基于SOPC的实时图像存储系统的设计

聂孟庆 余 愚

摘要:基于目前实时图像存储的解决方案研究的现状与发展趋势,本文研究了基于SOPC技术的实时图像存储设计方案。使用ALTERA公司的Nios II软核处理器作为总控制器,采用CCD传感器加ADV7181B视频解码芯片进行实时图像数据采集,SDRAM用来存放实时图像数据与程序,VGA控制器控制实时图像显示。

关键词:片上可编程系统;实时图像;视频解码;同步动态随机存储器

1引言

随着高速图像处理技术的应用领域不断扩大,对图像处理速度的要求也越来越高,当前基于软核处理器的图像处理系统成为研究的热点。微电子技术的迅猛发展为高速图像处理系统提供了硬件基础,其中内嵌软核处理器的现场可编程门阵列 (FPGA)满足了图像处理系统中对速度、集成度、可靠性的要求。FPGA的应用越来越广泛,大容量高速度的FPGA以及SOPC技术的出现,为图像采集和处理提供了一种新的解决方案,使用FPGA来构建基于片上可编程系统(SOPC)的图像处理系统,充分利用SOPC Builder中自带的各种IP核控制器,减少底层硬件的开发[1,2],已成为一种趋势。

2系统基本架构

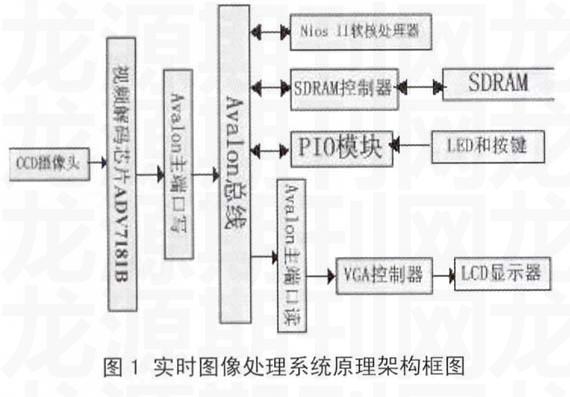

图1为基于SOPC的实时图像处理系统的基本架构,视频解码芯片ADV7181B首先对CCD摄像头

所采集的信号进行A/D转换,转换为YUV空间格式数据,然后再将YUV空间转换到RGB空间;FPGA通过I?C配置模块核对视频解码芯片ADV7181B进行参数配置, ADV7181B的时钟信号由一片27MHz的晶振提供,产生内部所需的27MHz的LLC(行锁定系统时钟)信号。通常使用二分频信号LLC2(13.5MHz)来同步整个图像采集系统,输出8位标准的ITU656 YUV4:2:2格式的数据;A/D转换后的数据通过SDRAM控制器存储到SDRAM中;VGA显示模块是用来将SDRAM中的视频数据通过VGA显示器实时显示出来。

3 视频解码芯片的I2C总线配置

为了控制总线上的设备,必须要遵守一个特定的协议(I2C总线协议)。I2C总线为同步传输总线,总线信号完全与时钟同步。I2C总线上与数据传输有关的信号有起始信号S、终止信号P、应答信号以及位传输信号。首先,I2C总线控制器发起一个数据传输的起始条件是:SCLK信号保持高电平,而SDA信号由高电平变为低电平。这意味着一个地址或者数据流传输已经开始。外围设备都监视着SCLK和SDA信号并等待着起始条件及正确的地址。起始条件满足后,就会送出一个8位的设备地址,所有的外围设备开始相应起始条件并转换下一个8位寄存器地址(7位地址+1位读写位)。在发送时由高位到低位依次传输。外围设备识别出传输地址后作出反应,在第九个时钟脉冲把数据线变为低电平,这被视为一个确认位。此时其他所有设备退出总线并使总线保持闲置状态,设备监视SCLK和SDA,等待起始条件并等待争取的传输地址的时刻即为闲置状态。接下来开始将8位数据写入或者读出寄存器,读写位决定了数据的传输方向。当时钟线SCLK为高电平,而数据线SDA由低电平变为高电平时,表示一次数据传输完成,停止I2C总线,等待下一次的传输开始。图2为I2C总线的数据传输时序图[4]。

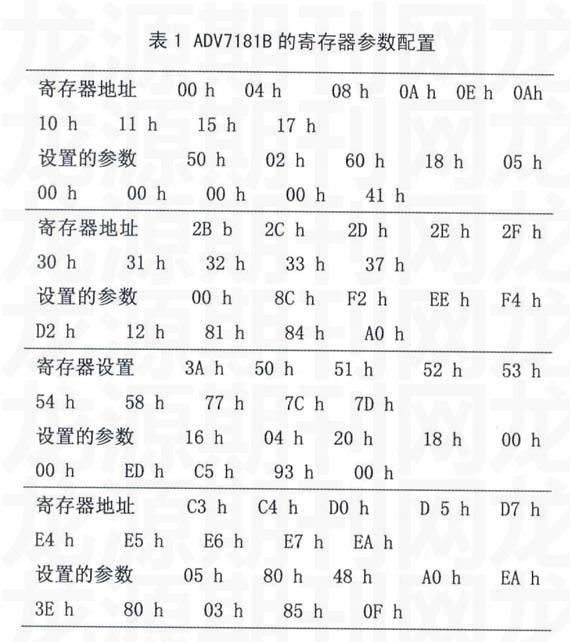

ADV7181B内部共有240个控制寄存器,可通过配置这些控制寄存器来设定和实现ADV7181B的各种功能。由于ADV7181B输出8位ITU656 YUV4:2:2格式的数字视频信号,在此要求下,只要对ADV7181B的40个寄存器的内容进行配置即可,这40个寄存器的地址和配置数据如表1所示。

配置数据存储在查找表LUT_DATA中,LUT-DATA为16位,包括了ADV7181B的寄存器地址和寄存器数据,配置时逐个写入寄存器的值,寄存器索引代码为LTU_INDEX。每个寄存器配置分三步,使用mSetup-ST来表示当前进行到哪一步。第一步准备数据,将8位从设备地址与存储在LTU_DATA中的寄存器地址合并为24位数据,并将mI2C_GO设置为1,启动I2C传输;第二步检测传输结束信号,如果检测到传输结束(此时mI2C_END=1),但ACK信号不正常,重新发送数据;如果检测到传输结束且ACK信号正常,则进入第三步,将寄存器索引加1,准备下一次数据的传输。

在SOPC Builder自带的IP核库中并没有I?C配置模块IP核,此模块是根据ADV7181B芯片的寄存器特点以及功能要求自行设计,并以IP核的形式通过Avalon总线链接到SOPC系统上。

4视频解码

CCD摄像头采集到的数据经过视频解码芯片进行A/D转换后,输出8位YUV 4:2:2格式视频数据流,然后经过视频解码模块将其转换为ITU656标准的视频数据流,这些信号包括8位的视频图像数据,行同步信号,场同步信号以及行参考信号。PAL制式下,每秒扫描25帧,每帧包含奇偶两场图像。每帧图像含有625行数据,其中有效图像数据576行,奇偶场各288行,23~311行是偶场视频数据,336~624行是奇场视频数据,每行图像数据包含720个像素,故标准的数字化PAL制式电视标准分辨率为720*576。在27MHz时钟频率下,意味着每秒27MB的数据速率:(13.5*8+6.75*8*2)Mbit/s=27MB/s=625*25*1728,即每行有1728字节的数据,其传输顺序为:CbYCrYCbYCrY………,需要指出的是CbYCr指的是对同一个地址进行的亮度和色差采样,接下来的Y对应下一个亮度采样。

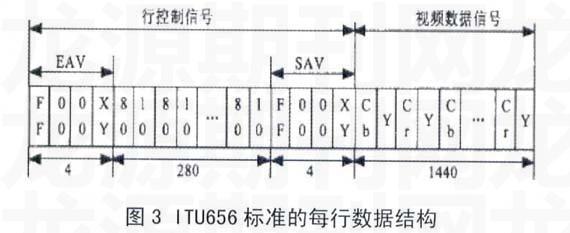

图3为ITU656标准的每行数据结构,每行数据包含水平控制信号和YCbCr视频数据信号。每行开始的288字节为行控制信号,开始的4字节为EAV信号(有效视频结束),紧接着是280个固定填充数据,最后是4字节的SAV (有效视频起始) 信号。SAV和EAV信号有3字节的前导:FF、FF、00;最后1字节XY表示该行位于整个数据帧的位置及如何判定SAV、EAV[5]。由SDRAM的工作特性可知,只在每个时钟周期的上升沿读取视频解码芯片传过来的视频数据。当侦测到连续三个字节为FF0000时,可知SAV或EAV的到来,接着判断第四个字节的第四位,如果为0即表示有效数据的开始,此时启动行列计数器,开始对接下来的图像数据进行解码,然后根据每个8位数据自身的信息,得到Y、Cb和Cr分量的值。

5SDRAM存储器设计

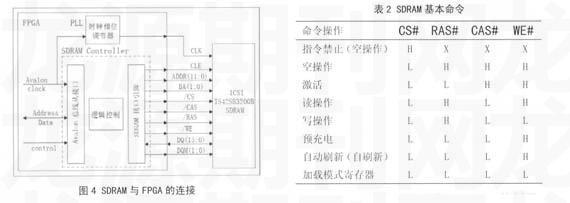

因为实时图像处理系统要进行大批量的高速图像数据采集,对数据的速度要求比较高,而且数据量比较大,在此采用ICSI公司的数据宽度为8位、存储容量为32MB的 IS42S83200B SDRAM来存储数据,它与FPGA的连接关系如图4所示[1]。

经过视频解码后输出8位的ITU656 YUV4:2:2格式的视频数据,由于SDRAM位宽同样为8位,因此可以将亮度信号Y和色差信号Cb与Cr分别单独存储到一个地址空间中,相当于一个采样周期产生一个SDRAM地址。另外,由于VGA的显示分辨率为640*480,则必须要提取出适合VGA的分辨率的图像。从PAL制式有效分辨率中提取出640*576有效分辨率图像数据存储到SDRAM地址空间中,然后从中读取480行送给VGA控制器即可。

5.1 SDRAM控制器的设计

SDRAM是同步动态随机存储器,同步是指与系统时钟同步,从而避免了不必要的等待周期,减少数据存储的延迟时间。动态是指为了提高存储容量,SDRAM芯片采用硅片电容存储信息,但是必须要不断地给电容充电才能保持数据信息不丢失。SDRAM的主要信号有控制信号(CS片选信号,CKE时钟使能信号,DQM输入输出使能信号,CAS、RAS、WE读写控制命令字),地址信号(BA0和BA1页地址选择信号,A0~A12地址信号,行列地址选择信号),数据信号(DQ0~DQ15双向数据)。这些信号均为系统时钟同步输入、输出信号。上电后,SDRAM控制器必须对SDRAM进行初始化操作,然后SDRAM进入正常工作状态,等待控制器进一步的读写和刷新操作指令。SDRAM的所有的操作都是在指令的引导下进行的,基本命令如表2所示。

具有Avalon接口的SDRAM控制器IP核包含在SOPC Builder中,它为片外SDRAM提供一个Avalon从接口,可以比较方便的在FPGA中定制一个与SDRAM芯片连接的系统。SDRAM控制器IP核可以根据实际使用的SDRAM芯片进行相应的配置[3]。

5.2隔行扫描转换为逐行扫描

由于PAL制电视信号是隔行扫描, 将一帧图像分为奇数场和偶数场分别扫描,数字化以后格式仍然不变,而VGA采用的是逐行扫描方式。因此,在将数据存储到SDRAM以前,还需要将奇数场和偶数场的数据再还原成一幅完整的图像,将隔行扫描变为逐行扫描。具体实现过程为:设计一个行计数器,在进行奇数场数据采集时,从0开始计数,每次加2,计数值依次为0,2,4,…,572,574;当进行偶数场数据采集时,从1开始计数,每次加2,计数值依次为1,3,5,…,573,575,该计数器实际上就相当于SDRAM地址发生器。当VGA控制器从SDRAM中读取数据时,只需按顺序读取地址读取出所需的480行即可,这样读取出来的数据就是一帧完整的适合VGA显示的图像。

6VGA显示

VGA控制器IP核集成在SOPC Builder中,可以根据系统具体情况进行定制。VGA控制器发出读有效信号到SDRAM中,SDRAM将视频数据传给MUX,通过转换模块将YUV4:2:2格式的视频数据流转换为YUV4:4:4格式的视频数据,使得每个像素都包含完整的亮度分量Y、色度分量Cb和Cr,然后将YUV4:4:4格式的视频数据通过YCbCr-RGB模块由 YUV空间转换到RGB空间,再将RGB空间数据传送给VGA控制器,VGA控制器同时产生VGA的行场同步信号VGA_HS和VGA_VS会同24位RGB数据一起传送到视频编码芯片VGA DAC7123中,最后通过显示器将图像实时显示出来[6]。

7结束语

本文重点介绍了基于SOPC技术实时图像的数据存储。系统各模块主要使用了SOPC Builder自带的IP核进行定制,由于IP核具有非常灵活的可定制特性和可移植特性,使得工作重心转移到系统设计方面,而不再是各模块编写方面,改变了传统的设计思路。本系统的实现是基于DE2-70多媒体开发实验板,经过验证,该方案充分保证了各模块之间的协调性与并行性,较好的实现了实时图像数据处理所要求的实时性、高速性,另外也充分体现了SOPC系统的高集成度、低功耗以及灵活高效的特点。在本系统基础上,可以进一步展开模式识别、运动目标检测以及视频图像压缩等方面的研究。

参考文献

[1] 李兰英等.Nios II嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[2] 侯建军,郭勇.SOPC技术基础教程[M].北京:清华大学出版社,北京交通大学出版社,2008.

[3] 王诚,吴继华等.Altera FPGA/CPLD设计(基础篇&高级篇)[M].北京:人民邮电出版社,2005.

[4] Multiformat SDTV Video Decoder ADV7181B datasheet[Z].Analog Devices Ltd,2004.

[5] 祝长峰,肖铁军. 基于FPGA的视频图像采集系统的设计[J].计算机工程与设计,2008,29(17):4404~4407.

[6]DE2-70 User Manual Version 1.01[Z]. Terasic Technologies Ltd,2007.

作者简介

聂孟庆,硕士研究生,主要研究方向为计算机视觉与模式识别;

余愚,教授,主要研究方向计算机视觉与智能控制。