基于电流折叠技术的CMOS全差分VCO设计

康香英 徐卫林

摘 要:针对目前通信系统应用上对压控振荡器的片上集成、宽调谐、调幅、启动特性和功耗等提出的综合性要求,分析和设计了一种压控调频调幅振荡器,其延迟单元采用全差分结构,以消除共模噪声和增加延迟控制的灵活性;并利用交叉耦合的差分负阻和电流折叠的正反馈技术进行频率调谐,使之在宽频范围内具有常数振荡幅度。采用0.5 μm CMOS工艺进行Spice仿真,结果表明振荡器具有34~197 MHz的宽调谐范围,并能保持常数振荡幅度,功耗仅10 mW,启动时间仅52 ns。系统还能在0.5~2.0 V范围内进行良好的线性调幅。

关键词:电流折叠;负阻交叉耦合晶体管对;自动振幅控制;全差分压控振荡器

中图分类号:TN402文献标识码:B

文章编号:1004-373X(2009)10-011-02

Design of CMOS Full Differential VCO Based on Current Fold Technique

KANG Xiangying1,XU Weilin2

(1.Xianggang Yixing Refractory Co.Ltd.,Xiangtan,411102,China;

2.Institute of Microelectronics and Information Technology,Wuhan University,Wuhan,430072,China)

Abstract:On-chip VCO with comprehensive target,such as wide tuning,amplitude adjusting,good start up time and lower power,is required in current communication system.A frequency and amplitude adjusting VCO is designed and analyzed.Full differential configuration is used to avoid common mode noise and achieve controlling flexibility of delay cells.Negative resistance differential complementary cross-coupled pair and regenerative feedback technique with current fold are applied to adjust frequency with constant amplitude in large range.Under 0.5 μm CMOS process,Simulation results in SPICE indicate that the VCO proposed behaves in wide linear tuning between 34~197 MHz with constant amplitude,10 mW power dissipation and 52 ns start up time.It also has good linear amplitude adjusting between 0.5~2.0 V.

Keywords:current fold;negative resistance complementary cross-coupled pair;automatic amplitude control;fully differential VCO

射频振荡器是仪器仪表、自动控制和通信系统等领域广泛使用的基本模块,是构成时钟恢复、频率合成等系统的核心电路[1,2]。通常用无源元件LC,隧道二极管、双基极二极管(单结晶体管)、雪崩双极型晶体管来设计,但它们都与标准的CMOS工艺不兼容[3]。虽然LC振荡器有良好的稳定性和相位噪声性能,振荡频率可达微波L带至C带,但调谐范围不大,而且不易于在当前主流CMOS工艺下进行片上集成。因而采用电流折叠的正反馈技术设计了一个全差分CMOS环形压控振荡器(VCO)。该振荡器在调谐时具有常数振荡幅度,并具有良好的线性调频调幅性能。

1 振荡器的工作原理及其全差分实现

1.1 振荡器的工作原理

振荡器是一种不需要外部信号激励,能够将自身的直流能源转换为周期性输出信号的电路。振荡条件由式(1)Barkhausen准则决定[4,5]。

|T(ω)|≥1,∠T(ω)=360°(1)

可见系统能够产生振荡的基本条件是环路增益T(ω)>1,环路相移为360°。大部分应用要求振荡器是可调谐的,理想压控振荡器的控制函数如式(2)所示。

ωout=ωo+KvcoVcont(2)

式中:ωo是对应控制电压Vcont=0时的振荡频率;Kvco为VCO的增益或者灵敏度。环形振荡器的工作原理:使得环路传输函数仅在一个频率点上满足Barkhausen准则,从而对延迟单元的设计提出了较高的要求。

1.2 振荡器的全差分实现

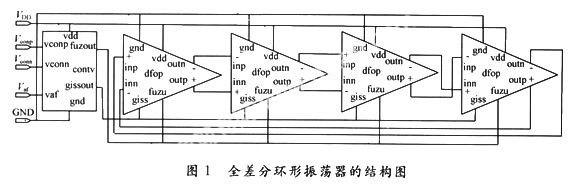

延迟单元的结构和数量应根据对振荡器速度、功率、噪声性能等要求进行选择。鉴于单端延迟单元的延迟时间容易受到电源电压噪声和衬底耦合噪声的干扰,采用全差分结构,可以在较大程度上抑制这类共模噪声[2,6,7],如图1所示。

图1的第一个模块是调频调幅控制单元,主电路采用4级全差分延迟单元,所以前三级采用反相连接,最后一级采用同相连接,以满足Barkhausen准则。而且避免了单端反相延迟单元不能采用偶数级数的缺点。控制单元送出两个控制电压控制延迟单元的尾电流MOS管栅源电压,从而实现频率和幅度调节。

2 电路设计

2.1 采用电流折叠的正反馈延迟单元

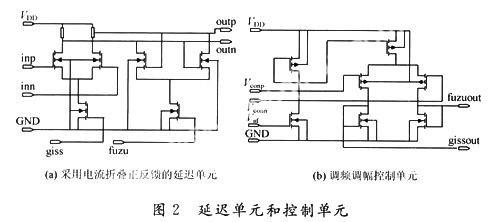

基于上述考虑,采用全差分单元来实现信号延迟,延迟时间决定于时间常数RC,若直接调节负载电阻进行频率调谐,伴随的是振荡信号幅度随频率的变化而变化。一种解决的方法是采用复制偏置技术,它同时调节负载电阻和尾电流的大小,使振荡信号幅度近似不变。缺点是需要增加一个运算放大器,且其带宽必须大于频率变化的带宽,这样增加了芯片面积和设计难度[8,9]。采用的是电流折叠正反馈延迟单元,它不需要使用运算放大器[10],如图2 (a)所示。

这里在差分对的基础上并入交叉耦合对,容易证明,该耦合对的小信号等效阻抗为-2/gm的负阻。只要这个负阻绝对值大于负载电阻,则差分对的负载电阻仍是正阻抗,而该正阻抗可通过调节交叉耦合对的偏置电流来改变其阻值,从而改变延迟,但会导致负载电阻上的最大电流发生变化。因此在调谐方案的设计上采用差分电压控制,同步向相反方向调节差分对尾电流,这样两个尾电流之和是一个常数,从而实现了频率调谐时的常数振荡幅度。控制上采用电流折叠结构,折叠到调频调幅控制单元,由该单元实现尾电流的同步调节。

2.2 调频调幅控制单元电路

调频调幅控制单元的作用是提供频率调谐功能,并保证调谐时的常数振荡幅度。如图2(b)所示,固定基准电流时,通过PMOS镜像的镜像电流也保持恒定,从而使得外部差分压控信号输入后,控制单元的差分对管电流发生变化,但总电流保持恒定,并利用栅漏短接的NMOS将这一电流转换为控制电压,从而保持了延迟单元调谐时的常数振荡幅度。鉴于振荡器应用的广泛性和差异需求,同时振荡幅度的增加可以提高相位噪声,因此这一控制单元设计上的优点还在于可以通过调节幅度控制输入端来调节振荡信号的幅度。

3 系统仿真

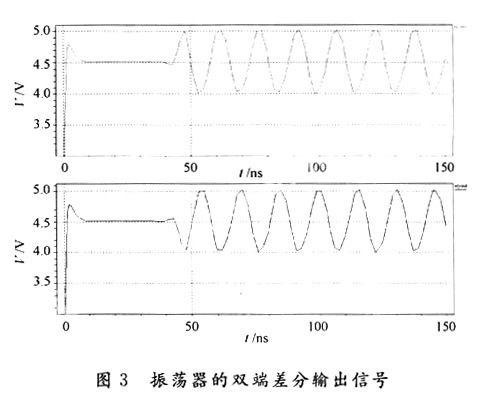

对整个系统在TANNER环境下利用Tspice工具和0.5 μm CMOS工艺库进行仿真。图3是2.5 V幅度控制电压和1.0 V差动电压下差分振荡输出信号。仿真结果表明,起振时间仅52 ns,输出信号摆幅1.0 V,振荡频率66.25 MHz,功耗仅10 mW。

通常环振频率调谐范围在3倍以内[3],仿真表明振荡器在差分控制电压-1.6~+1.6 V范围内和2.5 V幅度控制电压下具有163 MHz约6倍(34~197 MHz)的宽调谐范围,并具有1.0 V的常数振荡幅度,幅度偏差小于50 mV,如图4(a)所示。保持差分调频控制电压、调幅控制电压和振荡信号的幅度具有图4(b)所示的压控调幅曲线。表明在2.0~4.0 V调幅控制电压下,具有较好的线性调幅特性,可在0.5 ~2.0 V之间线性调幅。

4 结 语

设计的基于电流折叠的全差分压控调频调幅振荡器在0.5 μm CMOS工艺下的Spice仿真结果表明,振荡器具有较大的频率调谐范围和调幅范围;压控频率调谐增益和压控调幅增益的线性度都较好;电路功耗较低,仅10 mW;不需要电感和电容元件,便于CMOS工艺下的片上集成,并极大地减小了芯片面积。

参考文献

[1]张冠百.锁相与频率合成[M].北京:电子工业出版社,1995.

[2] [日]远坂俊昭.锁相环(PLL)电路设计与应用[M].何希才,译.北京:科学出版社,2006.

[3]池保勇,余志平,石秉学.CMOS射频集成电路分析与设计[M].北京:清华大学出版社,2006.

[4]Lee T H.The Design of CMOS Radio Frequency Integrated Circuit[M].UK:Cambridge University Press,1998.

[5]Fong N,Plouchart J.Design of Wideband CMOS VCO for Multiband Wireless LAN Applications[J].IEEE,Solid-State Circuits,2003,38(8):1 333-1 342.

[6]Hajimir A,Lee T H.Design Issues in CMOS Differential LC Oscillator[J].IEEE JSSC,1999,34(5):717-724.

[7]Kim B,Ko J S,Lee K.A New Linearization Technique for MOSFET RF Amplifier Using Multiple Gated Transistors[J].IEEE Microw.Guided Wave Lett.,2000,10(9):371-373.

[8]Gil J,Song S S.A 119.2 dBc/Hz at 1 MHz,1.5 mW,Fully Integrated,2.5 GHz,CMOS VCO Using Helical Inductors[J].IEEE Microw.Wireless Compon.Lett.,2003,13(11):457-459.

[9]Chuang Y H,Lee S H.A Low-voltage Quadrature CMOS VCO Based on Voltage-voltage Feedback Topology[J].IEEE Microw.Wireless Compon.Lett.,2006,16(12):696-698.

[10]Razavi B.A Study of Phase Noise in CMOS Oscillators[J].IEEE JSSC,1996,31:331-343.