中频数字接收机的工程实现

王红彦,刘 泳,姜晓洁

(山东航天电子技术研究所预研 1室,山东烟台 264003)

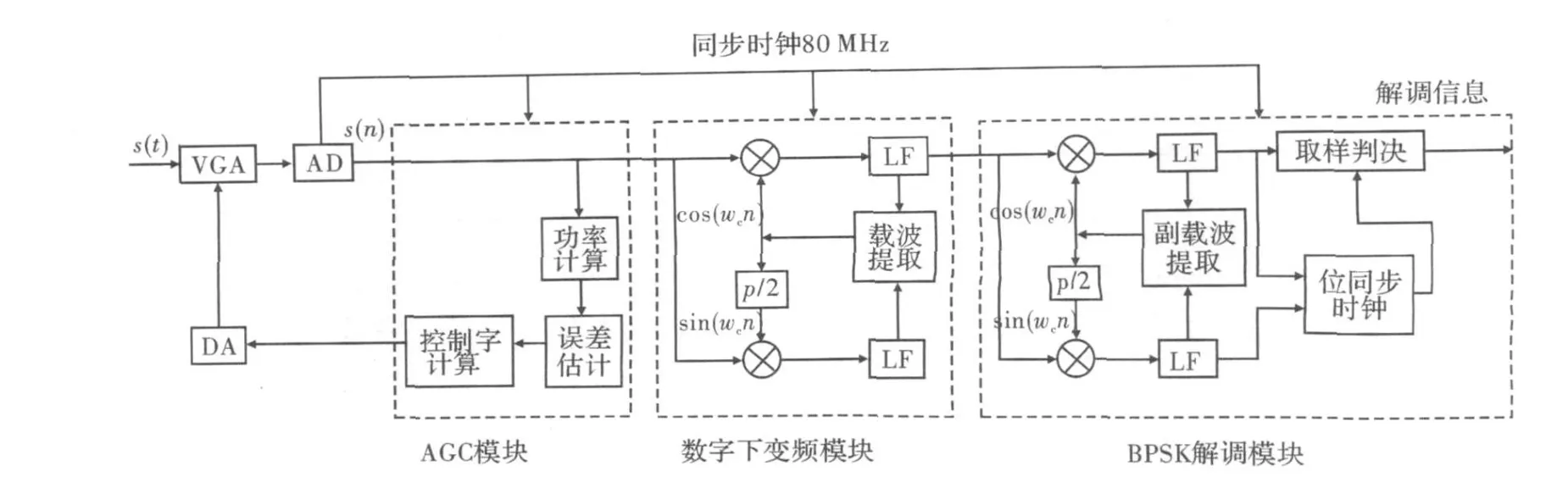

1 结构设计

接收机采用了软件无线电[1]设计思想,对输入信号在中频直接进行带通采样。输入信号频率为70 MHz,调制格式为 PCM/BPSK/PM。接收机的整体结构,如图 1所示,其工作流程如下:输入信号首先经过前端 AGC电路输出稳定幅度,然后通过带通滤波器滤除带外噪声,再经 A/D采样转换为数字信号,最后进入信号处理单元 FPGA,完成 AGC增益控制算法、数字下变频和 BPSK信号解调。PCI总线对接收机供电并与计算机进行信息交互。

图1 接收机结构

2 采样率选择

中频输入信号的载波频率为 70 MHz,但是需要处理的信号带宽只有 3MHz。对于这样的信号,采用带通采样的方法,不仅可以降低采样率,还可完成信号频谱下搬移。根据带通采样定理[2]

式中,fs为带通采样率;fH为带通信号高端边界频率;fL为带通信号低端边界频率;B为信号带宽。当选取信号带宽为 16 MHz时,经计算,采样频率有 3个区间:39 MHz≤fs≤ 41.33 MHz,52 MHz≤fs≤62 MHz和 78MHz≤fs≤124 MHz。实际设计时,综合考虑 A/D变换器性能价格、前端抗混叠滤波器的实现难易以及 FPGA的处理速度等因素,采样率设定为80 MHz,采样后信号频谱被搬到 10 MHz附近。

3 硬件选择

3.1 AGC电路

AGC电路主要由可控增益放大器 VGA和 D/A转换器构成。VGA芯片选用 AD公司的 AD8367。AD8367具有 45 dB控制范围,输入信号从低频到500 MHz内增益均随控制电压以 dB为单位线性变化。模式控制管脚 MODE决定控制增益随控制电压变化的关系:当 MODE接高时,增益随外加控制电压Vgain增大而增大,当 MODE接低时,增益随外加控制电压 Vgain增大而减小。实际设计时采用两片AD8367级联以扩展 AGC的动态范围。

VGA控制电压由 D/A转换器提供,选用 LINEAR公司的 LTC1458L,LTC1458L为 12位串行输入数模转换器,满幅输出电压为 2.5 V,最小量化电平LSB=2.5/(212-1)=0.61mV。

3.2 模拟带通滤波器

模拟带通滤波器选用国产 7MB61-70/U16型 LC带通滤波器,其中心频率为 70MHz,带宽为16MHz。通带内插入损耗最大值为 -1.634 dB,常规值为-1.193 dB。

3.3 A/D变换器

A/D变换器选用 TI公司的 ADS5500高性能模数转换器。ADS5500是一款低功耗、采样率为 125MSPS的 14位流水线模数转换器,模拟输入部分采用差分输入,所以在 A/D前端用变压器 ADT1-1WT将单级信号转换成差分信号,CLKOUT引脚随采样数据输出同步时钟。

3.4 FPGA

由于中频采样后数字信号全部在 FPGA内部处理,数据量大,而且信息速率比较高,因此 FPGA需要具有较高的资源。本设计选用 Altera公司的 StratixⅡ系列器件 EP2S60F672C,具有 60440个逻辑单元,最高工作频率可达到 550 MHz,可以满足系统的要求。

3.5 PCI总线

PCI总线是一种采用 32/64位传输的局部总线,使用了独立于 CPU的 33 MHz/66 MHz时钟,峰值传输速率为 132/264MB◦p-1,适合高速数据传输的要求[4]。本设计中 PCI总线工作时钟为 33 MHz,接口芯片选用 PCI9054,工作于 C模式。控制芯片用于控制 PCI9054的时序逻辑,选用 Altera公司的MAX3000A系列器件 EPM3128。

4 下位机软件设计

下位机软件的编写全部在 FPGA内部完成,采用硬件描述语言 VHDL和 Verilog编写各个程序模块,主要包括 AGC模块、数字下变频模块和 BPSK解调模块。其中数字下变频模块与解调模块都用到了Costas环:第一级环路用于提取载波,第二级环路用于提取副载波。整个设计流程如图 2所示,ADS5500的同步输出时钟 80 MHz作为整个系统工作的时钟。

图2 下位机软件流程图

4.1 AGC模块

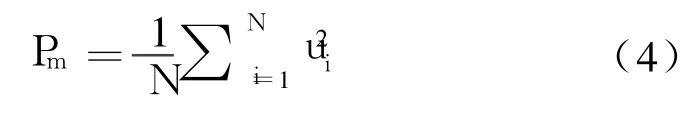

AGC模块根据输入信号的平均功率来实现增益控制,A/D采样后的信号平均功率 Pm可写成

其中,N为样本累加数;Pm为模拟输出信号平均功率;ui为 A/D输出的样本值;A/D采样的是经过增益调整的信号。平均功率的计算如图 3所示,N取2n,n为正整数,对累加寄存器右移 n位即是平均功率值。

图3 平均功率计算框图

增益控制字计算的方法是:与参考的平均功率值作比较,小于或超过参考功率,就分别增大或减小控制字,每次增大或减小固定的变化量,经过一定时间的调整,输入的平均功率会在参考功率左右变化。实际设计时,由于信号的瞬间变化不会太大,为保证控制精度,参考功率取一个窄带区间,当实际功率小于区间的下限时,调整控制字以增大 VGA输出增益;当实际功率大于区间上限时,调整控制字以减小VGA输出增益。控制字每次调整一位,则 D/A输出电压每次变化 0.61 mV,对应 VGA输出增益每次变化 0.61×0.05=0.030 5 dB。

4.2 数字下变频

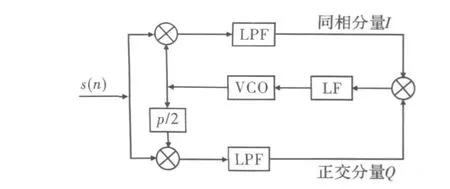

在进行数字下变频模块设计时,考虑到接收端与发射端之间存在频率和相位偏移,所以采用了 Costas环在提取相干载波的同时完成下变频功能。Costas环的结构,如图 4所示。

图4 Costas环结构

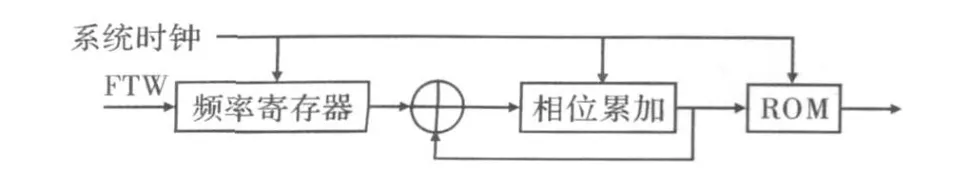

实际设计时,用数字频率合成器 DDS代替 VCO向两支路提供正交载波,DDS由频率控制字寄存器、相位累加器和 ROM表构成,如图 5所示。

图5 DDS结构

输出频率为 fnco=FTW×fclk/2N,其中 FTW是频率控制字,N是频率控制字字长,fclk是系统时钟频率。本设计中频率控制字长 N取 32,FTW=232×10 MHz/80 MHz=536 870 912。

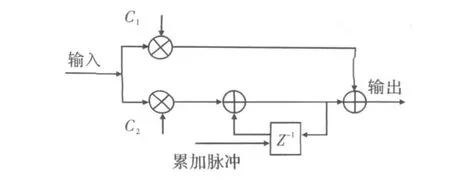

低通滤波器 LPF采用积分清零滤波器,通过分段累加实现低通滤波的功能。环路滤波器 LF采用图 6所示的结构,环路中两个重要参数 C1和 C2的推导过程参见文献[5]。

图6 环路滤波器结构

4.3 BPSK解调

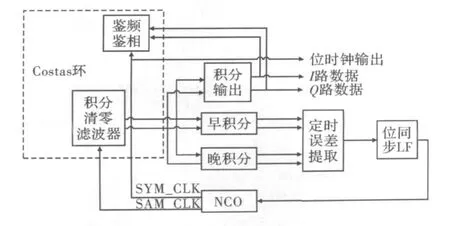

BPSK解调模块与数字下变频模块类似,此时Costas对副载波进行提取,DDS产生相干副载波。位同步时钟的提取选用早迟门位同步法。位同步环与Costas环相关,Costas环中积分清零滤波器的清零速率为 4倍的码元速率,受位同步 NCO输出时钟控制,位同步环分别取积分清零滤波器输出的前两项和后两项作早迟判决,计算出相位差值,并用该相位差值控制位同步 NCO的频率控制字,位同步环的结构,如图 7所示。

图7 位同步环结构

完成副载波恢复、位同步时钟提取之后,对同步积分信号进行取样判决,最终输出解调数据。

5 上位机软件

对下位机软件进行调试时,需要修改很多参数。每个参数修改后都需进行重编译,由于工程较大,编译一次往往需要用很长时间。为此,设计中利用上位机软件通过 PCI板卡对外部 RAM的写操作来配置下位机中的参数:将下位机中的参数在 RAM中分配特定的地址,修改时将参数值写入其对应的地址就可以了。下位机中的几个关键参数,比如码速率、副载波速率、频率控制字、环路滤波器参数 C1和 C2等,都可以通过上位机软件进行修改。图 8给出了设计中使用的一个典型上位机软件界面。

图8 上位机软件界面

6 仿真与测试

下面给出数字下变频模块和 BPSK解调模块的仿真和部分测试结果。图 9为Matlab仿真图,其中发送码元为 0 0 0 1 1 0 1 0,码速率 1 kHz,副载波速率8 kHz,载频为 10 MHz。

可以看出,信号经下变频后,同相 I路输出BPSK信号;在解调部分,BPSK信号与副载波相乘后,同相 I路数据极性与码元符号一致,所以将 I路数据分段累加取符号位,最后作码型变换即可得到解调数据。

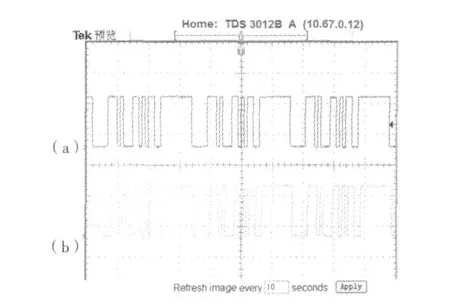

实际测试时,发射机产生频率为 70 MHz、原始数据为 1ACFFC1D循环序列、码速率 1 kHz,副载波速率 8 kHz、调相指数为 0.6的PCM/BPSK/PM信号,用 QuartusⅡ 8.0软件中的 SignalTap和示波器分别观察数字下变频和解调后的信号。图 10显示的是在SignalTap中观察到的数字下变频后的信号波形,其中 fir_i_d为同相分量 I,fir_q_d为正交分量 Q。图 11显示在示波器中观察到的发送数据与解调后的数据波形,其中图 11(a)为发送数据,图 11(b)为解调数据。

图10 下变频后 I,Q信号波形

图11 发送数据与解调数据

从 SignalTap中可以看出,数字下变频后同相支路的输出信号波形与仿真结果是一致的,表明数字下变频模块可以正常工作;而示波器则更直观地显示出发送数据与解调数据,通过对比,说明接收机可以正确解调信号。

7 结束语

经过联调测试,接收机各功能模块工作正常,AGC电路可以在 0~-60 dBm的动态范围内实现增益控制;在输入码速率 1~32 kHz,副载波速率 8~128 kHz信号的情况下,解调输出误码率低于 10-6,满足系统设计要求,接收机目前已成功应用于某地面测控设备。

本文设计的接收机结构简单,性能优良,PCI总线结构设计可以使接收机完成数据的高速实时处理,通过对 FPGA加载不同的软件,还可以实现对其他系统的中频接收,具有较强的通用性。

[1]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[2]殷瑞,万国龙.数字信号处理[M].北京:清华大学出版社,2007.

[3]田耘,徐文波,张延伟.无线通信FPGA设计[M].北京:电子工业出版社,2007.

[4]王晗中,吴利民.基于PCI总线的软件无线电中频数字接收机设计[J].无线电工程,2005,35(6):69-72.

[5]张厥盛.锁相技术[M].西安:西安电子科技大学出版社,1991.