基于FPGA+DDS的信号源设计与实现

刘 伟,钟子发,叶春逢

(电子工程学院,安徽 合肥 230037)

目前,大多通信设备都是针对某一种或少量几种固定的通信体制、信号调制样式以及信号特征参数,例如GSM移动通信信号只有GMSK一种调制样式,其调制速率为22.8 Kbit/s,因此这类通信设备中的数字信号激励器或数字波形形成电路大多采用专用集成芯片实现。而本文设计了一个通用的数字信号激励器,以产生所需要的各种信号调制模式的信号波形,且对每一种调制样式信号的各种特征参数能够灵活控制。

1 数学模型

为了保证高性能以及灵活性,现代通信对抗干扰设备通常采用FPGA+DAC的工作模式,在一些快速复杂的应用环境下,则可采用高性能的FPGA和DSP协同工作,作为数字干扰激励器的核心,同时为保证对跳频信号或其他快速通信信号的有效干扰,频综模块通常采用DDS的频率快速合成模式。其干扰信号产生原理[1]可以由式(1)表示:

其中 sI(t)、sQ(t)分别为基带模拟干扰信号,ωc为 DDS+PLL频综生成的载波角频率。

在FPGA中利用数字方式合成数字激励源,通过一定形式的低通滤波器或脉冲成型滤波器即可得到数字基带信号 sI(n)、sQ(n)。数字基带信号 sI(n)、sQ(n)通过 DAC变换为模拟基带信号sI(t)、sQ(t),再通过上变频模块即可实现干扰信号的上变频调制。在 FPGA中,cos(ωn)、sin(ωn)可由查找表(LUT)的方式生成,即DDS频率合成方式。在现代FPGA开发中,通常会提供一些较成熟的IP核,因此也可以直接调用IP核来实现在FPGA中正弦信号的产生,其原理也是通过查找表的方式生成。在产生正弦信号时,查找表即为一个ROM块,通常其中存储了一个周期的正弦信号,通过对读取地址按一定步进循环取值即可产生相应的正弦信号。查找表的存储深度和FPGA的工作时钟决定了可以产生的正弦信号频率范围[2]。

(1)单音信号

单音信号可以按式(2)产生:

其中,sI(t)=cos(ωt)、sQ(t)=sin(ωt)分别为 I、Q 路基带模拟信号,当ω=0时,I、Q路基带模拟信号退化为直流,此时,干扰信号即为信号载波。FPGA产生的数字基带信号cos(ωn)、sin(ωn)经 DAC 变换即为模拟基带信号 cos(ωt)、sin(ωt)。

(2)多音信号

多音信号可以在单音信号的基础上直接生成。一种简单的方法是使用多个查找表同时生成,这种方式控制逻辑简单,但相对占用更多的FPGA资源。另一种方法是使用一个查找表采用时分复用的方式生成,这种方式可以节省大量的FPGA资源,但控制逻辑相对复杂。

在产生多音信号时,需要注意合成信号的峰值,当各单音分量峰值同相叠加时就可能产生很高的信号峰值。因此可以通过控制各个单音分量的初始相位,来减小这种极高峰值的产生,即减小信号的峰均比。

(3)幅度调制信号

幅度调制信号可以按(3)式产生:

其中,sI(t)=mI(t)、sQ(t)=mQ(t)分别为 I、Q 路基带模拟信号。当mI(t)=mQ(t)=m(t)且无直流分量时,则可得到无载波分量的双边带(DSB)调制信号,m(t)为基带模拟信号;当mI(t)=mQ(t)=m(t)且有直流分量时,则可得到有载波分量的双边带调制信号,此时m(t)可以表示为m(t)=m0+m′(t),其中,m0是基带信号 m(t)的直流分量,m′(t)为交流分量,如果满足 m0>max(|m′(t)|),则可得到调幅(AM)信号。

(4)角度调制信号

角度调制信号可以按式(4)产生:

(5)数字调制信号

数字调制信号可以按式(5)产生:

其基带信号表示为:

当s(n)按不同的星座映射方式便可得到不同的数字基带调制信号,如:PSK、QAM信号等。为了降低带外信号,通常对发射信号使用一定形式的脉冲波型,如升余弦波型等。因此,在FPGA中数字基带激励输出后通常使用脉冲成型滤波器。

调频类:M进制的调频信号MFSK,码元ak电平定义为:ak={0,1,2,…,M-1},一个码元符号的 FSK信号即可表示为:

其中,Δf为相邻码元的载波频率偏移。对于MFSK信号,利用M个载频的正弦波数据,按照(7)式即可很容易获得合成波形数据。

调幅类:M进制的调幅信号MASK,码元ak电平定义为:ak={0,1,2,…,M-1},一个码元符号的 FSK信号即可表示为:

对于MASK信号,利用M个振幅的正弦波数据,按照(8)式即可很容易获得合成波形数据。

调相类:

·QPSK:一个符号间隔内的载波初始相位只可能是4 个(±45°、±225°)之一,一个符号内合成波形数据为:

·幅相联合调制 (16 QAM):一个符号间隔内的载波初始相位只可能是12个之一,幅度为3种之一,一个符号内合成波形数据为:

2 子模块设计

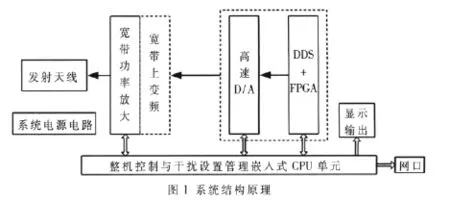

设计采用如图1所示的技术方案,它由全向/定向天线及馈线、20 W宽带功率放大模块、宽带上变频模块、基于DDS+FPGA和高速DAC的数字信号激励模块、整机控制与嵌入式CPU单元模块等部分硬件和一套信号产生与控制软件组成。

2.1 电源与主板模块

220 V的交流电通过电源管理模块转换到+5 V、-5 V、+12 V和+28 V分别为基带激励板、变频模块和功放模块提供相应的直流电输入。由设备的便携式需求牵引,本设计基于嵌入式PC104 CPU和宽温液晶显示屏为硬件控制平台并外接160 G硬盘,提供设备所需的鼠标、键盘、网口、USB、RS-232等接口,操作系统为 WindowsXP,编程环境为 Visual C++,通过软件编程实现各种样式信号的数字激励与波形形成,界面友好,操作简便灵活,所有参数和功能均可通过界面窗口和控制按钮实现输入和控制。

2.2 基带激励板

本设计采用DDS+FPGA+DAC数字信号激励器硬件电路和数字波形合成软件算法来生成所需要的各种信号,具体方案详见基带激励板电路设计。

2.3 变频模块

主要包括频综模块、上变频模块,基带信号首先实现单载波(CW)、 调幅(AM)、 调频(FM)、 调相(PM)等调 制样式,然后进入晶振+DDS+PLL[5]模块实现混频,产生输入到功放模块的信号。本设计要求输出信号和干扰频率范围为30 MHz~1 000 MHz,达33.3个倍频程,因此要解决宽带上变频[3]这一关键技术。为了实现信号源频率和特征参数的快速改变,采用减少PLL环路、加大中频瞬时带宽直接变频的方法提高换频速度。设计中采用在80 MHz的中频上进行宽带波形合成,然后再进行变频的方案,将80 MHz±5 MHz的中频信号变频至 30 MHz~1 000 MHz范围。对于调制信号的特征参数控制,采用了高速接口芯片进行并行控制的方式。

2.4 功放模块

宽带功率放大这一关键技术的设计采用三级放大的方案,混频输出信号经各分段滤波器滤除带外信号,进入功放模块实现功率放大,然后接天线输出至空间。为了提高功率输出效率,系统根据频段划分,采用伞状天线和对数周期天线两付输出天线相结合。其中,伞状天线的工作范围为30 MHz~500 MHz,对数周期天线的工作范围为 500 MHz~1 000 MHz。

3 基带激励板电路设计

本设备主要由数字基带激励板控制,FPGA为核心,所有操作都是在它的控制之下展开的;其次就是一些外围电路,包括电源配置、接口配置等;再有连接激励板与调制模块的数模转换及其滤波电路,为后续处理模块提供感兴趣的频带范围内的模拟信号。

3.1 晶振和电源管理

利用晶振来产生高稳时钟,通过FPGA内部锁相、分频来实时控制电路的时序,本设计采用15.36 MHz和20 MHz的晶振。根据供电方案,需要将+5 V直流输入电源转换为+1.5 V和+3.3 V,分别供给FPGA的内核和I/O口,选用TPS54613和TPS54615芯片并匹配外围电路来实现电源的转换,并通过磁珠加电容的发放,构成滤波电路来优化电源。

3.2 FPGA模块

FPGA产生 I、Q两路基带数字信号,DAC主要完成数模转换,生成I、Q两路基带模拟输出信号。同时FPGA完成对DDS+PLL的频综控制,实现对基带信号的上变频。通过Verilog HDL编程和调用IP核[5]来实现对RS-232串口、JTAG接口、变频模块和功放模块的时序逻辑控制。基带激励板通过RS-232串口与CPU互联,实现控制指令的传输;通过DB25与变频模块互联,控制DDS的状态;通过DB15与功放模块互联,实现射频波段的选择;变频模块与功放模块通过DB9互联,传输所选择的波段控制信息。

3.3 DAC与滤波电路

基带产生的数字信号需要经过数模转换和滤波电路,然后经由调制、混频和功放模块发射至空间。设计中选用DAC2904和LT6600芯片,根据手册配置外围电路,最终激励板经两个差分对输出I+、I-、Q+、Q-4路信号[4],然后送入调制模块实现各种调制样式。具体的电路原理图如图 2、图 3所示。

3.4 整机

利用 Altium Designer软件进行原理图的设计[6],然后生成PCB图,经过综合考虑后手动布局、布线,最后生成数字基带应用印制电路板。各个模块设计完成、调试通过后,整机组装并进行功能、指标测试,通过频谱仪、功率计检测,证明该设备完全能够满足实际应用的需求。

图3 滤波电路

本文设计并工程实现了综合测试宽带信号源,实验时利用频谱仪测试,信号的各种调制样式完全符合指标要求,同时通过外接天线测试,利用接收机能够检测到各种调制信号。实践证明该设备能够实现大功率宽带综合信号源、无线电监测训练电磁环境模拟源、无线电测向训练电磁环境模拟源、无线电管制(干扰)辐射源等功用。

[1]向新.软件无线电原理与技术[M].西安:西安电子科技大学出版社,2008.

[2]王诚.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2008.

[3]冯钟晋.10 MHz-3 GHz宽带高性能信号源的研制[D].西安:西安电子科技大学,2008.

[4]韩剑,李德明,冯雪.基于CPLD的 DDS正交信号源的设计[J].电子设计工程,2009,17(7):71-72.

[5]林静宜.基于DDS的多模式信号发生器的设计与实现[D].武汉:华中科技大学,2008.

[6]夏宇闻.Verilog HDL数字系统设计教程[M].北京:北京航空航天大学出版,2003.

[7]徐向民.Altium Designer快速入门[M].北京:北京航空航天大学出版,2008.