DM642和CPLD外部中断的寄存器式键盘设计

贺玺,杨述斌

(武汉工程大学 电气信息学院,武汉 430074)

贺玺(硕士研究生),主要研究方向为DSP、信号与图像处理;杨述斌(教授),主要研究方向为信号、图像处理与多媒体通信。

引 言

键盘是人机交互模块中必备的输入部分,在目前的嵌入式系统人机接口中通常采用专用的键盘处理芯片ZLG7290设计键盘[1-3]。由于ZLG7290是一种64位LED显示和64个按键的键盘管理器件,会造成部分LED显示和按键空闲浪费并占用硬件资源比较多,使成本增加。随着DM642性价比的提高,它在图像处理系统和数字媒体系统中的应用越来越广泛,而作为人机交互重要手段的键盘在上述系统中是必不可少的输入设备。通常以DM642为核心的电路系统中主要采用独立式键盘和行列扫描式键盘[4-5]。本文在DM642电路系统中使用CPLD提供多路输入/输出引脚的方法扩展键盘。DM642的外部中断监控按键的状态,CPLD管理键盘电路中的芯片逻辑。此外,CPLD(EPM7128AET芯片)共有100个输入/输出引脚,可根据实际需要自由扩展引脚,实现灵活,应用前景广阔。

1 独立式键盘和行列扫描式键盘

1.1 独立式键盘

独立式键盘是指将每个按键按一对一的方式直接连接到I/O输入线上所构成的键盘。独立式键盘可以工作在多种方式下:中断方式、程序查询方式、定时查询发送和中断查询方式。独立式键盘的缺点是需要占用较多的I/O线。当应用系统中需要的按键比较少或I/O线比较富余时,可以把单个按键与DSP的输入/输出引脚直连,采用查询或中断方式检测键值。电路如图1所示,S1~Sn表示n个按键,按键的输入端接地,输出端与DSP的输入/输出引脚P1~Pn相连,并接上拉电阻。DSP可以采用查询方式检测键值,也可以采用中断方式监控按键的状态。

图1 独立式键盘

1.2 行列扫描式键盘

行列扫描式键盘是行列式键盘中最主要的一种,是用n条I/O线作为行线,m条I/O线作为列线组成的键盘。在行线和列线的每一个交叉点上,设置一个按键。这样,键盘中按键的个数是m×n个。它适合于构成按键数目比较多的键盘。这种形式的键盘结构,能够有效地提高系统中I/O口的利用率。行列扫描式是先使列(行)线全输出低电平,然后判断行(列)线状态,若行线全为高电平表示无键被按下,若行线不全为高电平表示有键被按下。然后依次使列线为低电平,再判断行线状态,当行线全为高电平时表示被按下的键不在本列,当行线不全为高电平时表示被按下的键在本列,把此时的行线状态与列线状态和在一起即为被按下的键的位置。扫描法对键的识别采用逐行(列)扫描的方法获得键的位置,当被按下的键在最后一行时需要扫描N次(N为行数),当N比较大时键盘工作速度较慢。如图2所示,该键盘为16键行列扫描式键盘,具有4路输入引脚 Pi1~Pi4和4路输出引脚Po1~Po4配合使用。当DSP工作于查询方式时,按键不需要加上拉或下拉电阻。

图2 行列扫描式键盘

2 外部中断的寄存器式键盘

2.1 系统总体结构

键盘系统中CPLD选用EPM7128AET芯片,能提供多路输入/输出引脚,输出逻辑电平为3.3V,输入逻辑电平兼容3.3V和 5V两种,共100个输入/输出引脚。CPLD在逻辑控制和时序控制方面具有很多优势,它的内部拥有大量的逻辑门,可以在软件环境中巧妙地利用这些门电路,对输入引脚信号进行各种逻辑组合设计,将逻辑组合信号再提供给输出引脚。CPLD器件内部还提供了大量标准的逻辑电路模块,如译码电路、地址锁存电路等,这些电路模块代替了传统电路中需要的译码芯片、地址锁存芯片等,不仅为电路板设计节省空间,而且使电路设计流程更加灵活和方便。DSP选用TMS320DM642芯片,为了扩展 DM642的 GPIO输入/输出引脚而设计成16按键的键盘,CPLD需使用DM642的低8位数据总线D[7:0]、地址总线EA[10:3]、EA22和读写控制信号线,CPLD才能在内部产生所需的扩展寄存器。CPLD丰富的输入/输出引脚和大量的逻辑门管理键盘系统中的芯片逻辑。如图3所示,按键的16个输入端接地,输出端KEY[1:16]与CPLD芯片的输入引脚I[1:16]连接,输出端接上拉电阻,DM642的低8位数据总线D[7:0]、地址总线EA[10:3]及EA22与CPLD器件的输入/输出引脚I/O[1:18]连接,DM642的RE和WE信号是寄存器扩展用的读/写使能信号,空间片选信号CE1和地址信号EA22作为寄存器端口片选信号,把按键状态读端口映射到DM642的CE1空间。当有按键按下时,产生一个上升沿脉冲触发信号,该信号可以认为是一个外部中断事件,那么可以通过DM642的外部中断EXINT4响应该中断事件,而在DM642内部EXINT4可以映射为中断INT4,DM642在INT4对应的中断函数中通过数据地址总线读取按键的键值并进行分析。在程序层面,该按键的触发信号和程序中INT4的中断服务函数相对应,同时INT4的中断服务函数与中断向量表中的中断编号联系起来。

CPLD芯片内部扩展按键状态的16位输入端口控制寄存器逻辑图如图4所示,DM642通过操作寄存器读端口实现读取按键的键值并进行分析。在图4中,DM642的空间片选信号CE1和地址信号EA22作为寄存器端口片选信号,当CE1信号低电平有效时,与键盘状态有关的寄存器地址被映射到CE1空间,地址线EA22在映射关系中低电平有效。CE1空间地址有效范围为0x90000000~0x9FFFFFFF,按键KEY1~KEY8的寄存器端口地址为0x90080019,KEY9~KEY16的寄存器端口地址为0x9008001A。KEYCS[2:1]为输入端口的片选信号线,两路输入片选信号分别对应I[1:8]和I[9:16]输入引脚。芯片74138是CPLD内部提供的一种译码器,芯片74373是CPLD内部提供的一种地址锁存器,用于锁存按键按下时的电平状态。

图3 键盘硬件电路图

图4 CPLD内部的扩展寄存器

这里将扩展的寄存器端口地址设置为PORTAdd,PORTAdd在CE1空间中拥有一个32位的端口地址,PORTAdd[31:0]与DM642的CE1信号和EA[22:3]地址信号之间的定义关系如表1所列。CE1信号决定了PORTAdd31位,EA[22:3]地址信号决定了寄存器端口地址的PORTAdd[19:0]位,PORTAdd端口的其他位保留未用。根据表1中的映射关系就可以确定CPLD内部寄存器端口的物理地址。在图4中,CE1信号保持低电平、EA22信号保持高电平时选中74138_1芯片,则PORTAdd的第31位和第19位均应为高电平“1”;EA8~EA6为高位译码地址线,EA5~EA3为低位译码地址线,两片74138芯片配合使用,能够产生64路片选信号;片选信号KEYCS1和KEYCS2低电平有效,两片74373在DM642的CE1空间中的地址分别为0x90080019和0x9008001A。

表1 CE1空间端口地址与地址线的映射关系

3 软件设计

在CCS编程环境中,编写 main.c、boot.asm、ves_dm642.asm、key.cmd等文件,由于在CSL中包含 boot.asm函数,所以只需要自行编写main.c和ves_dm642.asm、key.cmd三个文件,然后添加到所创建的Key.pjt项目中。

ves_dm642.asm是DM642的中断向量表文件,声明中断函数名称及与中断编号的映射关系,KeyIsr是INT4对应的按键中断响应函数,其主要代码如下:

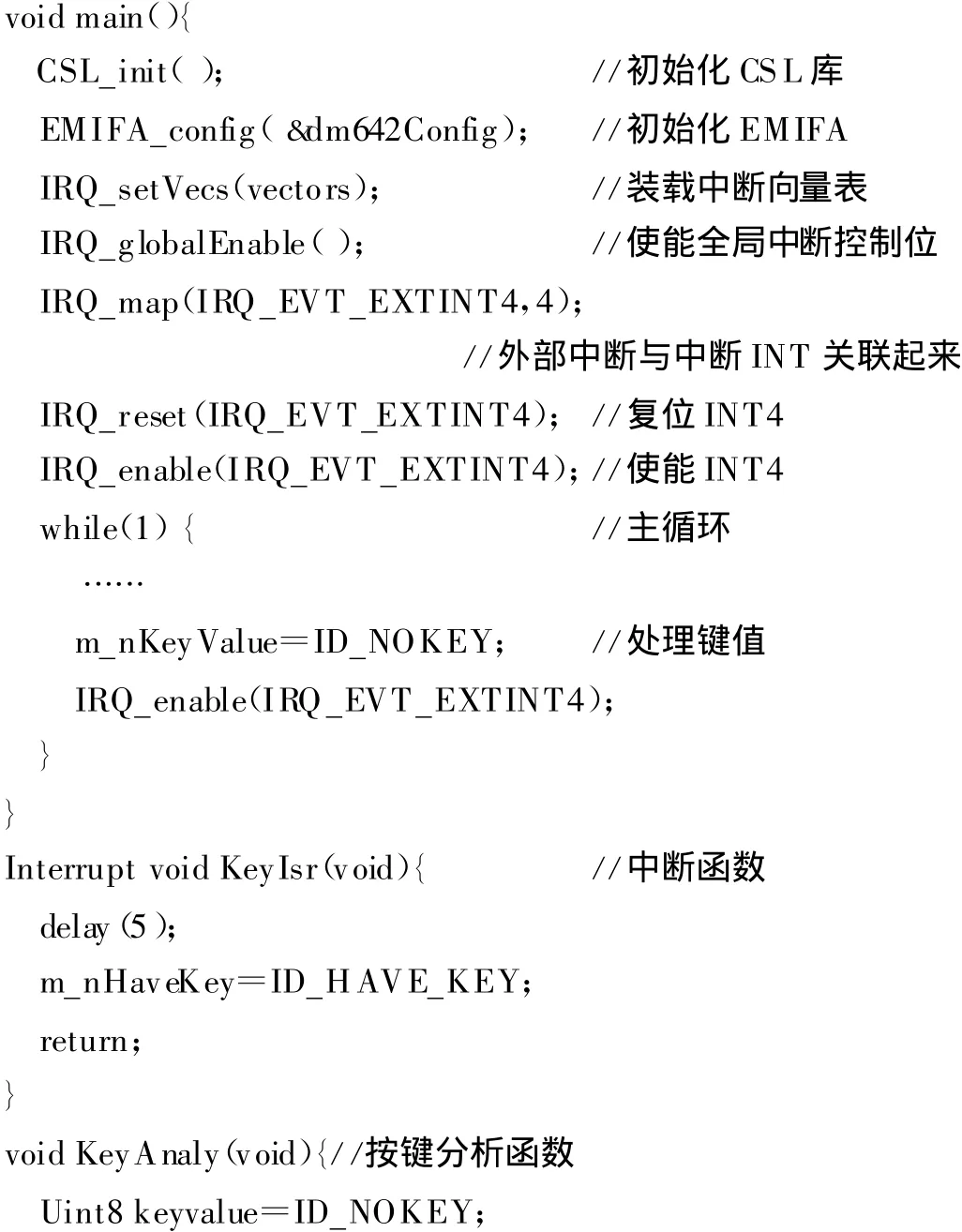

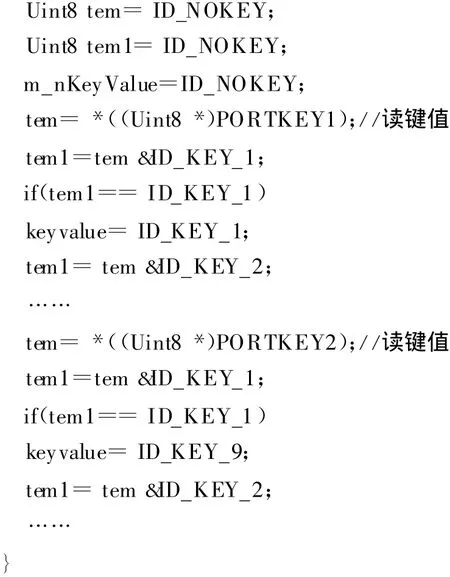

main.c是键盘电路的主程序,包括添加CSL库文件的头文件、定义按键状态寄存器的端口地址及按键的MASK、初始化设置EMIFA接口、按键分析函数。主要代码如下:

4 系统调试

为了调试程序,需要把 main.c、boot.asm、ves_dm642.asm、key.cmd文件添加到项目Key.pjt中。同时,需要设置Build Options中的Compiler和Linker属性页,最后编译、链接、下载。通过设置断点和探针来进行软件模拟调试。CCS仿真表明,程序能根据硬件设计的要求读取按键的键值并进行按键状态的分析,达到预期结果。

结 语

DM642和CPLD相配合的方法扩展键盘,DM642的外部中断监控按键的状态,CPLD管理键盘电路中的芯片逻辑。充分利用DM642的GPIO口引脚能够配置为通用输入/输出引脚的优势和CPLD丰富的输入/输出引脚特性。可以应用在以DM642为核心处理器的模式识别和图像处理系统的人机交互模块中,前景广阔。

[1]刘燕,黄晓革.键盘扩展设备ZLG7290在Linux系统中的驱动设计[J].科技创新导报,2008(1-b):16-17.

[2]范赛华,高美凤,朱建鸿.键盘扩展设备ZLG7290在 μC/OS-II操作系统中的驱动设计[J].科学技术与工程,2009,9(7):1934-1937.

[3]王雅辉,迟学芬,祝宇鸿,等.嵌入式多媒体通信终端中文字交互功能的实现[J].吉林大学学报:信息科学版,2009,27(1):56-61.

[4]张跃飞,李树山.基于DSP的智能断路器主控制器的键盘硬件设计[J].电气开关,2008(5):32-34.

[5]王跃宗,刘京会.TMS320DM642DSP应用系统设计与开发[M].北京:人民邮电出版社,2009.