基于ADF4156与ADF5001的微波本振源设计

单 菡

(江苏科技大学,镇江 212003)

0 引言

锁相(Phase Lock)技术是一种相位反馈频率控制技术,该技术在锁定时无剩余频差,并具有良好的窄带载波跟踪性能和带宽调制跟踪性能,而且对相位噪声和杂散也具有很好的抑制作用。因此,通过锁相频率合成技术实现的频率源已在通信、电视等领域得了广泛应用。本文介绍的基于ADF4156与ADF5001的微波本振源设计就是应用锁相技术结合RF预分频器实现微波本振源。

1 工作原理

本文所述微波本振源是由通过PLL频率合成器(包含低噪声数字鉴频鉴相器(PFD)、精密电荷泵和可编程参考分频器组成)、环路滤波器,压控振荡器、RF外部预分频器和高稳定度参考时钟五部分形成锁相环电路来实现的,其原理框图如图1所示。

图1 锁相环原理框图

频率合成器在锁相环(PLL)中工作,鉴频鉴相器(PFD)将反馈频率与参考时钟基准频率的某一分频形式相比较。PFD的输出电流脉冲经过滤波和积分,产生一个电压。此电压驱动一个外部电压控制振荡器(VCO)提高或降低频率,从而驱动PFD的平均输出接近零。

频率分频器分频,参考时钟分频器将基准参考输入时钟频率降至PFD频率(FPFD=FREF/R),反馈小数分频器(N)计数器和RF外部预分频器(P)降低输出频率,在PFD处与经过分频的基准参考时钟频率相比较,达到均衡时,这两个频率相等,则有(FOUT/P)/N= FREF/R,因此输出频率FOUT= (FREF/R)×P×N,小数N分频器内置一个Σ-Δ型小数插值器,能够实现可编程小数N分频。INT、FRAC和MOD寄存器可构成一个总N分频器(N = (INT+ (FRAC/MOD)))。因此当输出频率FOUT= (FREF/R)×P×(INT + (FRAC/MOD))时,锁相环电路达到琐相稳定状态。

2 器件介绍

ADF4156是一款6 GHz小数N分频频率合成器,它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和可编程参考分频器组成。该器件内置一个Σ-Δ型小数插值器,能够实现可编程小数N分频。INT、FRAC和MOD寄存器可构成一个总N分频器(N=(INT + (FRAC/MOD)))。RF输出相位可通过编程设置,适合要求输出与基准之间存在特定相位关系的应用。ADF4156还具有周跳减少电路,可进一步缩短锁定时间,而无需修改环路滤波器。

ADF5001预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18GHz的频率分频至适合输入到ADF4156 或 ADF4106等PLL IC的较低频率。ADF5001提供4分频功能,采用3.3V电源供电,具有差分100Ω RF输出,可以直接与ADF4156和ADF4106等PLL的差分RF输入接口。

3 电路设计与实现

本电路主要由五部分琐相环(PLL)频率合成芯片ADF4156、压控振荡器DXO11751220-5、RF外部预分频器ADF5001、高稳定度恒温晶体、环路滤波电路组成 (如图2所示)。以产生12GHz稳定微波本振源信号为例详细说明具体实施步骤。

3.1 器件选择

图2 微波本振源电路图

ADI公司的ADF4156小数N分频频率合成芯片,因其性能优异,使用灵活,被选为本设计锁相环电路实现的核心器件。由于设计要求产生12GHz稳定微波本振源信号,因此压控振荡器VCO的频率范围必须包含此频率,本电路选择了Synergy Microwave公司的微波VCO DXO11751220-5,频率范围为11750 ——12200MHz;PLL频率合成器的反馈输入射频频率一般不超过6GHz,因此在压控振荡器VCO到PLL频率合成器的反馈中必须加入RF外部预分频器以降低反馈输入射频频率,本设计中选用ADF5001固定4分频器;本设计选用压控振荡器VCO具有0.5V至15V的宽输入调谐范围,这要求在低电压ADF4156(电荷最大输出为5.5V)与VCO输入间采用有源PLL环路滤波器。OP184由于噪声性能佳,且具有轨到轨输入/输出,被选为该有源环路滤波器的运算放大器。参考基准时钟,选择中电集团13研究所的OX3系列高稳定度恒温晶体,本设计中选用100MH恒温晶体。

3.2 锁相环频率合成器参数设定

图3为琐相环频率合成器ADF4156原理框图。该频率合成器数字部分包括一个5位RF R计数器、一个12位RF N计数器、一个12位FRAC计数器和一个12位模数计数器。通过该器件提供的SPI接口对其内部5个32位移位寄存器写入数据,来实现各计数器的具体参数配置,详情参考ADF4156数据手册。

图3 ADF4156原理框图

本设计选用100MHz高稳定度恒温晶体作为参考时钟输入,要求产生12GHz的稳定微波本振源。如图3所示,由于ADF4156的N分频器的Σ-Δ电路存在速度限制,PFD工作频率不能超过32MHz,因此令鉴相频率FPFD为25MHz,而参考基准时钟为100MHz,需要对其进行内部4分频,由于ADF4156内部存在2分频器,因此只需将R寄存器值设置为2,即可实现参考基准时钟的4分频。根据锁相环原理器,当达到均衡时,鉴频鉴相器(PFD)两个输入端口频率相等,有(FOUT/P)/N=FREF/R=25MHz,(P在本例中为固定4,FOUT=12GHz),则可计算出N=120,根据器件数据手册要求,在低杂散模式下,MOD计数器最小容许值为50,设置MOD值为130(也可以设置为别的值,取决与设计要求的通道步进分辨率FPFD/MOD),INT、FRAC和MOD计数器可构成一个总N分频器(N = (INT + (FRAC/MOD))),而N=120,MOD=130,所以INT=120,FRAC=0。ADI公司提供的锁相环辅助设计工具ADISimPLL可以帮助实现PLL频率合成器各计数器值的参考设计,方便寄存器的配置。

3.3 环路滤波器设计

本设计选用压控振荡器VCO具有0.5V至15V的宽输入调谐范围,这要求在低电压ADF4156(电荷最大输出为5.5V)与VCO输入间采用有源PLL环路滤波器。实现这种结构的最简单方法是在无源环路滤波器之后添加一个增益级。运算放大器输出噪声将馈通至RF输出,并通过有源滤波器响应整形,因此噪声低。轨到轨输入操作也是PLL有源滤波器的重要考虑因素,因为可使用单运算放大器电源。这是因为电荷泵输出(CPOUT)在上电时将以0V启动,对不具有轨到轨输入电压范围的运算放大器可能造成问题。这也使得运算放大器的同相输入可偏置到高于地电压,且对电阻不匹配或温度变化引起的任何偏置电压变化内置余量。建议将偏置电平大约设置为电荷泵电源(VP)的一半,既满足输入电压范围要求又留有充足余量,并获得最佳的电荷泵杂散性能。本电路采用VP=5V进行测量,运算放大器共模偏置电压=2.2V。为了将基准噪声馈通降至最小,在同相运算放大器输入引脚附近放置1μF的大去耦电容,如图2所示。该电容和47kΩ的电阻形成截止频率低于10Hz的RC滤波器。

通常环路滤波器的设计带宽一般要低于为鉴相频率的1/10,绝对不能超过1/5,否则容易造成失锁,实际应用中为了更好的抑制带外噪声,设计时通常带宽要低于鉴相频率的1/10很多,本设计中鉴相频率FPFD=25MHz,设置环路滤波器的带宽为30KHz,相位,相位裕度为45度,使用ADI公司仿真辅助工具ADIsimPLLADI公司仿真辅助工具ADIsimPLL 工具进行仿真计算,得到环路滤波器的各参数如图2所示,最后根据实际电路做微调。

3.4 向锁相环频率合成器的寄存器写参数

可选用单片机、CPLD芯片或者FPGA芯片等等各种芯片向锁相环频率合成器的寄存器内写参数。锁相环频率合成器提供SPI接口,芯片的CLOCK、DATA、LE三个管脚负责接收外来数据,时序关系如图4(注意:在 ADI的 PLL 产品中,大多数datasheet中的SPI时序图有错误的,正确的应是如图4所示)。关于寄存器的描叙请参考ADF4216数据手册。

4 仿真结果分析

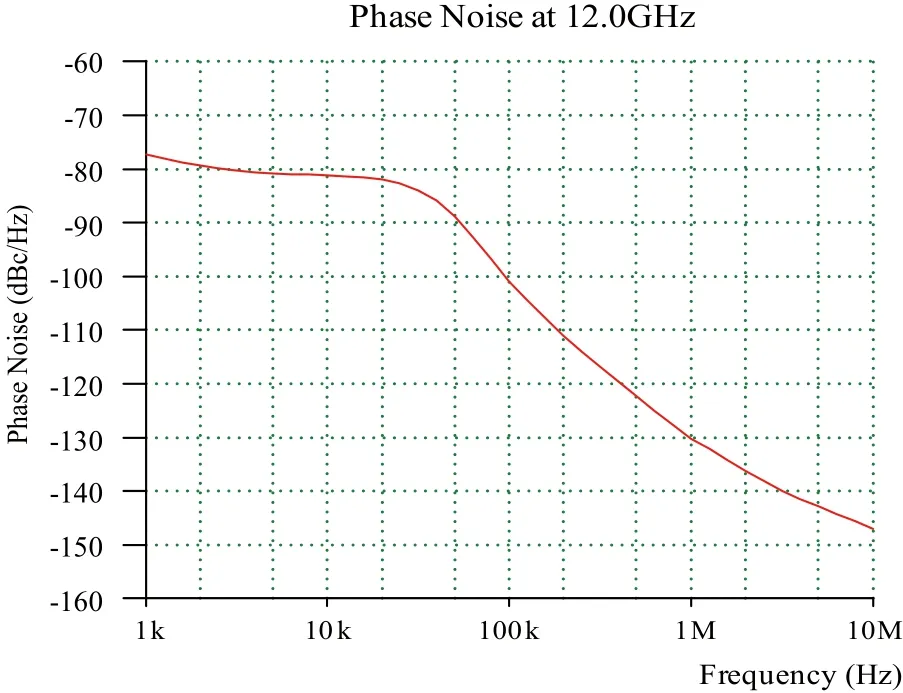

将上述所有参数输入到ADI公司仿真辅助工具ADIsimPLL中进行仿真分析,得到如图5所示噪声分析图。

由图5可见在12GHz@10KHz频偏相噪平均为-81.22dBc/Hz,基本满足指标要求。

5 结束语

采用该电路实现微波本振源,可以提供极低的抖动和出色的PSNR,可广泛应用于数据采集、无线基站、局域网(LAN)、宽带无线接入与测试设备、卫星通信、无线测量等领域。该电路简单,灵活可靠,只需编程修改内部寄存器参数,即可实现不同频率本振,实现一次设计,多种使用,具有很强推广性与可移植性。

图4 频率合成器SPI接口时序

图5 频偏相噪图

[1] 蒋涛, 唐宗熙, 张彪.S频段锁相频率合成器的设计[J].电讯技术, 2008, (08).

[2] 李彦舟.一种提高频率合成器鉴相频率的新方法[J].无线通信技术, 1989, (06).

[3] 郑春来.数字式双模锁相环频率合成器的设计[J].科技信息(学术版), 2006, (07).

[4] Analog Devices.ADF4156 datasheet [Z].2011.

[5] Analog Devices.ADF5001 datasheet [Z].2010.

[6] 阴亚东, 陈杰.BandⅢ锁相环型频率综合器的实现[J].半导体学报, 2008, (6): 1216-1222.

[7] 高吉祥.高频电子线路[M].北京: 电子工业出版社.2003.

[8] 池保勇, 余志平, 石秉学.CMOS射频集成电路分析与设计[M].北京: 清华大学出版社.2006.