基于USB的高清彩色CCD图像采集系统

黄以华,黄剑峰

(中山大学信息科学与技术学院 电子与通信工程系,广东 广州 510006)

随着时代的进步,科技的发展,数字图像的采集与处理在科技研究,工农业生产、医疗卫生、航空航天,军事对抗等领域得到了越来越广泛的应用。所以,对图像采集系统的研究具有重要的现实意义和应用价值。笔者提出了一种基于USB的彩色CCD高清图像采集系统。CCD中文名称为电荷耦合器件,它是20世纪70年代迅速发展起来的一种新型半导体探测器件,可把自然图像转换为电信号,具有动态范围大、电荷转移效率高、低噪声输出、分辨率高、工作频率高等优点[1]。USB即Universal Serial Bus,是通用串行总线的简称,这是由七家主要的计算机与电子科技大厂于1994年所研发和制定的一种串行总线协议[2]。本采集系统具有以下特点:数据传输采用USB2.0高速传输接口;整个系统由USB接口供电,无需外加额外的电源;系统可实现140万的高清图像采集;图像采集的速度最高达7.5 frame/s。

1 系统硬件设计

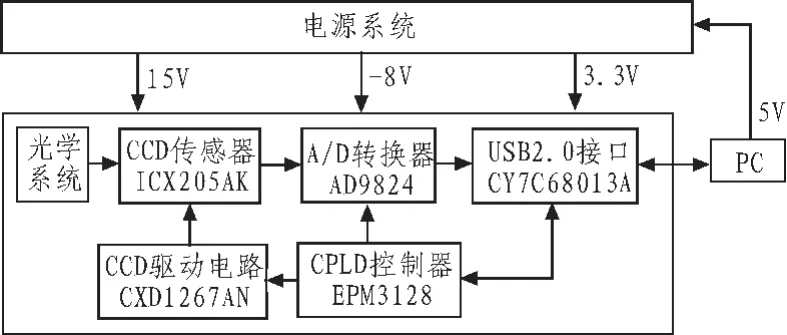

1.1 系统硬件架构

本系统的硬件架构如图1所示。整个系统由电源系统、光学系统、图像传感器,A/D转换器、CPLD控制器、USB2.0高速接口、上位机PC以及控制程序等各个部分组成。电源模块负责给整个系统供电,电源模块的输入是USB总线提供的5 V电源,进行DC-DC转换产生两路CCD驱动所需要的电源:15 V、-8 V。其他模块的供电采用统一的3.3 V。图像传感器采用的是SONY公司的 CCD ICX205AK,它是一款1/2英寸、145万有效像素的CCD传感器,每秒能够输出145万有效像素的图像7.5帧[3]。A/D转换器负责将CCD输出的模拟信号转变成为数字信号,采用的是ADI公司的AD9824,它是一款完善的CCD信号处理器[4]。CPLD控制器产生CCD和AD工作所需要的时序,同时须实时接收USB总线发送过来的控制信息,并根据接收到的参数实现图像的曝光时间和白平衡等调整。USB2.0高速接口是整个系统数据通信的“交通要道”,对系统中高速图像信号采集,上位机与硬件电路之间通信等方面起着至关重要的作用。本系统采用Cypress公司的USB2.0控制器 CY7C68013A,CY7C68013A芯片内部包含USB2.0收发器、串行接口引擎 (SIE)、增强型8051内核、16KB RAM、4KB FIFO存储器、I/O接口、数据总线、地址总线和通用可编程接口,硬件资源非常丰富[5]。根据系统的要求,并考虑到系统的成本,本系统采用Altera公司的MAX 3000A系列产品中封装为TQFP 100的EPM3128ATC100-10N芯片作为系统的控制中心。该芯片有2500个系统门,128个宏单元,最大支持80个用户I/O,且功耗低[6]。

图1 系统架构Fig.1 System structure diagram

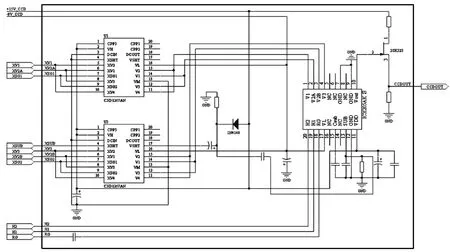

1.2 CCD驱动电路设计

图2为CCD驱动电路[3]。由于ICX205AK垂直移位寄存器不能直接使用TTL电平驱动,所以需要引入CCD驱动电路部分,对CPLD生成的各种转移脉冲信号进行功率放大,以满足CCD对驱动波形电压及电流以及时序的要求。驱动信号的好坏会对CCD的电荷转移效率产生较大的影响,从而影响成像的质量[7]。本设计采用的是与ICX205AK相配套的垂直时钟驱动芯片CXDl267AN,将原本为TTL电平的 V1,V2A,V2B,V3和SUB信号转变为合适的电平。其中V1,V3要求为-8 V/0 V两个等级,V2A,V2B要求为-8 V/0 V/+15 V 3个等级,SUB为-8 V/+15 V两个等级。引入XSG1,XSG2两个时序信号,用于控制CXD1267AN生成垂直移位时钟信号V2AV2B,实现感光阵列中的电荷信号转移到移位寄存器。H1,H2水平寄存器转移时钟,用于控制水平移位寄存器的电荷信号的顺序移出,其频率直接决定CCD信号输出的频率。

图2 CCD驱动电路Fig.2 Driver circuit of CCD

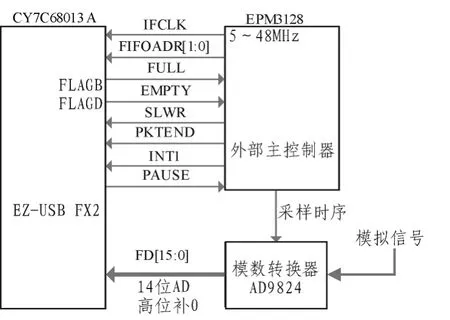

1.3 高速USB2.0接口设计

图3为高清图像采集系统的核心传输链路,USB2.0高速接口。因为图像采集系统要求将数据高速而准确地传入PC端,故本系统采用Slave FIFO模式,图像不经FX2LP的CPU处理,直接通过从属端点FIFO将数据高速传入PC端。

图3 高速USB2.0接口电路Fig.3 Interface circuit of USB

图3中,IFCLK为Slave FIFO的接口时钟。Slave FIFO接口时钟信号既可由内部提供,也可由外部提供。如果FX2LP设置为使用外部时钟源,则IFCLK引脚可被用来提供5~48 MHz之间的任何频率的时钟信号。当IFCLK被设置为输入时,最小频率为 5 MHz。 FIFOADR[1:0]引脚用来选择 EP2、EP4、EP6和EP8中的一个FIFO与数据总线FD连接。FULL和EMPTY引脚分别是FIFO的满状态和空状态标志,通过配置CY7C68013A内部的相关寄存器可使得当FIFO满状态或者空状态的时候向外部控制器发送相应的标志。SLWR引脚是写FIFO控制信号,当SLWR被激活时,数据总线FD上的数据在每个时钟信号IFCLK上升沿到来时被写入FIFO。

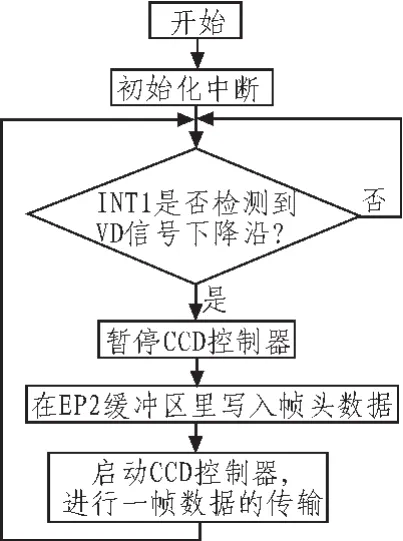

INT1和PAUSE信号是为了协调高清图像数据正常发送而引入的额外信号。系统中CCD图像传感器输出的模拟信号经AD9824采样后输出14 bit数字信号,但数据中不包含图像帧头信息。为使主机应用程序能够准确和完整地分离出图像数据,本系统设计方法是在EZ-USB FX2LP的INT1中断服务程序中为每一帧图像加入特定的帧头[8]。在EZ-USB在往FIFO里面写入帧头的过程中,不允许CPLD继续让AD向FIFO传送数据,从而引入了PAUSE信号通知CPLD暂停传送数据的操作。

本系统采用的模拟转换器AD9824是一款14bits的高效CCD信号处理器,而FD[15:0]是16位的数据总线,在设计过程中,我们将高位数据线接地,低14位数据线接AD9824数据并行输出数据。

2 系统软件实现

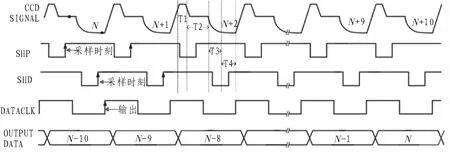

2.1 AD相关双采样

相关双采样(CDS)通过对每一个CCD像素点输出信号采样两次来消除低频噪声的影响,它是根据CCD输出信号和噪声信号的特点而设计。图4为相关双采样时序图,图中详细的指出了相关采样的时序要求。CCD每个像元的输出周期都以复位脉冲信号开始T1,先清除前一个像素的电荷,以等待下一像素电荷的到来。此时的输出信号被嵌入复位电平,并产生复位噪声;在图中T2期间,由于复位MOSFET漏电流的影响,复位电平有微小下降,这种现象称为复位失调电压。此时的输出信号为复位电平与复位噪声、复位失调电压的叠加;在T3期间,CCD电荷进行水平转移,此时混入移位时钟干扰;T4期间的输出为复位噪声、复位失调电压和有用光敏输出信号的叠加[1]。所以相关双采样的原理就是在T2和T4时刻对同一像素点的输出信号进行采样,然后将两次采样值相减就基本消除了复位噪声的干扰,得到信号电平的实际有效幅值。本系统选用的模数转换器AD9824内部具有相关双采样电路,系统实现过程中就是EPM3128产生如图4所示的SHP、SHP、DATACLK采样信号,即可完成相关双采样逻辑,很大程度降低了图像数据中包含的噪声信号。

图4 相关双采样时序图Fig.4 Double sample timing

2.2 USB固件程序设计

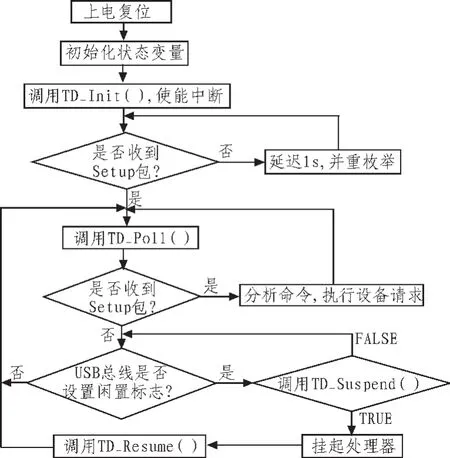

在USB接口设计中,USB固件编程是整个设计任务的核心。USB固件程序用于完成USB设备的识别、重列举、设备请求、USB协议处理、外部硬件的功能、负责与USB主机之间的数据通信等。固件的设计就是使在USB总线上的传输能获得最大的有效的数据传输速度。

设备上电之后,就会按照如下的步骤执行固件:

1)初始化架构全局变量;

2)调用 TD_Init()初始化 FX2LP芯片,调用用户自定义的初始化函数,返回后USB设置为未配置状态,并打开中断;

3)在紧接着的1秒内,重新枚举USB设备,直到收到SETUP封包;

4)检查设备请求,有请求则执行相应的功能,有的需要跳转到相应函数;

5)检查总线挂起事件,没有挂起事件则执行9);

6)调用 TD_Suspend(),返回失败代码则执行 9);

7)挂起处理器;

8)检查重新开始事件,事件发生则调用TD_Resume(),否则执行7);

9)调用 TD_Poll,函数返回到 4)并执行。

固件框架流程如图5所示。

图5 固件程序流程图Fig.5 Flow chart of firmware program

由于AD9824传送过来的每一帧图像都是连续的,也就是不包含帧头信息。本系统采取的做法是在一帧数据到来的时候,CPLD控制器会给CY7C68013A一个中断信号。中断服务程序所要做的工作就是清空FIFO里面的数据,并往FIFO里面写入512个字节的帧头(0xFF)数据。这样做的目的是保证上位机能够正确的识别每一帧数据。中断服务程序流程图如图6所示。

图6 中断程序工作流程Fig.6 Flow chart of interrupt program

2.3 上位机程序设计

本系统的上层应用程序使用VC++6.0软件进行编程,采用多线程、双缓冲区等技术实现动态图像的实时显示。

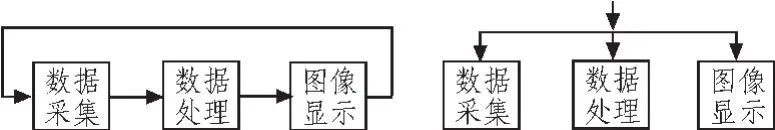

在图像采集系统中,主要有3个功能模块:图像数据采集模块、图像数据处理模块、图像显示模块。如果采用单线程方法,则工作过程为:先进行数据采集,采集完成后对数据进行处理,最后将处理后的数据进行显示。由于这3个功能模块不能同时进行,会造成了CPU的利用率低,限制传输帧速率的提高,导致系统的整体效率大大降低。

为了提高运行效率,本应用程序设计时采用多线程并行处理的方法,将数据采集、数据处理与图像显示分别放在3个线程里进行。从图7中可以很明显看出单线程与多线程的区别。

图7 单线程与多线程系统结构Fig.7 Single-threaded and multi-threaded architecture

在图像数据采集模块中,一种数据采集方法是串行处理[9],如图 8 所示。

图8 串行数据采集方法Fig.8 Serial data acquisition methods

这种结构易于实现,但存在着明显的不足:效率低下,不适合实时性要求高的场合。

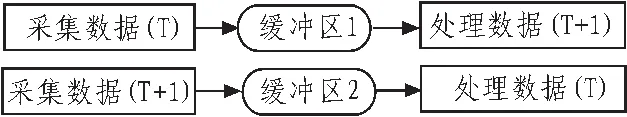

为了进一步提高图像采集的实时性,在应用程序开发时设计了双缓冲区交替采集处理[10]的工作方式,如图9。周期T时应用程序采集数据到缓冲区1,同时处理缓冲区2中的数据;周期T+1时应用程序采集数据到缓冲区2,同时处理缓冲区1中的数据。如此反复交替,可以显著提高数据采集效率。

图9 双缓冲交替采集方法Fig.9 Double buffering alternate acquisition method

系统测试结果表明,与普通的但缓冲区单线程结构相比,这种双缓冲区多线程结构可以显著提高图像传输的帧速率。

3 系统测试

通过USB2.0电缆将设备连接到装有Windows XP系统PC机上面,PC机上面运行采集软件进行图像采集。如果图像模糊不清,可以通过调节设备的镜头焦距,使得图像能够正确对焦。图10是整机调试的环境。图中采集到的图像数据为CCD的原始并未做处理的有效数据。图像的分辨率为1 360×1 024约等于140万像素。最快可以实现7.5 frams/s的采集速率。

图10 整机调试图Fig.10 Overall debugging Figure

4 结 论

本文设计了一个基于USB的彩色CCD图像采集系统,系统采用USB总线供电且能稳定工作,采集到140万的高清彩色图像,并最快能实现7.5 frame/s的动态图像采集。文章从硬件方面详细的叙述了整个系统的架构设计,CCD驱动电路的设计以及高速USB2.0接口的设计方案。软件方面阐述了AD相关双采样,USB固件程序的设计框架以及上位机多线程、双缓冲的设计思路。总之,本系统的设计方法对基于USB的图像采集系统的软硬件设计都具有重要的参考价值。

[1]佟首峰,阮锦,郝志航.CCD图像传感器降噪技术的研究[J].光学精密工程,2000,8(2):140-145.

TONG Shou-feng,RUAN Jin,HAO Zhi-hang.Noise reducing scheme on output signal of CCD[J].Optics and Precision Engineering,2000,8(2):140-145.

[2]周立功.PDIUSBD12 USB固件编程与驱动开发 [M].北京:北京航空航天大学出版社,2003.

[3]Diagonal 8 mm (Type 1/2)Progressive Scan CCD Image Sensor with Square Pixel for Color Cameras[Z]:ICX205AK.SONY Corpornation.

[4]Complete 14-Bit 30 MSPS CCD Signal Processor:AD9824[Z].Analog Devices, Inc.,2002.

[5]EZ-USB FX2LP USB Microcontroller:CY7C68013A[Z].Cypress Semiconductor Corporation,2006.

[6]MAX 3000A Programmable Logic Device Family[Z].Altera Corporation 2006.

[7]侯新梅,李自田,胡炳樑.基于FPGA的面阵CCD驱动电路的设计[J].现代电子技术,2010,7(318):195-197.

HOU Xin-mei,LI Zi-tian,HU Bing-liang.Design of driving time circuit for area array CCD based on FPGA[J].Modern Electronics Technique, 2010,7(318):195-197.

[8]孟浩,付继光,王中宇.基于EZ-USB FX2的CMOS图像采集系统设计与实现[J].仪器仪表学报,2007,28(4):332-335.

MENG Hao,FU Ji-hua,WANG Zhong-yu.Design and implementation of CMOS image acquisition system based on EZ-USB FX2[J].Chinese Journal of Scientific Instrument,2007,28(4):332-335.

[9]陈胡兴.多线程技术及其在数据采集中的应用[J].机械工程与自动化,2007(4):140-141.

CHEN Hu-xing.Multi-threads technology and its application in data acquisition[J].Mechanical Engineering&Automation,2007(4):140-141.

[10]刘晓冬,苏光大.一种基于中断的多线程高速图像采集系统[J].计算机工程与应用,2000,36(5):8-11.

LIU Xiao-dong,SU Guang-da.A high speed image capture system based on interrupt and Multi-Thread techniques[J].Computer Engineering and Applicatons,2000,36(5):8-11.