膈神经脉冲刺激仪的研制

钱明理 王 成

膈神经是颈丛中最重要的分支,其中的运动纤维支配膈肌。膈神经放电呈周期性,表现出特征性的高频振荡现象,频率为100次/s左右。神经断裂后即失去推动传导冲动的作用,一般认为神经细胞损坏后不能再生,而神经纤维在一定条件下是可以再生的[1]。雪旺细胞在神经再生中起着重要作用。损伤远侧雪旺细胞分裂增殖形成索带,对再生轴突起引导作用,并可诱导生长锥的迁移方向。雪旺细胞与靶器官还能分泌多种神经营养因子(neurotrophin,NT),如神经生长因子(nerve growth factor,NGF)等数十种多肽或蛋白类活性物质,营养、支持神经细胞的增殖代谢和调控轴突的再生与髓鞘的形成[4]。

电刺激能通过促进雪旺细胞和NGF的一系列活动而加速神经再生。雪旺细胞在生长及迁移时分泌大量的NGF,而电场使NGF受体向阴极移动,随即NGF聚集在远端并诱导轴突也向远端生长。目前,电刺激能促进神经再生已得到公认[5-6]。

研究表明, 模拟膈神经脉冲能有效地促进周围神经损伤后神经纤维再生,对周围神经损伤的治疗和康复有比普通的电刺激更好的疗效[2-3]。

生物刺激器在临床的应用较为广泛,如心脏起搏器对心脏起搏点的刺激;通过图像、声音等的刺激可用于观察脑电的变化;肌肉刺激器能用于观察肌肉的收缩情况等。本文所描述的膈神经刺激器目前在临床上还未得到应用,而且该领域涉足的人不多,可参考的文献资料极少,故该神经刺激器的研制是一个开拓的过程,值得尝试。

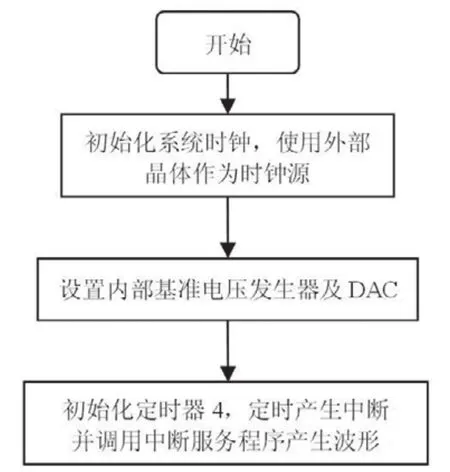

利用已采集到的膈神经模拟信号,设计一种程控电脉冲神经刺激器,可植入动物体内长久发放一个信号电脉冲,用以帮助受损的周围神经修复。本研究通过以下3个步骤来实现(如图1所示):

图1 步骤图

1 刺激器设计原理

美国Cygnal公司所设计的Cygnal C8051F系列单片机,其运行速度达到25 MIP/s。Cygnal C8051F系列单片机是集成的混合信号片上系统,具有与MCS-51内核及指令集完全兼容的微控制器,除了具有标准8051的数字外设部件之外,片内还集成了数据采集和控制系统中常用的模拟部件和其他数字外设及功能部件[7]。Cygnal C8051F系列单片机的功能部件包括模拟多路选择器、可编程增益放大器、ADC、DAC、电压比较器、电压基准、温度传感器、SMBus/I2C、UART、SPI、可编程计数器/定时器阵列(PCA)定时器、数字I/O端口、电源监视器、加密狗定时器(WDT)和时钟振荡器等。所有器件都有内置的FLASH存储器和256字节的内部RAM,其中FLASH存储器既可用作程序存储器又可用作于非易失性数据存储。应用程序可以使用MOVC和MOVX指令对FLASH进行读或改写。有些器件还可以访问外部数据存储器RAM,即XRAM(如图2所示)。

图2 C8051F020原理框图

1.1 主程序总体设计

利用C语言编程使C8051F020器件的片内数/模转换器(DAC)将已采集的数据表通过使用累加算法实现一个中断驱动的函数发生器,最终输出频率与幅度可调的模拟信号波形。根据要求,程序流程如图3所示:

图3 主程序流程图

1.2 部分程序设计

1.2.1 设置系统时钟

C8051F微控制器拥有高速CPI-51内核,系统时钟最大可达25 MHz,因此考虑使用外部的振荡源-22.1184 MHz的晶体(外部振荡源才能达到此较高的振荡频率,且有相当高的精度)[8]。当外部振荡器稳定运行时,晶体振荡器有效标志(OSCXCN寄存器中的XTLVLD)被硬件置‘1’。XTLVLD检测电路要求在允许振荡器工作和检测XTLVLD之间至少有1 ms的启动时间。在外部振荡器稳定之前就切换到外部振荡器可能导致不可预见的后果。因此,在设置系统时钟考虑其过程如下:①允许外部振荡器;②等待1 ms;③查询XTLVLD‘0’->‘1’;④切换到外部振荡器。

1.2.2 禁止加密狗定时器(WDT)

MCU内部有一个使用系统时钟的可编程加密狗定时器(WDT)。当加密狗定时器溢出时,WDT将强制CPU进入复位状态。根据实际需要,要求禁止WDT以防止意外产生的禁止操作。向WDTCN寄存器写入0×DE后再写入0×AD可禁止WDT,但注意:写0×DE和写0×AD必须发生在4个时钟周期之内,否则禁止操作将被忽略。

程序中与上述对应的源代码为:

1.2.3 设置内部基准电压发生器及DAC

电压基准电路为控制ADC和DAC模块工作提供了灵活性。C8051F有3个电压基准输入引脚,允许每个ADC和2个DAC使用一个外部电压基准或片内电压基准输出[9]。在使用DAC之前,必须通过设置REFnCN寄存器的相应位来使能内部电压基准。内部电压基准电路由一个1.2 V、15 ppm/℃(典型值)的带隙电压基准发生器和一个2倍增益的输出缓冲放大器组成。内部基准电压可以通过VREF引脚连到电压基准输入引脚。从芯片数据手册中可知DAC工作所需VRER=2.4 V,而基准电压发生器使用内部带隙基准作为即可产生2.4 V的输出电压,因此在使用DAC之前,还必须通过设置REFnCN寄存器的相应位(BIASE 和REFBE)为‘1’来使能内部电压基准。

程序中与上述对应的源代码为:

每个C8051F020器件都有2个片内12位电压方式数/模转换器(DAC)。可以用对应的控制寄存器DAC0CN到DAC1CN允许/禁止DAC0和DAC1。在被禁止时,DAC的输出保持在高阻状态,DAC的供电电流降到1 μA或更小。每个DAC的电压基准在VREFD引脚提供。

DAC为电压输出方式,有灵活的输出更新机制,允许无缝满刻度变化并支持无抖动输出更新适合于波形发生器的应用。此更新机制允许用基于定时器4的溢出信号更新DAC输出。 在ADC转换操作中,ADC转换可以由定时器溢出启动,不用处理器干预。与之类似,DAC的输出更新也可以用定时器溢出事件触发。这一特点用于DAC产生一个固定采样频率的波形时尤其有用,这样可以消除中断响应时间不同和指令执行时间不同对DAC输出时序的影响。当DAC0MD位(DAC0CN.[4∶3])被设置为‘10’时,对DAC数据寄存器的写操作被保持,直到相应的定时器溢出事件(定时器4)发生时DAC0H:DAC0L的内容才被复制到DAC输入锁存器,允许DAC数据改变为新值。设计中采用定时器4溢出更新输出,DACn输出更新发生在定时器4溢出更新输出之时。这意味着写DACnH和DACnL并不立即影响DAC输出,写入值将被保持,直到发生下一次定时器4溢出时才更新DAC。

1.2.4 初始化定时器4并产生中断

定时器4是一个16位的计数器/定时器,由2个8位的SFR组成:TL4(低字13节)和TH4(高字节)。它使用系统时钟作为时钟源。定时器4提供3种工作方式,这里采用方式1(自动重装载的16位计数器/定时器),用于控制DAC输出的采样速率[10]。当计数器/定时器寄存器发生溢出(从0×FFFF到0×0000)时,自动重装载方式的计数器/定时器将定时器溢出标志TF4置‘1’,产生一个中断。溢出时2个捕捉寄存器(RCAP4H,RCAP4L)中的16位计数初值被自动装入到计数器/定时器寄存器,定时器重新开始计数。设计中DAC采样速率就是通过初始化定时器4的重载值来设置的,重载值是2次中断之间的SYSCLK周期数。该值是负值,这是因为C8051定时器是向上记数的。可以用下面的公式计算该值,即:定时器4重载值=SYSCLK/SAMPLE_RATE_DAC DAC所允许的最大采样速率大约为100 kHz,这是由10 μs的输出建立时间决定的。在选择DAC采样频率时,还必须考虑到2次定时器4中断服务程序要执行的所有指令的最长时间,否则输出频率将受到影响。设计使用22.1 MHz的SYSCLK和80 kHz的DAC更新速率,这就允许ISR在276个SYSCLK周期内执行结束,这主要是在采样速率和定时器4 ISR的执行时间之间进行权衡。

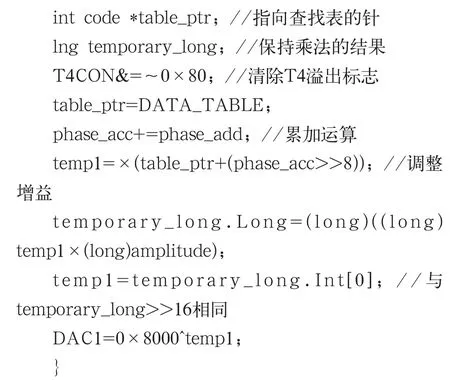

程序中与上述对应的源代码为:

1.2.5 波形产生

在定时器4溢出时将调用中断处理程序,波形产生完全在定时器4的ISR中完成,分为三级实现。所有产生的波形都用一个16位的累加器,用它来记录输出波形在横轴上的位置。在给定DAC的更新频率为80 kHz时,该累加器提供1.2 Hz的频率分辨率。定时器4 ISR中的第一级根据波形的设置查找与累加器对应的下一个DAC输出值。每次调用定时器4 ISR时,累加器的值增加

程序中与上述对应的源代码为:

2 Cygnal C8051F单片机开发工具

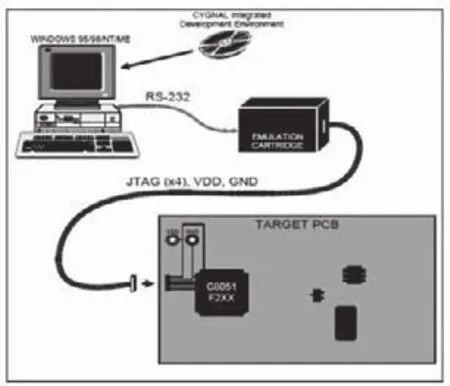

Cygnal的开发工具实质上就是计算机IDE调试环境软件及计算机USB口到C8051F单片机JTAG口的协议转换器(EC2)的组合。Cygnal C8051F系列所有的单片机片内均设计有调试电路,该调试电路通过边界扫描方式获取单片机片内信息,通过4线的JTAG接口与开发工具连接以便于进行对单片机在片编程调试。适配器(EC2)一端与计算机相连,另一端与C8051F单片机JTAG口相连,应用Cygnal提供的IDE调试环境可以进行非侵入式、全速的在系统编程(ISP)和调试。开发工具与PC机(已安装Cygnal IDE)硬件连接:在系统编程和调试环境如图4、图5所示。

图4 硬件连接示意图

图5 Cygnal IDE

3 结果与讨论

经过上述描述的过程,将产生膈神经模拟信号植入正常家兔进行活体实验(如图6、7所示)。

图6 刺激器

图7 膈神经模拟信号波形

其大致波形形状与正常家兔膈神经脉冲信号(通过Matlab 6.5程序绘制波形)一致。该刺激器在示波器上的实际输出频率为200 Hz、幅度为2 V。由此,初步实现了神经刺激信号的发生。

目前,由于此类植入式神经刺激器研制领域的人不多,该神经刺激器的研制过程是一个开拓的过程,并无仿效先例,因此改进工作还将不断进行。

[1]柏树令.系统解剖学[M].5版.北京:人民卫生出版社,2001:50.

[2]夏奕俊,徐向阳,崔茂龙,等.模拟膈神经脉冲电刺激促进周围神经再生的研究[J].中华实验外科杂志,2004,21(10):1219-1221.

[3]夏奕俊,徐向阳,崔茂龙,等.膈神经脉冲电刺激促进周围神经再生的实验研究[J].中华手外科杂志,2004,20(4):246-248.

[4]Dong Z, Sinanan A, Parkison D, et al.Schwann cell development in embryonic mouse nerves[J].J Neurosci Res,1999,56(4):334-348.

[5]Weidner N, Blesch A, Grill RJ, et al. Nerve growth factor-hypersecreting Schwann cell grafts augment and guide spinal cord axonal growth and remyelinate central nervous system axons in a phenotypically appropriate manner that correlates with expression of L1[J].J Comp Neurol,1999,413(4):495-506.

[6]Varon S,Conner JM. Nerve growth factor in CNS repair[J].J Neurotrauma,1994,11(5):473-486.

[7]李勋.单片机实用教程[M].北京: 航空航天大学出版社,2006:65-71.

[8]马喜顺,陶庸.高速SOC单片机C8051F[J].电子产品世界,2002(5A):63-64.

[9]阎石.C8051F单片机应用解析[M].北京:航空航天大学出版社,2002:34-35.

[10]郭玉霞.MCS-51系列单片机原理与应用[M].北京:航空航天大学出版社,2010:44-46.