X波段低相噪跳频源的设计与实现

梁刘永,张 龙

(中国空空导弹研究院 河南 洛阳 471009)

X波段低相噪跳频源的设计与实现

梁刘永,张 龙

(中国空空导弹研究院 河南 洛阳 471009)

结合直接数字频率合成(DDS)和锁相环(PLL)技术完成了X波段低相噪本振跳频源的设计。文章通过软件仿真重点分析了本振跳频源的低相噪设计方法,同时给出了主要的硬件选择和详细电路设计过程。最后对样机的测试结果表明,本方案具有相位噪声低、频率控制灵活等优点,满足了实际工程应用。

锁相环;直接数字频率合成;低相噪;X波段

随着电子技术的发展,雷达、通信、电子对抗等各类电子系统对频率源的相位噪声、频率转换时间、频率分辨率及体积、功耗等指标要求越来越高。目前频率合成的方式主要有4种[1-3]:直接模拟频率合成(DAS)、锁相环频率合成(PLL)、直接数字频率合成(DDS)、混合频率合成(DDS+PLL)。DAS 频率转换时间快,但体积、功耗大,目前已很少采用;PLL输出频率高、频带宽、输出频谱质量好,但频率辨率低、快转换慢;DDS具有频率分辨率高、频率转换时间短、输出相位噪声低等优良特性,但输出频率低、杂散特性差,将DDS结合PLL的频率合成技术综合了两者的优点成为目前雷达系统中经常采用的频率合成方式[4-6]。

文中设计了一个X波段低相燥跳频源,通过详细设计及仿真,测试结果表明该跳频源具有低相噪、跳频时间短的优点,能够很好地满足系统设计的要求。

1 系统主要指标与方案

1.1 系统主要指标要求

本文要实现一个X波段跳频源作为系统下变频接收链路的本振信号,其主要技术指标要求如下:

1)工作带宽:100 MHz

2) 相位噪声:≤-85 dBc/Hz@10 kHz;

3) 杂散抑制:≥-65 dBc;

4) 谐波抑制:≥-50 dBc;

5) 跳频时间:≤20 μs;

6) 跳频步进:2 MHz;

7)输出功率:≥10 dBm。

1.2 系统方案设计

由指标可以看出,相位噪声和杂散是本系统的两个关键指标项,本方案以100 MHz晶振为基准,通过DDS+PLL技术的L波段跳频电路,与基于PLL的X波段点频电路通过上变频实现本振跳频功能。方案原理如图1所示。

图1 X波段本振跳频源原理框图Fig.1 Block diagram of X band LO hopping source

方案中X波段点频源直接采用PLL合成的方式,PLL相当于一个窄带跟踪滤波器,具有良好的频率稳定度及相位噪声特性,结构简单、便于集成。

DDS和 PLL结合常见的有 PLL内嵌 DDS、DDS和 PLL输出混频及DDS激励PLL等方案,前两种都需要混频器进行频谱的搬移,混频器的非线性将会产生大量的杂散谐波,对混频器后端的带通滤波器提出了较高的要求,增加了系统设计的复杂度,特别当DDS的输出频率不高时,混频出的有用信号和镜频信号很近,很难用滤波器滤除干净,因而,本文的L波段跳频源选择的是DDS直接激励PLL的方案。

2 系统指标论证与仿真

2.1 相位噪声分析

本方案采用X波段点频源与L波段跳频源上变频的方式实现本振跳频功能,根据混频时噪声相加原理,为满足本振源的相噪指标要求,X波段点源及L波段跳频源的相噪指标均须满足指标要求。

典型锁相环电路包括鉴相器(PD)、N分频器、环路滤波器(LPF)、和压控振荡器(VCO)和参考输入等部分组成,它们是影响环路噪声性能的主要因素。根据锁相环理论,在小信号锁定状态下可将其视为线性系统,环路输出相位噪声可以计算成所有环路噪声源的均方根之和,图2给出了环路噪声模型。

图2 锁相环相位噪声模型Fig.2 Model of PLL phase noise

图中 Φosc、ΦR、ΦPD、ΦLPF、ΦVCO、ΦN分别为参考晶振、前置分频、鉴相器、环路滤波、压控振荡器及分频器引入的相位噪声,ΦOUT为输出相位噪声。根据锁相环传输特性:

开环传递函数:

闭环传递函数

则参考晶振引入的相噪:

鉴相器引入的相噪:

压控振荡器引入的相噪:

分频器引入的相噪:

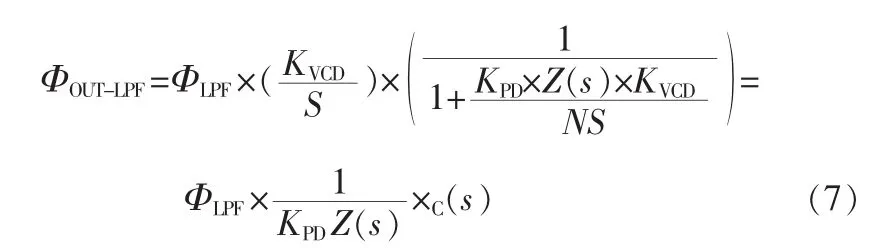

环路滤波引入的相噪:

由于锁相环闭环传递函数的低通特性:

则由噪声传递函数和环路传递函数可知,在环路带宽以内,相位噪声主要由晶振、鉴相器、和分频器引入、而在环路带宽外,相噪主要由VCO决定。为降低相噪我们采取了以下措施:

1)采用高稳定、低相噪晶体振荡器作为参考振荡源。

2)选用低相噪鉴相器、提高鉴相频率。

3)合理设计环路带宽,兼顾相噪和跳频时间。

根据锁相环相噪经验公式,对该方案相位噪声进行估算:

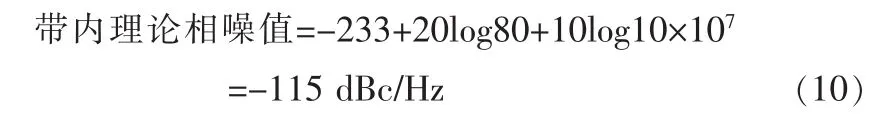

对于X波段点频源,选择100 MHz低相噪晶振作为参考信号,同时鉴相频率选择为100 MHz,PD选用模拟鉴相器HMC440,其特点是工作频率高(可达 2 800 MHz),噪声基底非常低(SSB相噪基底-233 dBc/Hz,并集成5 bit数控程序分频器,是低相位噪声锁相频率合成器的关键部件,将参数代入式(9)

同理,对于L波段跳频源,锁相芯片选择AD公司的ADF4106,该产品归一化相噪基底为-219 dBc/Hz。

根据混频时噪声相加原理,考虑放大器的相噪恶化(按3 dB估算)。X波段点频和L波段跳频源混频后输出相噪为:

图3 X波段点频源相位噪声仿真结果Fig.3 SimulationresultofXbandpoint-frequencysourcephasenoise

图4 L波段跳频源相位噪声仿真结果Fig.4 Simulation result of L band hopping source phase noise

图3、图4分别给出了X波段点源和L波段跳频源的相噪仿真结果。从图中可以看出,两部分电路相位噪声与指标相比均有较大余量、保证了混频放大后相噪满足指标要求。

2.2 杂散特性分析

锁相环杂散主要有两种,一种是外部串扰对VCO的调制,另一种是鉴相频率的泄漏,对于外部串扰需要找到干扰源,切断干扰回路。而对于鉴相泄漏一般是在通过合理设计环路带宽,利用环路的低通滤波特性来抑制鉴相泄漏,必要时可在环路滤波器之后再加一级低通滤波的方法加以抑制,为了不影响环路滤波的参数,辅助滤波的带宽一般应取环路带宽的十倍以上。另外鉴相频率不能取的太低,避免其落入环路带宽内。对于本方案L波段跳频环环路带宽设计为100 kHz,远远小于DDS输出的鉴相频率,由于环路的低通滤波的特性可以将鉴相频率抑制到80 dBc以下,同样的X波段点源的环路带宽设计为1 MHz,也远低于100 MHz的鉴相频率,可以较好地抑制鉴相泄漏。

DDS的杂散很多[7],主要由于幅度量化误差和相位截断误差产生,大小一般在-80~-75 dBc之间。当用DDS驱动PLL时,因为PLL相当于一个窄带高Q值得跟踪滤波器,在环路带宽以外,DDS的杂散大部分都会被抑制。

L波段跳频源和X波段点频源上变频产生的组合杂散采用腔体滤波器滤除,腔体滤波器具有插损小、Q值高、带外抑制好的特点,适用微波频段应用,实际定制加工的滤波器阻带抑制达65 dB。图5给出了信号和杂散经过混频、滤波、放大后的功率估算。从图中可以看出,输出信号对混频组合分量的泄漏抑制达74 dBc,满足指标65 dBc的要求。

图5 本振源对混频组合分量的抑制Fig.5 The restrain of local oscillator to mixing combination

另外,在本方案中多个器件需要共用电源,为避免信号同过电源线相互串扰,在电源处理上增加去耦电路,低频大容量电容和高频低容量电容配对使用,并在器件引脚出增加去耦电容,提高电路杂散性能。

2.3 跳频时间分析

由于方案采用X波段点源和L波段跳频源上变频方案,跳频时间主要由L波段跳频源决定。L波段跳频环的跳频锁定时间包括DDS的频率转换时间、PLL的转换时间和控制电路转换时间。DDS频率跳变时间为纳秒级,与PLL和控制电路的转换时间相比可以忽略。

PLL频率转换时间与环路状态有关,锁相环的存在着相位捕获和频率捕获两个过程。通常频率捕获的时间远大于相位捕获时间,锁相环跳频时间通常指的就是频率捕获时间。本文采用高直流增益的有源比例积分二阶环,频率捕获时间取决于以下因素:

1)跳频步长:步长越小,捕获时间越短,反之越长,对于本方案,DDS激励的频率步进在kHz范围,可以保证环路有较小的捕获时间。

2)环路带宽:带宽越宽,捕获时间越短,反之越长。同时环路带宽的选择还要兼顾PLL的相噪性能,一般选择为VCO的相噪特性曲线和锁相芯片相噪特性曲线的交叉点。

3)阻尼系数:阻尼系数越大,捕获时间越短,反之越长。

ADIsimPLL是ADI公司推出的专门用于锁相环电路设计的软件,其内部提供了大量的器件模型,操作界面简洁,非常适用于ADI公司的PLL芯片进行设计。采用图6所示的原理框图,对锁相环进行了仿真,图7为环路仿真结果。从跳频时间仿真结果中可以看出频率稳定时间只有5 μs。频码控制部分采用FPGA并行控制DDS芯片的方式,可以将控制转换时间控制在10 μs以内,频率转换总时间最终可以满足指标。

图6 L波段跳频源仿真原理图Fig.6 L band hopping source simulation schematic diagram

3 硬件电路加工及测试

本振源低频电路板采用FR-4,介电常数为4.6,高频部分采用Rogers5880,介电常数2.2。加工过程包括芯片共晶、金丝键合、基片烧结、回流焊贴装工艺、总装等工序,对于局部需要手工调试的器件采用手工焊接工艺。

图7 L波段跳频源跳频时间仿真结果Fig.7 Simulation result of L band hopping source hopping time

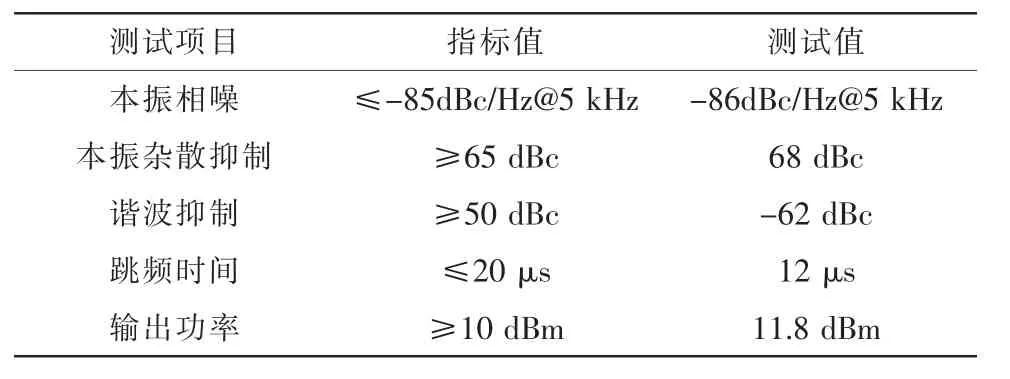

由于整个电路结构复杂,既有模拟电路又有数字电路,模拟电路中又含有中频电路和微波电路,为了保证低相位噪声和杂散性能,避免各个部分之间的射频干扰,采取了多腔体结构,并在结构设计中尤其注意了微波吸波材料的使用。在整体电路加工完后,加电测试,针对各个功能模块问题,在调试过程中先分腔逐个功能模块进行调试,通过不断调试改进,表1为电路测试结果。电路测试值表明各项性能均达到了指标要求。

表1 X波段本振源实际测试结果Tab.1 Test results of X band LO

4 结 论

作为X波段跳频接收机的关键部分,本文综合利用DDS和PLL技术完成了X波段本振跳频源的详细设计和加工测试,测试结果表明方案合理可行。文章通过理论分析和仿真详细论证了相位噪声、杂散和跳频时间等频率源关键指标的实现方法。所完成的频率源具有相噪低、频率控制灵活等优点,达到了预期的工程目标。

[1]费元春.宽带雷达信号产生技术 [M].北京 国防工业出版社,2002.

[2]张厥盛.锁相技术[M].西安:西安电子科技大学出版社,2001.

[3]白居宪.低相噪频率综合[M].西安:西安交通大学出版社,1995.

[4]杨国渝.采用DDS+PLL技术实现S波段频率合成的一种方法[J].电子科技大学学报,1999,28(4): 388-391.

YANG Guo-yu.A new methodofDDSHybridPLL technology in an s-band frequency synthesizer[J].Journal of University of Electronic Science and Technology of China,1999,28(4 ): 388-391.

[5]任鹏.一种基于DDS和PLL技术本振源的设计和实现[J].现代电子技术,2009(9): 178-180.

REN Peng.Design and implementation of local oscillator based on DDS and PLL[J].Modern Electronics Technique,2009(9): 178-180.

[6]李俊俊.基于DDS+PLL频率合成器的设计和实现[J].电子测量技术,2009,32(4): 26-30.

LI Jun-jun.Implementation of frequency synthesizer base on DDS and PLL [J].Electronic Measurement Technology,2009,32(4): 26-30.

[7]蔡竟业.一种高分辨率低杂散频率合成器的研制[J].电子科技大学学报,2005,34(6): 1009-1012.

CAI Jing-ye.Design of a high-resolution and low-spurious frequency synthesizer[J].Journal of University of Electronic Science and Technology of China,2005,34(6): 1009-1012.

Design of an X-band low phase noise local oscillator

LIANG Liu-yong,ZHANG Long

(China Airborne Missile Academy,Luoyang471009,China)

An X-band low phase noise local oscillator is described based on DDS and PLL technology.Deeply,it analyses implementation of low phase noise using software simulating.Also,the main hardware devices and specific circuits is introduced.At last,the test results indicate that the oscillator obtains advantages of excellent phase noise and quality of flexible frequency controlling.It can meet the needs of project practically.

PLL ;DDS; low phase noise; X band

TN74

A

1674-6236(2012)04-0135-04

2011-12-16 稿件编号:201112093

梁刘永(1982—),男,河南郑州人,硕士,助理工程师。研究方向:雷达系统微波频率源研制。