纳米光波导表面粗糙度与散射损耗的分析与测试*

臧俊斌,薛晨阳,2,晋玉剑,仝晓刚,韦丽萍,刘 超

(1.中北大学电子测试技术国防科技重点实验室,山西太原030051;2.中北大学仪器科学与动态测试教育部重点实验室,山西太原030051)

0 引言

硅基光波导器件由于其高可靠性、易集成、低成本、与微加工工艺具有良好的兼容性,在光源[1]、光波导放大器、光开关[2]、光量子计算机[3]、光子晶体器件等领域有着重大的潜在应用价值,引起了国际学术机构和学者的高度关注。高性能光波导器件的实现依赖于低损耗的波导结构单元,因此,对低损耗光波导的研究具有重要的科学意义与应用价值。

SoI材料用于制作光波导器件具有以下优势:波导层Si和限制层SiO2之间的折射率差[4]很大,从而可降低器件尺寸,提高芯片的集成密度;SoI光电子工艺与标准的CMOS工艺完全兼容,为同一芯片内的光电互联和光电集成器件[5,6]提供了可能,且易于规模化生产;SoI波导通过成熟的加工工艺可以实现很小的传输损耗。目前,SoI材料的制备技术成熟多样,晶片价格也在不断下降;本文中主要研究了SoI纳米光波导[7]光传输过程中的散射损耗与热处理后对表面粗糙度的影响。

1 波导传输损耗的理论分析

一般来说,造成损耗主要有3种方式:散射、吸收、弯曲。散射损耗通常主要产生在介质波导[8,9]中,对直波导的损耗起主要影响;当波导结构发生弯曲时,辐射损耗将变得特别严重[10],此时的损耗主要为辐射损耗;而吸收损耗主要是针对于半导体和其他晶体材料而言,与材料组分有关。

通常采用量子学来准确描述损耗的产生机理,但由于量子学深奥且不易于直观理解和掌握,因此,本论文主要进行了直观的散射损耗分析,并结合所制备的波导进行了表面粗糙度的实验测试。

光波导中散射损耗主要分为体散射损耗和表面散射损耗[11]。体散射主要是由杂质或缺陷(杂质原子、晶格缺陷、空位)引起的。单位长度的体散射损耗正比于该单位长度内的缺陷数[12],此外,体散射损耗还取决于缺陷的尺寸值。但体缺陷值相对波长来说很小,因此,体散射损耗比起表面散射损耗影响较小可以被忽略。

由Payne和Lacey定义得散射损耗闭合公式

其中,φ(d)为波导表面模场,k0为空间波数,n1为波导芯层的折射率,n2为包层的折射率,Neff为波导芯层的有效折射率,d为波导层厚度的用来描述波导侧壁的粗糙度。

通常,波导表面的粗糙度符合指数型或者高斯型两种分布,因此,式(1)可以写成

从而,可得散射损耗与表面粗糙度以及波导宽度的对应趋势,如图1所示。

图1 SoI纳米光波导散射损耗与表面粗糙度、波导宽度的关系曲线图Fig 1 Relation curve diagram of SoI nano-optical waveguide scattering loss with surface roughness and waveguide width respectively

由上图分析可得,散射损耗随着波导宽度的增加而减小,对于尺寸一定的波导,其散射损耗与波导各个面的粗糙度σ的平方呈正比。

尽管Payne和Lacey定义得散射损耗闭合公式能直观地表示出粗糙度与散射损耗的对应关系,但计算比较复杂繁琐,因此,本文表面散射损耗的计算采用Tien提出的公式。

Tien提出的表面散射公式简单并准确地定义为

式中 σu为波导上表面的粗糙度均方根,σl为波导下表面的粗糙度均方根,kyu为波导上包覆层的衰减常数,kyl为波导下包覆层的衰减常数,h为波导芯层的厚度。由以上公式可以得出,表面散射损耗取决于波导表面的粗糙度。对于本文中非对称的SoI平板波导为例:n1=3.476,n2=1.462,n3=1,h=0.22μm,因此,由包覆层的衰减常数计算公式可以得到在单模态下TE模式的包覆层衰减常数为

假设波导芯层的上表面和下表面粗糙度均方根σu,σl都为1 nm时,通过计算可得到TE单模态下表面散射损耗为

式中 相应的损耗常数为0.175 dB/cm。

2 制备

本文采用MEMS工艺中的电子束光刻(electron beam lithography)与感应耦合等离子体(inductive coupled plasma,ICP)刻蚀工艺对500 nm的波导进行刻蚀加工。电子束光刻是利用电子束在涂有电子抗蚀剂的晶片上直接进行绘制或投影复印图形的曝光技术,与普通光刻技术最大的区别是通过电子束对电子光刻胶进行曝光,且不受光学衍射极限的制约,可实现比普通光刻更高精度的纳米结构图形转移,其制作线条精度小于10 nm。ICP刻蚀技术是光刻工艺的后续工艺,它结合了化学、物理刻蚀方法的优点,不但可以获得好的刻蚀方向性和选择性,而且大大加快了刻蚀速度,所以,ICP刻蚀技术成为目前刻蚀波导的主流方法。

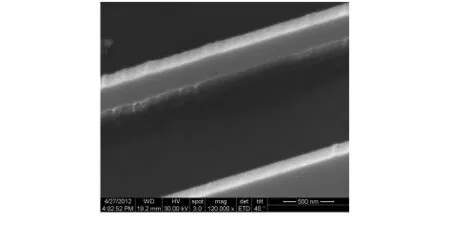

制备中,加工使用的SoI材料其覆层厚度为220nm,最终制备出的波导其刻蚀深度为220 nm(全刻蚀),刻蚀宽度为500nm,刻蚀陡直度达89°±1°。其SEM图如图2所示。

图2 直波导Fig 2 Straight waveguide

3 实验测试

如图3所示为波导的上表面AFM图,表面粗糙度为1.09 nm。图4为采用电子束与ICP刻蚀加工制作的波导侧壁SEM图,该波导结构未进行过任何后处理,由图可估算出侧壁粗糙度为7 nm左右。

图3 AFM分析图Fig 3 AFM analysis diagram

图4 高温热处理前的侧壁SEM图Fig 4 Sidewall SEM photo before hyperthermia heat treatment

由于SoI波导的散射损耗为上下表面散射损耗加上两侧壁的表面散射损耗,所以,由式(5)可估算得到SoI矩形波导未高温热处理前的总散射损耗为9.71 dB/cm。

图5为885℃高温热处理后波导的SEM图,可看出表面粗糙度图明显降低,通过SEM图可估计其表面粗糙度降低至4 nm左右,同上,由式(5)可算得SoI波导高温热处理后的表面散射损耗为3.343 dB/cm。

4 结论

本文系统分析计算了波导散射损耗与表面粗糙度的关系,并进行了波导损耗测试,测试结果与理论分析相符。此外,采用高温热处理使波导表面粗糙度降低了大约3 nm(高温热处理最大化了表面晶粒尺寸,致使表面平滑化),并通过计算证明波导的散射损耗降低了6.37 dB/cm,为今后光波导集成光学的研究和发展提供了很好的基础。

图5 高温热处理后的侧壁SEM图Fig 5 Sidewall SEM photo after hyperthermia heat treatment

[1]Libertino S,Coffa S,Saggio M.Design and fabricated of integrated Si-based optoelectronic devices[J].Materials Science in Semiconductor Processing,2000,3(5-6):375-381.

[2]Sridaran S,Bhave SA.Nanophotonic devices on thin buried oxide Silicon-on-insulator substrates[J].Optics Express,2010,18(4):3850-3857.

[3]Xia Fengnian,Sekaric L,Vlasov Y.Ultra-compact optical buffers on a silicon chip[J].Nature Photon,2007,1:65-71.

[4]Layadi A,Vonsovici A,Orobtchouk R,et al.Low loss optical waveguide on standard SoI/SIMOX substrate[J].Optics Communications,1998,146(1-6):31-33.

[5]王仕超,张晓霞,周 勇,等.基于MZI光波导的MOEMS压力传感器[J].仪表技术与传感器,2009(12):4-6.

[6]Chen Shaowu,Yan Qingfeng,Xu Qingyang,et al.Optical waveguide propagation loss measurement using multiple relections method[J].Optics Communications,2005,256(1-3):68-72.

[7]崔丹凤,薛晨阳,仝小刚,等.垂直纳米光栅耦合器耦合效率分析与测试[J].传感技术学报,2011(8):1132-1135.

[8]Mao SC,Tao SH,Xu Y L,et al.Low propagation loss SiN optical waveguide prepared by optimal low-hydrogen module[J].Optics Express,2008,16(25):20809-20816.

[9]Ang T W,Reed G T,Vonsovici A,et al.0.15dB/cm loss in unibond SoI waveguides[J].Electronics Letters,1999,35(12):977-978.

[10]Vlasov Y A,McNab SJ.Losses in single-mode silicon-on-insulator strip waveguides and bends[J].Optics Express,2004,12(8):1622-1631.

[11]Knight SD.Process and design techniques for low loss integrated silicon photonics[D].Boston,USA:Massachusetts Institute of Technology,2006.

[12]Hunsperger R G.Integrated optics theory and technology[M].USA:Springer Science Business Media,2009:107-128.