片上异构双PowerPC雷达控制器的设计与应用

施海锋,柏玉娴

(南京电子技术研究所, 南京210039)

0 引言

现代相控阵雷达的控制器主要是根据作战任务确定雷达工作方式和工作参数,对雷达资源进行自适应调度与管理,是雷达系统实现多目标、多任务的关键,性能直接影响雷达的目标容量和测量精度[1]。XILINX公司的Virtex-5 FXT平台集成了两个PowerPC440嵌入式处理器内核和若干高速串行收发(Serdes)接口以及大量的IP核[2],获得了VxWorks实时嵌入式操作系统支持,全面地满足了雷达控制的实时性强、接口种类多、集成度高的需求特点,是高性能嵌入式雷达控制器的一个良好选择。但目前该平台的应用处理大多基于VxWorks的单PowerPC,接口主要以千兆以太网等方式为主,既存在着较大的资源浪费,也无法完全满足雷达控制日益增长的性能要求。在不大幅度提高设计成本的前提下,本文提出一种“主-从”异构式控制模型架构的嵌入式雷达控制器设计方案,充分发挥Virtex-5 FXT平台的能力,提高雷达控制器性能。

1 应用需求

雷达控制器一般依据雷达驻留或脉冲周期规划任务,实时数据的接收、处理、发送等工作必须在同一驻留或脉冲周期的规定时间内完成才能实现雷达的协调工作[3]。随着大型数字阵列雷达等新型雷达的研制,雷达控制器面临的新需求主要有:

(1)控制周期要求小于200 μs,并有进一步缩小的趋势;

(2)多雷达间的精密协同要求任务编排精度从几十微秒提高到几十纳秒,并具备多优先级、多驻留的预处理能力;

(3)需要实现高精度的坐标转换,多阵面或多相限的波束指向计算;

(4)控制信息容量快速增长,控制接口的带宽需要达到几Gbps以上、延时控制在几十微秒以内。

以动平台数字阵雷达为例,雷达控制器的主要工作有:信息接收、存储(处理时间T1)、调度指令解析(T2)、系统时间同步(T3)、多优先级任务规划与编排(T4)、定时参数计算(T5)、导航数据平滑(T6)、坐标转换(T7)、波束指向计算(T8)、控制指令生成(T9)、系统状态监控(T10)、指令输出(T11)等。这些任务在逻辑上大多属于关联任务,一个任务的执行依赖于上一个或多个任务的执行结果。只有一个处理器的情况下,几个动态任务同时请求业务时进出运行队列所带来的开销会导致处理时间的不确定,从而降低系统的整体性能。在接口方面,目前使用的以太网TCP/IP协议的解析也会消耗大量的处理器资源。单PowerPC雷达控制器的处理性能和接口能力均无法满足这些新需求。

基于已有的Virtex-5 FXT硬件平台,考虑从两个方面提高雷达控制器的性能:

(1)通过双核并行处理提高处理性能;

(2)采用更好的总线技术提高接口处理能力。

2 关键技术分析与设计

2.1 多核处理架构与操作系统

多核处理器是将多个处理器内核集成在一块芯片上,支持多个处理器内核之间任务的划分和分配,并能够并行执行任务[4]。主流的多核技术主要有两种架构:

(1)对等同构架构,如Intel的酷睿2等。在要求进行并行处理时,同构多核架构容易获得比较好的效果。但同构多核处理性能会受到软件中必须串行执行部分的制约。如果考虑用于保持高速缓存相关性时的同步时间,以及多个内核集中访问内存时的待机时间等,整体处理能力的提升可能并不明显。

(2)“主核+从核”的异构架构,异构处理器集成了包括通用处理器内核和特定高性能处理内核的多种处理核。典型的有TI公司的ARM和数字信号处理DSP结合的OMAP系列多核芯片以及AMD公司的CPU和GPU结合的APU处理器等。异构多核处理器提供了两全和均衡的方案,内核的异构性可以同时执行具有不同要求的应用程序,CPU致力于执行传统处理器的主要任务,比如运行操作系统、执行传统的串行任务等,DSP或GPU等则执行数学密集型计算。

目前,针对多核设计的操作系统处理模式主要有以下3种:

(1)对称多处理(Symmetric multiprocessing,SMP),一个操作系统的实例可以同时管理所有CPU内核,且应用并不绑定某一个内核。

(2)非对称多处理(Asymmetric multiprocessing,AMP),每个CPU内核运行一个独立的操作系统或同一操作系统的独立实例。AMP可以是同构的,所有内核运行同一种类型和版本的操作系统;也可以是异构的,每个内核运行不同类型或版本的操作系统。

(3)混合多处理(Bound multiprocessing,BMP),BMP结合了SMP高级资源管理和AMP应用控制的混合功能,一个操作系统的实例可以同时管理所有CPU内核,但每个应用被锁定于某个指定的核心。

这3种模式都有其各自的优点和缺点。每一个模式适合于解决某方面的特定问题,而且对操作系统的要求也各不相同。

2.2 异构双核架构设计

为满足微秒级的强实时处理要求,雷达控制器一般采用VxWorks操作系统,该系统支持实时系统的一系列特征包括多任务,中断支持,任务抢占式调度和循环调度[5]。操作系统程序对系统进行管理而花费的时间和空间称为操作系统开销。对于VxWorks主要是中断响应、任务切换以及内存管理等。虽然微内核设计使VxWorks缩减了系统开销并加速了对外部事件的反应,但VxWorks的中断处理程序中实现的功能有很多限制,比如不能进行浮点运算、获取信号量等,需要把这些工作留给任务来做。实际测试Power-PC440处理器一次中断响应及任务启动时间需要14-20 μs,当有多个中断与任务时,对于雷达控制器而言是一笔不小的开销。

如何设计Virtex-5 FXT平台中的两个PowerPC440嵌入式处理器架构主要取决于以下3个因素:

(1)实时性设计。核心问题是降低雷达控制器的软件运行时间。如前所述,雷达控制的大多数任务属于串行连接关系,因此SMP并不是最优方案。如果采用AMP方式分别运行 VxWorks操作系统,则两个CPU均有部分资源被用于操作系统自身开销。此时,操作系统的应用反而不能充分发挥处理器性能。

(2)开发成本。目前最新的VxWorks6.X版本操作系统与Workbench集成开发环境已经支持该平台的AMP或SMP应用,但操作系统以及开发环境都是专有的,操作系统的升级成本非常昂贵。

(3)技术可行性。PowerPC440目前既支持基于VxWorks操作系统的开发,也可利用XILINX公司的ISE软件编程实现类DSP的中断处理、浮点运算、接口处理等功能。

根据上述的分析,目前的改进方案是对两个PowerPC核进行异构化的主、从划分:主处理器类似于通用CPU,运行VxWorks操作系统,实现整个系统的管理:包括内存与文件系统管理、人机接口、数据的处理、高速接口控制等;从处理器类似于DSP,配置一个32位浮点运算单元(FPU),专用于计算密集型运算,不运行操作系统,利用C语言编程。

2.3 高速接口设计

以太网TCP/IP协议栈解析需要大量的软件开销,基于Virtex-5 FXT的PowerPC平台与VxWorks6.7环境的测试条件下,标准UDP协议报文的传输性能最高仅达到约180 Mbps。这已经远不能满足现阶段的雷达控制器的带宽与实时性要求。因此需要从商用市场上寻求新的高性能开放式总线技术。

光纤通道(FiberChannel,FC)兼顾了网络与通道的优点,具备高带宽(目前规范最高16 Gbps)、延时确定性(最小延时2 μs)、可伸缩性(包括点到点、仲裁环、交换拓扑)等优点,可为复杂军用综合电子信息系统定制中、大规模的交换系统,提供实时的控制和响应以及大数据量的传输能力。

RapidIO技术是目前惟一的嵌入式系统互连国际标准(ISO/IEC 18372),数据帧小,具备很强的实时性,支持通道捆绑提供更高的带宽,适合于插箱级的紧耦合系统。RapidIO互连定义包含两类技术:面向高性能微处理器及系统互连的ParallelRapidIO接口;面向串行背板、DSP和相关串行控制平面应用的SerialRapidIO接口。本文主要描述的串行 RapidIO技术(sRIO)。

光纤通道FC和RapidIO主要面向高性能嵌入式互连通信,层次结构简洁,均可以实现基于硬件的高效数据传输,成为嵌入式系统应用的优选。

本控制器中采用FC替代千兆以太网接口作为主要外部通讯接口,模块之间数据交互则使用sRIO接口。千兆以太网接口则主要用于系统调试或作为辅助外部接口使用。

3 系统设计

在确定了异构双核架构以及FC、sRIO等外部接口后,嵌入式雷达控制器的具体设计构架如图1,控制器采用符合VITA 46规范的6U VPX板卡形式,基于一片Virtex-5 FX200T芯片构建,处理器与接口功能均采用IP形式在FPGA内部硬件实现(如图1虚线内所示),电平转换、总线驱动则由专用芯片完成。为满足光纤信号的输入输出,采用VPX电光混合连接器。

图1 雷达控制器构架图

3.1 主要性能

嵌入式雷达控制器主要性能如下:

(1)两个 PowerPC440处理器,工作主频 400 MHz;

(2)1GByte片外DDR2 SDRAM,1GByte FLASH;

(3)支持2路4.25G FC、一路X4 3.125G sRIO、自定义协议Serdes接口;

(4)支持多路1000base-T、1000base-X以太网接口。

3.2 硬件设计

集成在FPGA里的两个32位定点PowerPC是控制器的核心,具备独立的内存存储空间(DDR2 SDRAM),主 PowerPC配置了外部程序存储空间(FLASH),从PowerPC的程序运行在FPGA内部的BRAM中,执行文件包含在FPGA的配置文件里。在配置了中断处理器、串口等设备后就组成了一个双PowerPC基本系统。

根据FPGA内部的资源,控制器实现了两路4.25G规范FC,一路X4 3.125G sRIO接口,两种接口协议解析均由FPGA硬件完成,具备高效、稳定的优点。FPGA中仅使用了一个以太网MAC核,通过一片以太网交换芯片实现多通道的1000base-T、1000base-X以太网接口扩展。FPGA内部提供了专用的DMA通道和PowerPC处理器本地总线接口(PLB),挂接在DMA和PLB上的设备可与DDR2内存直接交互数据。每个DMA通道可提供6.4 Gbps(32位,200 MHz)的理论带宽;PLB总线的理论带宽达到了12.8Gbps(128位,100 MHz)[6]。为保证接口带宽,以太网、sRIO、Serdes等接口均挂接在DMA上;两路4.25 Gbps光纤通道使用PLB总线。

两个内核之间的通信机制是双核系统设计的关键[7]。本方案中,主处理器面临多个任务并管理通讯接口,因此中断源多,配置专用的中断控制器,可实现32个中断源的多优先级控制。从处理器主要用于高性能的计算,任务相对较少,因此利用GPIO状态触发实现简单快速的中断响应。主处理器与从处理器之间主要通过中断实现同步与互斥,并通过FPGA内部的双口RAM实现数据共享,为避免两个处理器同时写同一片RAM区引起的数据出错,提前将内存分为若干块并分配给每个任务,每块内存地址空间只允许一个处理核进行写操作。

3.3 双核开发流程

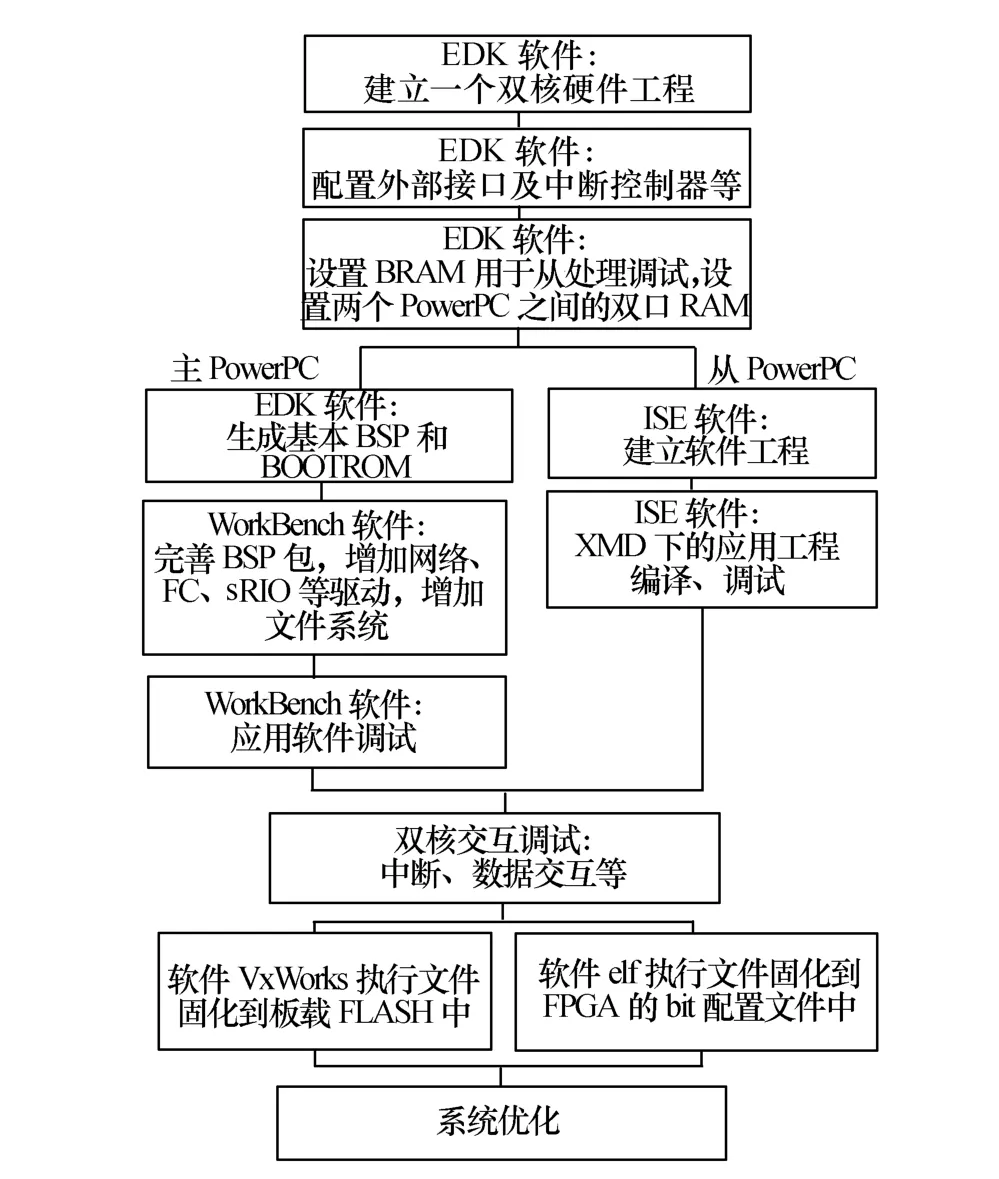

双核的开发需要利用ISE套件和Workbench软件共同完成,首先通过ISE套件中的EDK软件调用PowerPC、DMA控制器、PLB总线控制器、内存接口控制器、FPU、以太网 MAC、sRIO、FC等硬核组成一个双PowerPC硬件系统,对各IP进行内存地址、中断等的配置后,再分别对两个PowerPC进行不同的软件设计:主处理首先生成最简化BSP包,逐步增加各种驱动后开展VxWorks操作系统的软硬件的调试;从处理直接利用ISE软件进行编程与调试;两个PowerPC分别完成调试后开展中断和内存交互等的协同调试。具体流程如图2所示。

图2 雷达控制器双核开发流程图

4应用

根据现在的设计,操作系统无法对两个处理器进行统一的任务调度与资源平衡。因此,双核之间任务的预先分配是双核能否发挥最大效能的关键。任务规划及并行处理优化原则如下:

(1)任务属性分类及分配。主处理器完成涉及大量内存与外部接口操作的任务;从处理器完成涉及大量浮点运算的任务;

(2)对任务进行功能内聚及优先级规划,关联性强的工作作为一个任务来运行,避免多个任务之间大量的通信影响系统效率;对于实时性要求高的任务以高优先级运行,以保证事件的实时响应;

(3)主、从处理器均采用静态内存分配方案,在程序编译时候将所有需要的内存都已经分配好。避免内存动态分配带来的延时或一次分配失败;

(4)对所有任务的处理时间进行测算,合理调整部分任务的执行顺序,将主、从处理器之间的等待时间控制为尽可能短。

双核任务规划如图3所示。

图3 双核任务规划示意图

应用表明:预先规划较好的实现了主、从处理器的负荷均衡,提高了双核执行效率和处理性能;FC、sRIO等基于硬件处理协议接口大幅减少了CPU在接口协议处理上的开销。双核控制器对比基于千兆以太网的单核处理控制器,性能改善最高可达到60%以上,实际传输带宽提高了10倍以上。基于千兆以太网的单核处理控制器原先可满足最短600 μs左右雷达驻留周期的实时控制;双核控制器则可满足200 μs以内驻留周期的应用需求。

5 结束语

多核处理进入嵌入式系统是大势所趋,内嵌高性能多核处理器的FPGA在嵌入式控制领域具有广阔的应用前景。本设计针对雷达控制特定的应用需求,在设计成本及技术风险有效控制的前提下,充分挖掘Virtex5-FXT平台的能力,实现了一种异构式双Power-PC雷达控制器的构建与应用,改进后的控制器处理性能得以大幅提升。同时,FC、sRIO等国际规范的高速接口的应用,使得控制器具备了良好的通用性。该控制器被应用于大型数字阵列相控阵雷达中,取得了良好的使用实效和较高的性价比。

[1] 舒亚海.舰载相控阵雷达反导技术研究[J].现代雷达,2013,35(4):6-9.Shu Yahai.Anti-missile prospect of shipborne phased array radar[J].Modern Radar,2013,35(4):6-9.

[2] Xilinx,Inc.Virtex-5 FPGA user guidedata book[Z].MARCH 31,2008:22-24.

[3] 邱国华,史国庆.相控阵雷达中实时雷达控制的设计方法[J]. 现代雷达,2003,25(6):22-24.Qiu Guohua,Shi Guoqing.Design method for real-time radar control system in phased array radar[J].Modern Radar,2003,25(6):22-24.

[4] 陈芳园,张冬松,王志英.异构多核处理器体系结构设计研究[J]. 计算机工程与科学,2011,33(12):27-36.Chen Fangyuan,Zhang Dongsong,Wang Zhiying.Research of the heterogeneous multi-core processors architecture design[J].Computer Engineering & Science,2011,33(12):27-36.

[5] 张晓平,王 剑.基于嵌入式系统的雷达控制器[J].现代雷达,2004,26(4):35-37,42.Zhang Xiaoping,Wang Jian.Radar controller based on embedded system[J].Modern Radar,2004,26(4):35-37,42.

[6] Xilinx,Inc.Embedded processor block in virtex-5 FPGAs[Z].MARCH 31,2008.

[7] 刘 建,陈 杰,敖天勇,等.片上异构多核DSP同步与通信的实现[J].电子科技大学学报,2010,39(4):528-531,536.Liu Jian,Chen Jie,Ao Tianyong,et al.Implementations of synchronization and communication in heterogeneous multicore DSP[J].Journal of University of Electronic Science and Technology of China,2010,39(4):528-531,536.