基于DSP和FPGA双CPU架构的导航微机系统

高延滨,刘辉煜,何昆鹏,张兴智

哈尔滨工程大学自动化学院,黑龙江哈尔滨 150001

基于DSP和FPGA双CPU架构的导航微机系统

高延滨,刘辉煜,何昆鹏,张兴智

哈尔滨工程大学自动化学院,黑龙江哈尔滨 150001

为了满足惯性系统的小型化发展,设计了一种体积小、功耗低、价位低的高性能导航微机系统。此导航微机系统由TI公司数字信号处理器芯片TMS320C6726和Altera公司的FPGA芯片EP3C10E144A7两种CPU组成,DSP主要负责导航数据处理和算法运算,FPGA主要负责惯性测量单元(IMU)的数据采集和接口控制。该微机系统充分利用了TMS320C6726的运算速度快、浮点数据处理能力强和FPGA的SOPC技术的特点,通过VHDL语言编程实现双口RAM接口完成双CPU的快速数据通信。两种CPU能分别发挥自身优势,协调地工作,提高了导航计算机的运行效率。

导航微机系统;信号处理器;双CPU;双口RAM;捷联解算

随着捷联惯性导航技术的成熟及其在无人机上的应用,促使捷联惯性导航系统向低成本、小体积和低功耗方向发展。捷联式导航系统采集信号种类多,算法较复杂,因此导航计算机需要有丰富的接口和快速的数据处理能力。传统的导航计算机大多为专用计算机、通用计算机平台、嵌入式工控机(PC104)等,它们体积大、功耗大、价格高,不适用于小型制导场合[1]。近年来,随着各种嵌入式处理器的发展,出现了运算能力强大的数字信号处理器和可编程的逻辑器件。数字信号处理器(DSP)是专为高速数据处理而设计的微处理器,其改进的哈佛结构、先进的多地址/数据总线和多级流水线机制、专用的硬件乘法器和高效的指令集使芯片的指令周期降到10 ns以下;先进的制造工艺使其功耗仅有数十毫瓦;其体积通常在25 mm×25 mm左右。现场可编程门阵列(FPGA)具有编程方便灵活、集成度高、处理速度快、低功耗、高性价比、可靠性高等优点。在此,结合DSP和FPGA各自的特点,设计一种主从式、双处理器体系结构,适用于小体积、低功耗和低成本捷联惯性导航系统[2]。

1 导航微机系统的总体设计

导航微机系统主要有2个功能:一是数据的输入和输出,包括采集惯性器件的输出信号,接收上位机的校正信息、初始对准信息和控制信息,输出解算后的导航参数[3]。二是数据处理和计算,包括初始对准、导航解算、在线校正、误差补偿和滤波等。这就要求导航计算机有较强的数据处理能力和灵活的控制功能。对于后者是DSP的优势所在,可以很好的完成。但是对于前者,和外界进行大量的数据交换和外围设备的控制则是DSP的弱项,勉强令其完成,则其赖以进行高速数据处理的多级缓冲和高速流水线机制将被频繁打断,最终使DSP的优势无法发挥[4]。

FPGA是随着微电子设计技术和工艺的发展而产生的一种现场可编程逻辑门阵列。它通用性强,可根据用户不同的需求实现特定的功能,内部有大量的触发器和I/O接口,采用高速CHMOS工艺,大大降低了芯片的功耗,扩充接口和增加控制单元只需FPGA内部资源满足即可,不再会有新增元器件和扩大计算机体积的额外负担,这些特点恰好符合导航计算机的多接口,多流程控制以及小型化的需求,可以和DSP进行优势互补。做为导航计算机中的外设通信和控制单元,负责数据传输和流程控制,DSP则只用来导航算法处理,这样能使导航计算机的体积指标和整体性能得到提高。

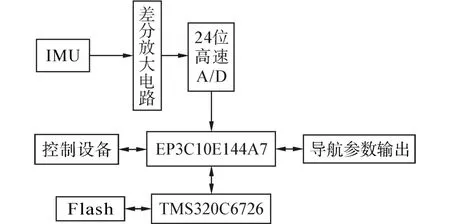

本系统设计以发挥DSP和FPGA的最佳性能为原则,DSP完成导航的算法处理,FPGA完成惯性器件的数据采集和简单的处理,比如剔除野值,平滑滤波等,系统和外界所有的通讯都由FPGA负责,总体结构如图1所示。

图1 总体结构

2 数据处理系统的设计

2.1 数据采集系统设计

数据采集负责导航系统中所有信号的输入,主要包括陀螺、加速度计、里程计和GPS的信号输出。根据信号的格式不同,需要设计不同的接口电路:里程计和GPS的信号输出通常为串行模式,利用Al-tera公司提出来的SOPC方案,即在FPGA上嵌入NiosII软核处理器,通过UART内核接收数据提供给NiosII软核处理器。陀螺和加速度计的输出一般分为数字脉冲和模拟电压2种,如果输出是数字脉冲,可以在软核上设计一个高精度频率采样系统[5],这样的设计比一般的计数器设计可靠性高;如果惯性测量单元(IMU)输出是模拟电压,则需要一个A/D电路把模拟电压转换成数字信号,A/D电路做为信号进入FPGA的前端,关系到IMU信息的准确性和可信度。本系统是针对模拟电压输出设计的,根据系统的精度要求,选用了Linear公司的24位高速差分A/D芯片LTC2440。

LTC2440是一款只有5 μV偏移的高速24位无延迟增量累加模数转换器,它是SPI接口输出,采用专有的增量累加型架构,实现了无延迟的可变速度和分辨率。10种速度/分辨率组合可通过一个简单的串行接口来设置,也可以通过把单个引脚连接至高电平或低电平来轻松地选择一种快速超低噪声速度/分辨率组合。转换的准确度和器件的功耗与所选的速度无关,但是输入电压变化范围较小,只有±2.5 V。为了扩大LTC2440的电压输入范围,在电路前端加一个全差分衰减放大器AD8475,可提供精密衰减0.4倍,惯性器件的输出可以扩大到±5 V以上。由于惯性器件的输出有高频噪声,需要插入一个前置采样滤波器,将前置采样滤波器的带宽设置为采样频率的1/3,并在FPGA中对数据进行滑动平均滤波,以上的设计能很好的保证数据的精度和实时性。

2.2 DSP处理器的外围电路设计

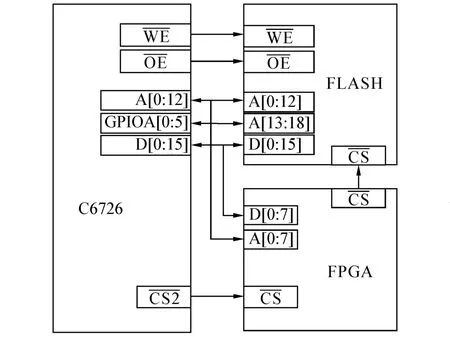

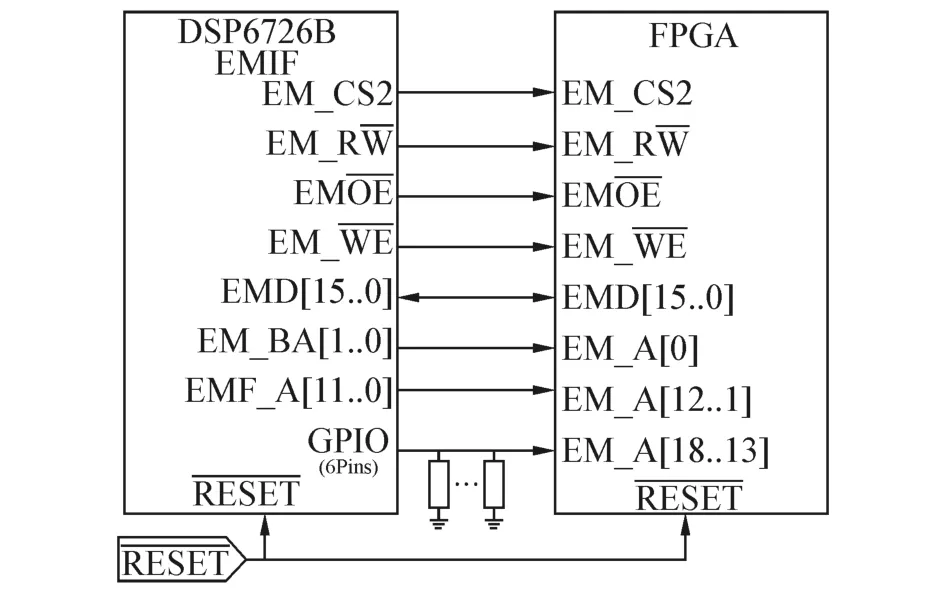

本系统DSP选用TMS320C6726处理器,C6726支持32位单精度浮点和64位双精度浮点运算[6],在系统中负责导航解算的功能。设计了DSP的最小系统,其外围电路控制主要就是Flash读写操作和与FP-GA的数据通讯,如图2所示。

图2 DSP最小系统及外围电路

在本设计中,FPGA与DSP的通信是通过双口RAM来实现的。在FPGA内部设计双口RAM,双口RAM的地址线和数据线连接到DSP的EMIF接口上,同时Flash也连接到EMIF接口上,这样就涉及到共用地址线和数据线的问题。在本设计中,在FPGA内部使用VHDL硬件描述语言设计逻辑电路,通过DSP的GPIO控制片选信号连接到RAM上或Flash上。DSP与Flash和FPGA的接口如图3所示。

图3 Flash与DSP接口

2.3 FPGA的基础平台设计

FPGA的主要任务是将A/D转换后的数据进行采集并将数据发送给DSP进行解算。在Altera公司提供的Quartus II软件中利用Qsys,即可进入Nios II软核定制设计界面。基于SOPC的设计中,Nios II处理器、SDRAM控制器、EPCS控制器、SYSTEM ID和JTAG UART内核是系统运行最基本的定制,其他的内核都是根据所设计系统的需求而进行的定制[7]。在本设计中,使用的都是系统自带的内核。

3 DSP与FPGA数据传输

随着FPGA的应用越来越广泛,Altera公司的Qsys嵌入式系统中添加了为外设进行预留接口的功能。因此本文设计了一种基于Qsys的双口RAM与DSP6726的EMI外部存储器扩展接口,双口RAM可用于提高 RAM吞吐率,用于实时数据缓存[8-9],实现了DSP6726与NiosII软核之间导航数据的交互传输。

3.1 基于Qsys的双口RAM

Qsys是Altera公司在Quartus II 11.0版中开始发布的系统集成工具,它在SOPC Builder基础上实现了新的系统开发特性,提高了FPGA设计者的工作效率。Qsys系统内部处理器和外设之间遵循Avalon交互式总线。Avalon交互式总线在Qsys系统生成中自动完成,包括Avalon外设、Avalon信号和Avalon端口3部分[10]。

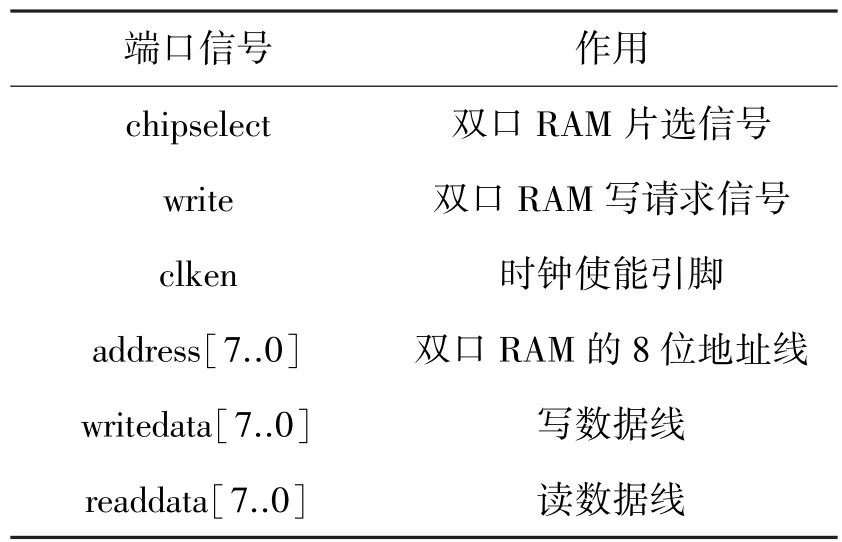

在进行Qsys系统建立、添加片上存储器外设时,将其设置为双口RAM的模式,数据宽度选取为8位数据模式,RAM大小设置为256 bits。设置完成后双口RAM的一端的地址线以及数据线自动连接到Qsys系统的Avalon交互式总线上,另一端口的数据线可以由用户分配到相应的I/O口与 DSP的EMIF接口连接。在双口RAM中的各个端口信号含义如表1所示。

表1 双口RAM各端口信号含义

3.2 双口RAM的时序仿真设计

为了使生成的双口RAM与DSP6726的EMIF接口设计时序匹配,对生成的双口RAM进行了时序仿真,如图4所示。

图4 双口RAM基本读写时序仿真

从仿真结果得出双口RAM的基本写时序为:控制chipset信号变为高电平,给出要写入的地址信号和数据信号,再给出write信号和clken信号,将要写入的数据写入到双口RAM中;双口RAM的基本读时序为:给出要读出的数据地址信号,控制chipset信号和clken信号变为高电平,在经过一段延迟时间后,数据将在readdata上进行输出。

3.3 DSP与双口RAM接口电路的设计

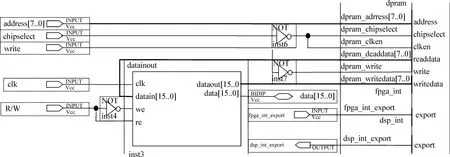

由于DSP的数据线是双向的,而Qsys生成的数据输入和输出线是分开的,所以需要加入数据方向控制电路,否则DSP将只能进行数据读操作或写操作。TMS320C6726 DSP只有一个异步片选信号CS2,而双口RAM与Flash共用外部的地址线与数据线,当DSP对Flash进行读操作时同时也对双口RAM进行读操作,这样必然导致读取的数据出错。为了不让Flash和DPRAM存储空间地址重叠,设计通过DSP的一个GPIO控制CS2片选信号。

当GPIO置高时可以读写DPRAM数据;GPIO置低时读写Flash的数据。DSP6726扩展FPGA为异步存储器的接口如图5所示。

图5 DSP6726扩展FPGA为异步存储器的接口

图6 Quartus II中双口RAM的接口电路

考虑到DSP6726扩展外部存储器的时序要求和为了匹配Avalon从外设读写时序,DSP的chipse-lect和write信号经过非门接到了DPRAM相应端口上;在数据转换电路中,通过DSP的EMRW信号对方向进行选择,EMRW信号在DSP的读数据区间呈高电平状态,在DSP的写数据区间呈低电平状态,因此将R/W信号通过非门连接到datainout模块的we端口,同时R/W信号又直接连接到re端口;clk-en引脚只需在读写周期内有效,因此直接连到DPRAM的chipselect上,接口电路如图6所示。

4 结束语

以DSP和FPGA双CPU构架为核心的导航微机系统经过调试表明,系统的性能明显优于传统的捷联导航微机系统。此导航微机系统具有体积小、功耗低、性价比高、功能扩展灵活的特点,已成功地用在基于石英音叉陀螺(微机械陀螺)的小型捷联制导系统中,出色地完成了捷联制导计算的工作。本系统的研制对于扩展捷联惯性导航系统的应用领域具有一定的积极作用。

[1]罗广红.基于 DSP/FPGA的捷联导航计算机研究[D].哈尔滨:哈尔滨工程大学,2012:2-3.

[2]刘勇.基于DSP和AVR单片机的主从式双CPU导航计算机[J].压电与声光,2003(6):456-458.

[3]张树侠,孙静.捷联式惯性导航系统[M].北京:国防工业出版社,1992:8-9.

[4]胡文彬,高延滨,许德新.新型双CPU架构的捷联惯性导航微机系统[J].应用科技,2007,34(6):23-25.

[5]高延滨,詹俊妮,何昆鹏,等.高精度石英振梁加速度计频率采样系统设计[J].应用科技,2012,39(3):61-64.

[6]陈美燕.基于FPGA+DSP的信息采集板的设计[D].成都:西南交通大学,2009:45-46.

[7]周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006:9-54.

[8]秦鸿刚,刘京科,吴迪.基于FPGA的双口RAM实现及应用[J].电子设计工程,2010,18(2):72-74.

[9]季强,刘利强.双口RAM在数据采集系统中的应用[J].应用科技,2004,31(5):22-24.

[10]刘杰.基于模型的设计——Qsys篇[M].北京:机械工业出版社,2012:33-35.

The design and implementation of navigation computer with dual CPU based on DSP and FPGA processor

GAOYanbin,LIU Huiyu,HE Kunpeng,ZHANG Xingzhi

College of Automation,Harbin Engineering University,Harbin 150001,China

In order to meet the development of the inertial system,a new kind of navigation computer with the char-acteristics of small size,low power,low cost and high performance was presented in this paper.The navigation computer system is made up of digital signal processor(DSP)chip TMS320C6726 from TI company and FPGA chip EP3C10E144A7 from Altera company.DSP is mainly responsible for the navigation calculation and data pro-cessing,and FPGA is mainly responsible for inertial measurement unit(IMU)data acquisition and interface con-trol.The microcomputer system takes advantages of fast processing speed and strong float point data processing ca-pability of TMS320C6726 and SOPC technology of FPGA.The dual-CPU can quickly transmit data through double-port RAM which is achieved by VHDL language.The operating efficiency of the navigation computer is improved.

navigation computer;DSP;double CPU;dual-port RAM;strap-down algorithm

TP273.4

A

1009-671X(2014)03-0023-04

10.3969/j.issn.1009-671X.201305025

2013-05-30.

国家自然科学基金资助项目(51309059).

高延滨(1963-),男,教授,博士生导师;

刘辉煜(1990-),男,硕士研究生.

刘辉煜,E-mail:liuhuiyu415@163.com.