集成萤火虫2号GPU的片上系统设计和实现

杜慧敏, 王涌钢, 李 涛

(西安邮电大学 电子信息工程学院, 陕西 西安 710121)

集成萤火虫2号GPU的片上系统设计和实现

杜慧敏, 王涌钢, 李 涛

(西安邮电大学 电子信息工程学院, 陕西 西安 710121)

设计一个用于图形处理的片上系统。该系统将LEON3处理器和萤火虫2号图形处理器相结合,通过AHB总线互联而成。主模块LEON3处理器通过访问分配给各个从模块地址空间,实现对从模块的控制和主从模块之间的数据通信。以OpenVX内核函数为测试用例,进行功能验证和现场可编程逻辑阵列的验证。结果表明,该系统能够正确读写数据,快速实现图像处理。

图形图像处理器;处理器;片上系统;现场可编程逻辑阵列;OpenVX

随着各个领域对图形处理性能要求的不断提高,单纯由微控制器对图形处理的嵌入式系统已经不能满足人们的要求。

目前图形处理主要通过软件或者在图形处理过程中对部分处理阶段采用硬件加速来实现。文献[1-2]通过软件在ARM处理器对图像压缩编码、图像畸变校正、图像平滑锐化、以及边缘检测等图像算法进行实现,该实现针对性较强,处理速度慢;文献[3-5]通过软件对图形处理器进行了功能建模,实现了图形处理器的各个图形管线阶段的功能,其处理速度较慢;文献[6-8]通过硬件实现了图形处理器中三角形光栅化、图形管线中几何阶段的剪裁、以及传统固定流水线结构的图形处理器,但只是对图像处理中某些阶段进行加速,整个图形处理器的处理速度较慢,而且应用范围较窄。在嵌入式系统中加入专门的嵌入式图形处理器芯片或是利用具备图形加速引擎的片上系统(System on Chip,SoC)芯片来提高图形绘制速度是研究的主要问题之一[3]。

为了实现对图形的快速处理,本文设计一个SoC系统,将LEON3[9-10]处理器和FireFly2图形处理器[11-12]相结合,完成簇控制器以及与AHB总线接口转化模块的设计与实现。利用Modelsim完成功能仿真,并通过Vivado综合实现,在包含Xilinx V7-2000t器件的FPGA开发板上完成SoC系统的FPGA验证。

1 FireFly2 图形处理器的结构

FireFly2是一种新型的多态并行阵列结构的图形处理器,可以进行线程级并行、数据级并行和操作级并行运算,能高效实现图形、图像和数字信号处理任务[13-15]。它是由16个处理单元(Processing Element, PE)互联构成一个4×4的二维阵列簇(Cluster)。

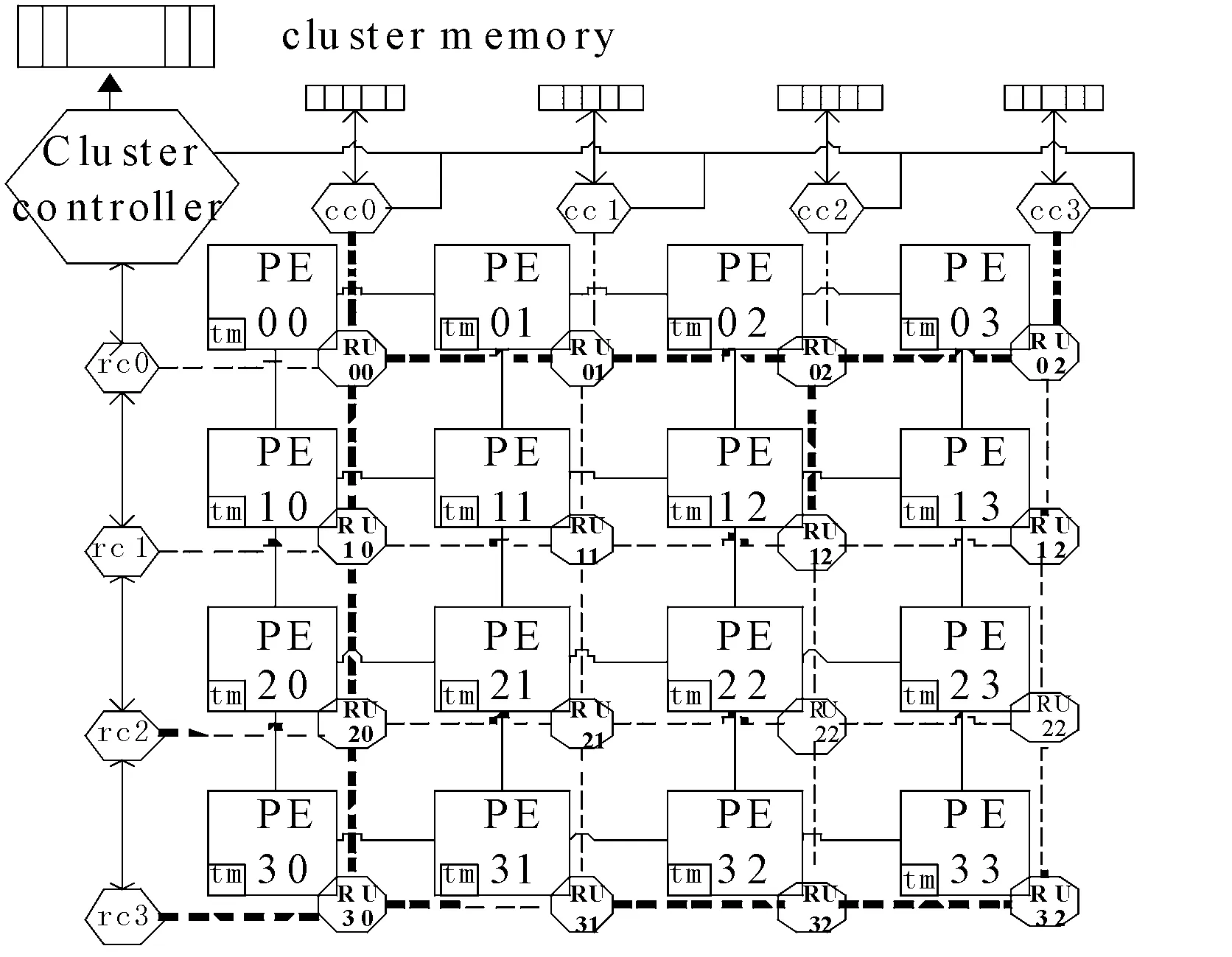

簇的结构如图1所示,这种簇的结构可以以平面结构展开,也可以构成分层次(Hierarchical)结构。

图1 FireFly2的簇结构

该结构包含簇控制器、行列控制器、处理单元、路由器和线程管理器,各模块具体实现功能如下。

(1)簇控制器(Cluster controller):实现整个簇与外部的通信即实现数据和指令的初始化,数据回收;并协调实现整个簇实现单指令多数据(Single Instruction Multiple Data,SIMD)与多指令多数据(Multiple Instruction Multiple Data,MIMD)处理模式。

(2)行控制器(Row controller,RCi):为每一行PE设计了一个行控制器,用来实现一行PE的SIMD运算,线程管理的信息配置,PE的数据和指令初始化。

(3)列控制器(Column controller,CCi):用来管理整个簇的存储,实现数据的动态加载和数据的回收。

(4)处理单元(processing element,PE):该PE具有以下特点:精简指令集(Reduced Instruction Set Computing,RISC)、四级流水线结构、具有浮点运算单元(Float Point Unit,FPU)、独立的指令和数据cache(哈佛结构)、没有寄存器操作,操作数的存取直接访问数据存储等。

(5)路由器(Router):实现路由通信。通过路由器(Router)和处理单元(PE)互联组成一个4×4阵列,如图1中虚线所示。其中还有一种通信为近邻通信,各个PE之间进行通信,如图1中PE间的实线互联。

(6)线程管理(Thread management):实现线程间的切换,一个PE最多有8个活跃的线程,当一个线程阻塞时,可以切换到其他线程去运行,充分利用了处理单元的资源。

该结构能够实现4种运行模式,分别为SIMD运行模式、MIMD运行模式、分布式指令并行模式及流处理运行模式,可以实现多种任务的混合计算,提高系统性能。

2 SoC系统整体结构

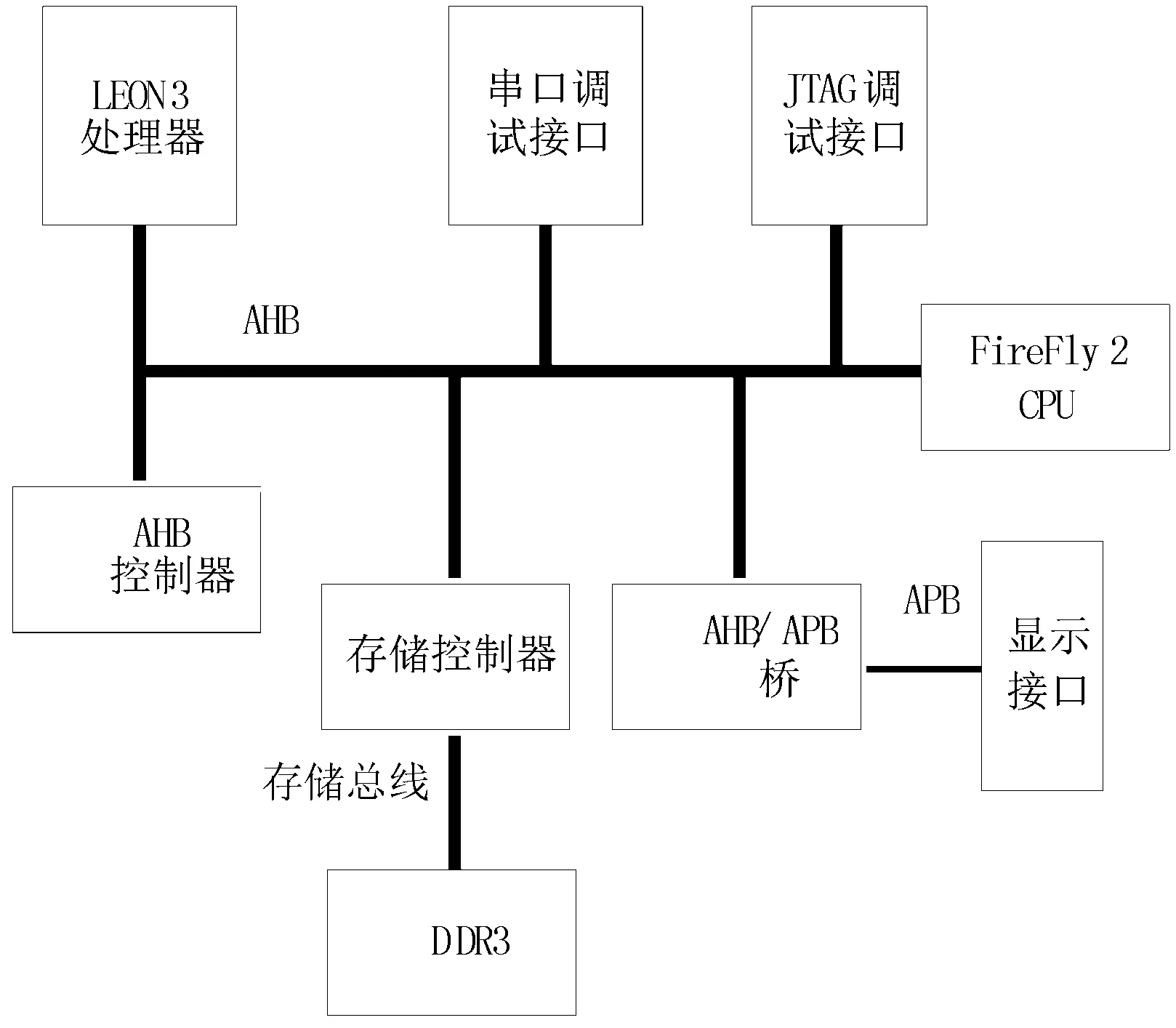

SoC系统结构主要包括LEON3处理器(主模块),FireFly2 GPU(从模块),AHB/APB片上总线(总线兼容AMBA2.0[16]标准),串口调试模块(RS232,Serial Dbg link),JTAG调试模块(主模块),存储模块(DDR3)以及显示模块(VGA,从模块)等。整个SoC系统通过AHB/APB总线互联而成。SoC系统整体结构设计如图2所示。

图2 SoC系统结构

该系统通过LEON3控制整个系统有序运行,DDR3存储LEON3的运行程序和数据;JTAG和RS232 DBG将程序和数据加载到SoC系统中,同时可在系统运行时进行调试;VGA显示处理后的图像结果;AHB控制器模块实现SoC系统高速设备的管理;APB控制器实现SoC系统低速设备的管理。

3 SoC系统的设计与实现

在SoC系统中,AHB总线和APB总线具有即插即用的特性。FireFly2在SoC系统主要实现数据的快速处理,将其定义为从模块,LEON3作为主模块来控制数据的读写。

3.1 FireFly2中簇控制器的设计与实现

FireFly2簇的输入输出数据通道控制由簇控制器实现,其结构如图3所示。

图3 簇控制器结构

由图3可知,簇控制器主要由1个数据接收控制模块(RECV_CTRL)和1个数据发送控制模块(SEND_CTRL),4个FIFO(First Input First Output)和1个RAM存储组成。

RECV_CTRL首先检测FIFO0是否为空,如果不空,则读取FIFO0中的数据并解析,如果是给簇控制器内部发送数据,则将数据写入FIFO1,并由SEND_CTRL来控制下发;如果是SIMD指令,则将数据写到RAM存储中;当RECV_CTRL检测到FIFO2不空时,则将FIFO2中的数据传送到FIFO3中,并由上位机读取FIFO3中的数据。

3.2 FireFly2与AHB总线接口设计与实现

FireFly2的数据读写接口与AHB总线接口的转化,由IO_Convert模块实现。其接口框图如图4所示。

图4 接口转换模块接口

LEON3通过32bit的地址去访问从设备,并由AHB controller解析地址来产生hsel_s信号,表示是否命中该设备;htrans信号表示主模块的传输状态,SoC系统中AHB总线使用的是NONSEQ非连续状,表示单数据发送或者突发传送的第一个数据传送,此时,与之前发送的地址和数据无关;hburst信号表示批量传送状态,SoC系统中AHB总线使用的单数据传送;hsize信号表示传送数据的大小,用字节表示,由于FireFly2处理的数据都是32bit的数据,选择4个字节的数据大小传送。

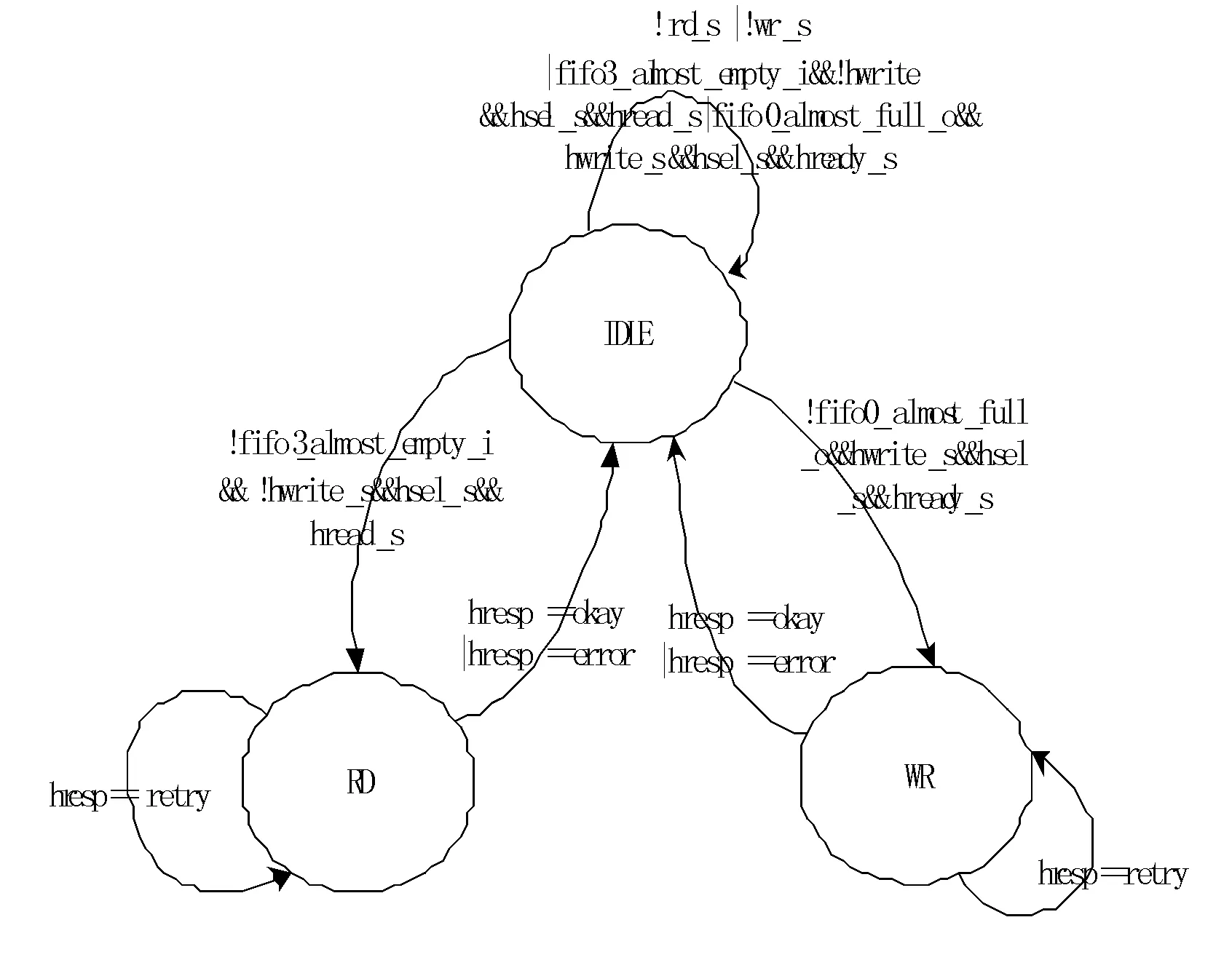

图5描述了AHB到FireFly2的接口转换状态转移。

图5 接口转换状态图

在空闲(IDLE)状态下,检测读写相关的信号,如果读有效且fifo3_almost_empty_o为低,则转到读数据(RD)状态进行操作;如果检测写信号有效且fifo0_almost_full_o为低,则转换到写数据(WR)状态进行操作。否则,继续转到IDLE状态。

在RD状态下,通过读地址和读相关信号,读取数据,读取成功后返回okay信号,表示操作结束;读取错误时返回error给LEON3进行处理。如果返回的是retry信号,则保持RD状态等待重新发送读操作的相关信息。

在WR状态下,通过写地址和相关信号进行写数据,写结束后返回okay信号,表示操作结束;写错误时返回error给LEON3进行处理。如果返回的是retry信号,则保持WR状态等待重新发送写操作的相关信息。

通过簇控制器和IO_Convert模块,可使FireFly2 GPU连接到AHB总线,与其他部件通过AHB总线互联,形成SoC系统。

4 SoC系统测试与性能分析

利用OpenVX[17]内核函数的测试用例,对设计的SoC系统进行功能验证和FPGA验证。

4.1 Modelsim 功能仿真

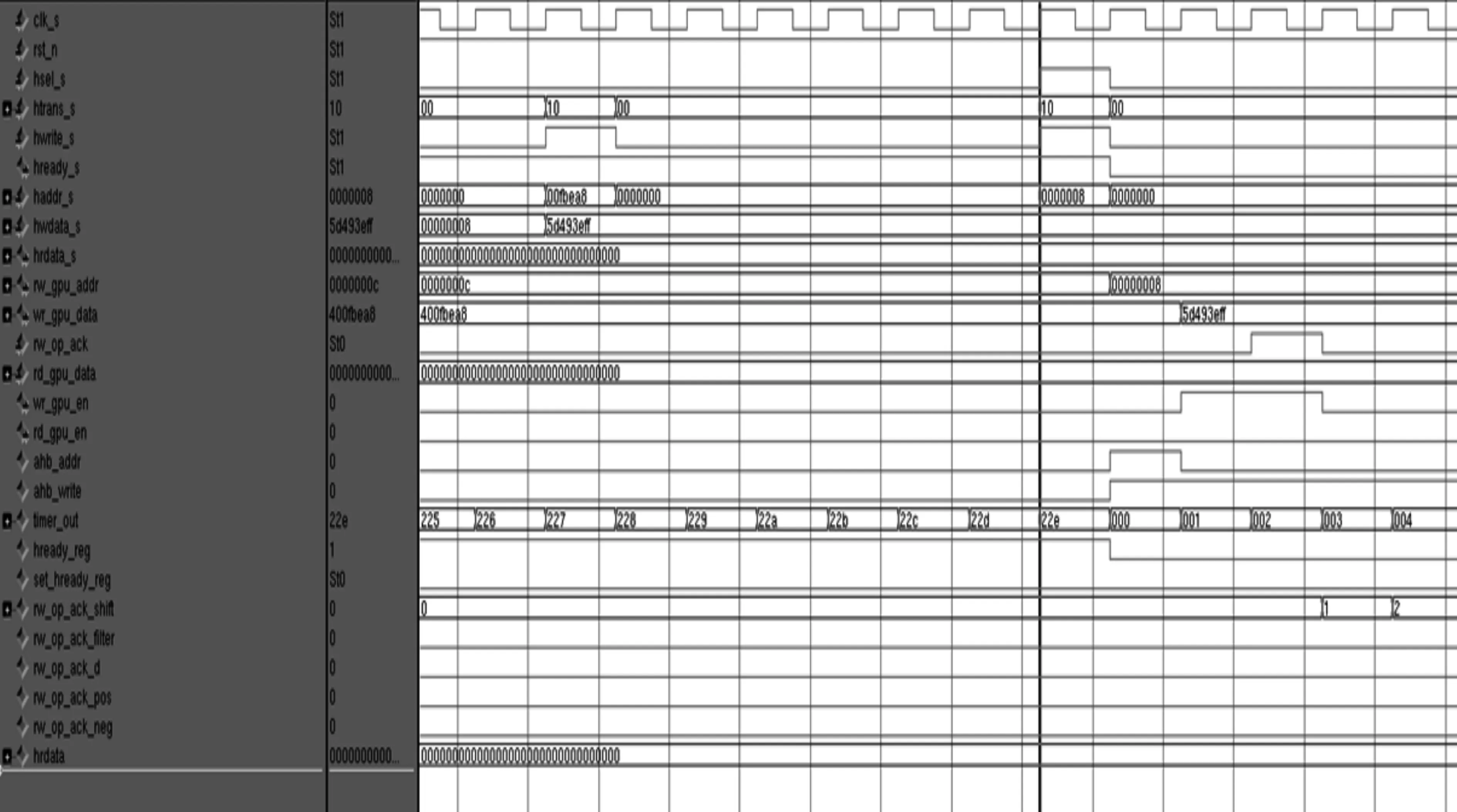

通过接口转化模块,可将LEON3发送的写数据和读数据命令发给FireFly2模块。由FireFly2的簇控制器将数据初始化到其内部各个部件或者从各部件中读取。图6是接口转化模块的功能仿真。

图6 接口转化模块的仿真

由图6可知,在hsel_s信号为高,hwrite_s信号为高,将数据写到相关的存储地址下,其地址对应的是FIFO0;同样在读数据时hsel_s信号为高,hwrite_s信号为低,将数据从相关存储地址读出,其地址对应的是FIFO3,仿真结果显示,能够正确的给FireFly2中写数据,以及对该模块的数据读取。

4.2 FPGA验证

整个SoC硬件系统如图7所示。

图7 SoC系统

该系统包括上位机主要进行程序的配置和加载;FPGA开发板实现了SoC的硬件系统;显示器完成了SoC系统计算结果的显示。通过EMU[18](Emulation Platform Controller)加载LEON3mp.bit文件,同时用GRMON2[19]加载编译过的OpenVX测试例子。

选择测试用例中的图像增强(accumulate_squared)和通道提取(channel_extracted)两个内核函数实现的图像处理例子,在FPGA上进行验证。FPGA验证结果如图8和图9所示。

(a) 原图(b) 图像增强结果

图8 图像增强的FPGA处理结果

(a) 原图(b) 红色通道

(c) 绿色通道 (d) 蓝色通道

图9 通道提取的FPGA处理结果

由图8可以看出,图8(b)比图8(a)变亮。图像增强主要实现了原始图像数据与它本身数据平方的累加,属于迭代算法,对原始图像进行增强处理。由图9可见,通道提取主要实现图像的颜色提取,由此可知系统对图像处理的结果正确。

4.3 性能分析

通过FPGA综合实现后资源占用情况如表1所示。

表1 资源占用情况

表1中块RAM的资源占用率为49%,占用块RAM的资源相对较多,而其他资源占用相对较少,这是由于Firefly2的一个主要特征是所用的存储单元统一为片上存储,对于FPGA片上存储资源占用较多。资源占用满足FPGA资源要求,系统的工作频率为100MHz,可快速进行图形处理。

5 结束语

设计了集成LEON3和FireFly2的SoC系统,对FireFly2的簇控制器以及与AHB接口转化模块进行了设计和实现。通过Modelsim功能仿真和FPGA验证,结果表明,接口转化模块的功能仿真与设计相符合,SoC系统处理图像的结果正确。整个系统频率为100MHz,资源占用率中块RAM资源占用率为49%,其余资源占用较少,满足FPGA器件对资源占用的要求,可快速进行图形处理。

[1] 蒋立丰.嵌入式图像处理系统的设计与研究[D].上海:东华大学,2013:30-42.

[2] 王学宾.基于ARM的嵌入式图像处理技术的研究[D].天津:河北工业大学,2013:28-40.

[3] 杨国东.嵌入式图形处理器的研究与实现[D].济南:山东大学,2010:29-41.

[4] 饶志恒.图形处理器的图形管线研究与实现[D].长沙:湖南大学,2011:34-43.

[5] 黄伟钿.面向移动平台的3D图形处理器的设计[D].广州:华南理工大学,2011:35-47.

[6] 黄锐.实时嵌入式图形系统的三角光栅化研究与设计[D].上海:上海交通大学,2008:33-45.

[7] 田兵.嵌入式图形处理器裁剪引擎的设计[J].计算机与数字工程.2011,39(10):161-165.

[8] 谭显强.基于FPGA的3D图形处理器IP核的设计与实现[D].南京:南京航空航天大学,2010:30-50.

[9] Gaisler A. IP Library User’s Manual 1.3.7-B4144[S]. USA:Aeroflex Gaisler,2014.

[10] Gaisler A. IP Core User’s Manual 1.3.7-B4144[S]. USA:Aeroflex Gaisler, 2014.

[11] 韩俊刚.图形处理器的历史现状和发展趋势[J].西安邮电学院学报,2011,16(3):61-63.

[12] 李涛,杨婷,易学渊.萤火虫2:一种多态并行机的硬件体系结构[J].计算机工程与科学,2014,12(2): 191-200.

[13] 李涛,肖灵芝.面向图形和图像处理的轻核阵列机结构[J]. 西安邮电学院学报,2012,17(3): 41-47.

[14] 韩俊刚,姚静,李涛,等.多态并行机上的3D图形渲染[J].西安邮电大学学报,2015,20(2):1-6.

[15] 李涛,孙建,王鹏博.基于PAAG的OpenVX核心库函数并行化实现[J].西安邮电大学学报,2015,20(2):7-10.

[16] ARM.AMBA Specification(Rev 2.0) [S]. United Kingdom: ARM,1999.

[17] Susheel Gautam, Erik Rainey. The OpenVx Specification1.0[S]. USA:Khronos Group,2014.

[18] DINI GROUP.EMU Software Manual[S]. USA:DINI GROUP,2011.

[19] Gaisler A.GRMON2 User’s Manual Version2.0.55 [S]. USA :Aeroflex Gaisler, 2014.

[责任编辑:祝剑]

An SoC design and implement which integrates Fire-fly2 GPU

DU Huimin, WANG Yonggang, LI Tao

(School of Electronic Engineering, Xi’an University of Posts and Telecommunications, Xi’an 710121, China)

A system on chip is designed in this paper for graphics processing. The system integrates FireFly2 GPU with LEON3 processors, and interconnects through AHB system bus. The master module LEON3 processor can access to each slave module by assigning address space, and control each slave module and data traffic among the main module and slave modules. OpenVX kernel is used as an assembly language in the test case to carry out functional simulation and FPGA verification. Results show that the system can correctly read and write data and quickly realize image processing.

GPU, CPU, SoC, FPGA, OpenVX

2014-12-01

国家自然科学基金重大项目(61136002);教育部科学研究计划重点项目(2111180)

杜慧敏(1966-),女,博士,教授,从事计算机体系结构、计算机图形、大规模集成电路的研究。E-mail: 228660529 @qq.com 王涌钢(1988-) ,男,硕士研究生,研究方向为计算机体系结构、计算机图形。E-mail:leopardwyg@163.com

10.13682/j.issn.2095-6533.2015.03.006

TN492

A

2095-6533(2015)03-0039-05