高速差分传输线的设计

巩稼民, 侯 斌, 杨 祎

(西安邮电大学 电子工程学院, 陕西 西安 710121)

高速差分传输线的设计

巩稼民, 侯 斌, 杨 祎

(西安邮电大学 电子工程学院, 陕西 西安 710121)

针对高速印制电路板设计中存在的差分线反射问题,设计一种参数设计完全对称与传统端接相结合的差分传输线拓扑结构。依据差分线理论,得到差分线的设计参数,量化分析了主芯片TI8168与内存芯片DDR3互连中时钟信号差分传输的端接方法和端接参数。仿真结果表明,该结构可抑制差分信号的反射和差分信号引起的共模信号的反射,提高了信号传输质量。

差分传输线;信号完整性;反射;端接

信息量的不断提升以及高速电路的飞速发展,对高速信号的传输提出了更多要求。差分传输线独特的传输特性使它在高速信号领域得到了广泛的应用,但其在高速电路板设计中的时延和端接等问题,又对信号完整性产生了影响[1-3]。

第三代双倍速率同步动态随机存储器(Double Data Rate - Ⅲ,DDR3)能够支持800~1 600 Mbps的数据传输,为满足更高的信号速率、大信息量和低电压的需求,DDR3的时钟信号的设计就面临越来越多的挑战。DDR3的外部时钟信号一般是用差分线来进行传输,差分线具有很强的抗干扰和抗噪声的能力[4-5]。差分线在进行信号传输时会产生差分信号和共模信号的反射等问题[6-7]。目前,为抑制高速电路板中差分传输线的差模信号和共模信号的反射,均采用T型端接和∏型端接。但是,T型端接和∏型端接不仅布线困难、电路复杂,负载大、功耗大,影响驱动能力,而且在传输线设计中要求等长,会走蛇形线,传输线的特性阻抗就会发生变化,在设计中不好控制,从而影响信号质量。

本文在分析差分信号的传输原理基础上,针对高速印制电路板( Printed Circuit Board, PCB)设计中存在的差分线反射问题,通过分析PCB布线中差分阻抗及端接电阻的设计并采用SigXplorer软件进行仿真,量化分析了时钟信号差分传输的端接方法和端接参数,提出了一种实用可行的解决差分线反射问题的方法。

1 高速差分传输线

1.1 差分信号理论

在差分互连中,主要使用两条传输线来传输信号,即差分驱动器有两个输出端,并且同时输出信号。

差分驱动器的两个信号极性相反,即正极性输出端信号为V1,负极性输出端信号为V2,则差分信号可以定义为[8]

Vd=V1-V2。

差分传输正是利用Vd来传输信息,接收端是利用感受到的差分信号的电压波形来提取信息。而同时接收端还能感受到另一种信号,即共模信号。共模信号可以定义为[8]

任何两个单端信号的组合都可以用差分信号与共模信号的组合来表示,即有[8]

其中Va和Vb均为任意的单端信号,Vc为共模信号,Vd为差分信号。

任何两个信号都可以用差分分量和共模分量来表示。如果只考虑差分分量时,则电路只含有奇模阻抗Zo,则此时差分阻抗Zd的阻值为[8]

而只考虑共模信号时,则电路只含有偶模阻抗Ze,而共模阻抗Zc的阻值为[8]

1.2 差分信号的反射

信号的反射是信号完整性的主要问题,与传输线的阻抗密切相关。在单个传输线中,当信号沿着传输线传输时,若信号在传输线上所感受到的瞬时阻抗恒定不变时,信号不会发生反射;然而,若传输线中的特性阻抗发生了突变,则信号将会被反射,如图1所示。阻抗突变表现在走线拐弯、过孔、封装、分支线等传输路径上的任何地方。由于差分线是由两条传输线耦合得到,所以差分信号的反射与单个传输线的反射原理相同,当差分阻抗发生变化时,会产生信号反射。

图1 阻抗突变

2 差分线端接电路设计

基于主频为1 G的高速图像信息采集与存储的六层PCB板设计,主要对主芯片8168与DDR3芯片之间的时钟信号进行研究设计,并采用差分线来传输时钟信号。为了保证信号完整性,在使用差分信号传输时,一般把差分阻抗控制在100Ω左右,而差分线的等长、线距、线宽以及相邻介质的介电常数等都会影响差分阻抗,从而影响参数设计和信号质量,所以必须对差分传输线的特性和终端负载进行分析和设计。

2.1 差分阻抗的参数设计

根据板子的材料、层数和制作工艺,选取的阻抗计算模型,表层单端微带线的横截面如图2所示,其参数如表1。由于差分阻抗的计算必须基于单端传输线特性阻抗计算的基础之上,因此,差分传输线的横截面如图3所示,参数如表2所示。根据以上数据,采用专业的阻抗计算软件Polar Si9000求解器计算传输线的阻抗,求得单端传输线的特性阻抗Z0为65.15 Ω,差分阻抗Zd为105.2 Ω,进而求出了信号在频率为450 MHz时的差分线奇模阻抗Zo和偶模阻抗Ze分别为53.6 Ω和77.6 Ω。

图2 表层微带线横截面

表1 表层微带线的参数设置和阻抗计算

图3 耦合的表层微带线横截面

表2 耦合的表层微带线的参数设置和阻抗计算

2.2 终端电阻的确定

当传输线的特性阻抗等于终端负载的电阻值时,就可以实现阻抗匹配,抑制反射,将阻抗匹配的这种方式称为信号的端接。差分信号的端接方式有:T型端接、∏型端接和传统端接[9],由于T型端接和∏型端接的设计原理相同,以T型端接为例,如图4(a),端接电阻R1和R2分别为[9]

R1=Zo,

(1)

(2)

差分信号感受到的阻抗为两个R1的串联即2Zo,刚好等于差分阻抗Zd。共模信号感受到的阻抗为两个R1并联后再和R2串联,阻值为0.5Ze,刚好是等于共模阻抗Zc,所以此时差分信号与共模信号均达到了阻抗匹配,理论上不会发生反射,从而保证了信号的质量。

而对于传统的端接,如图4(b),端接电阻R3为[9]

R3=2Zo。

(3)

差分信号到达端接位置时感受到的阻抗是R3,即2Zo,刚好是等于差分阻抗Zd,此时差分信号就不会发生反射。在此种端接方式下,对于共模信号相当于末端开路[8],所以传统端接没有消除共模信号的反射。因此,差分传输线为消除反射一般采用T型端接和∏型端接。若输入端只输入差分信号,传统端接会导致差分信号在传输的过程中出现共模信号的反射,影响信号质量。

图4 差分互连的端接方式

3 差分传输电路的仿真

3.1 IBIS模型和仿真参数的设置

IBIS主要是描述器件的驱动源输出阻抗、上升/下降时间及输入负载等参数,可以用它来对PCB板进行信号完整性仿真和时序分析。本文的仿真是基于所用芯片的IBIS模型进行分析研究。根据应用需求,设置仿真参数为:传输线类型为理想的耦合微带线,最小耦合长度为300 mil,最小线距设置为0.1 mm,允许的时延长度55~75 mm,传输速率为5 560 mil/ns,信号仿真频率450 MHz,信号的上升时间为0.151 ns。在整个板子的差分线仿真设计中,将差分驱动端的信号设定为极性相反、振幅相同的信号特性,即差分信号,并且两条传输线设置等长。

3.2 仿真结果分析

(1)差分传输线的无端接仿真分析

建立8168芯片与DDR3芯片差分互连的拓扑结构如图5,仿真结果如图6。

从仿真结果可以看出,DDR3的工作电压为1.5 V,由于发射端的信号虽极性相反,但是信号的振幅为正的,所以差分信号引起的共模信号的电压为750 mV。图6中,短线是指差分信号,实线是指差分信号引起的共模信号,点划线与虚线是指接收端的信号,从图中明显可以看出接收端信号的过冲是 412.153mV ,噪声容限是372.11mV。差分信号的过冲是803.964mV,噪声容限是754.16mV,信号的反射较严重,有振铃,其过冲已经高于噪声容限,信号质量比较差,不利于信号的接收。

图5 差分传输线无端接的拓扑结构

图6 差分传输线无端接的信号仿真

(2)差分传输线的T型端接仿真分析

T型端接的拓扑结构即参数如图7所示,仿真结果如图8,其中R1和R2分别是由式(1)和式(2)得到。

对比图6和图8,图8中由于端接电阻与传输线特性阻抗相匹配,差分信号的反射得到了抑制。但是接收端的信号幅度降到0.82 V左右,信号的高电平已经降到高门限下面,无法判决信号的高低电平,这是因为端接电阻导致了负载功耗增大,从而拉低电平导致误码增大。因此,虽然T型端接有较好的信号传输质量,但是在实际应用中会导致信号电压的大幅降低。

图7 差分传输线T型端接的拓扑结构

图8 差分传输线T型端接的信号仿真

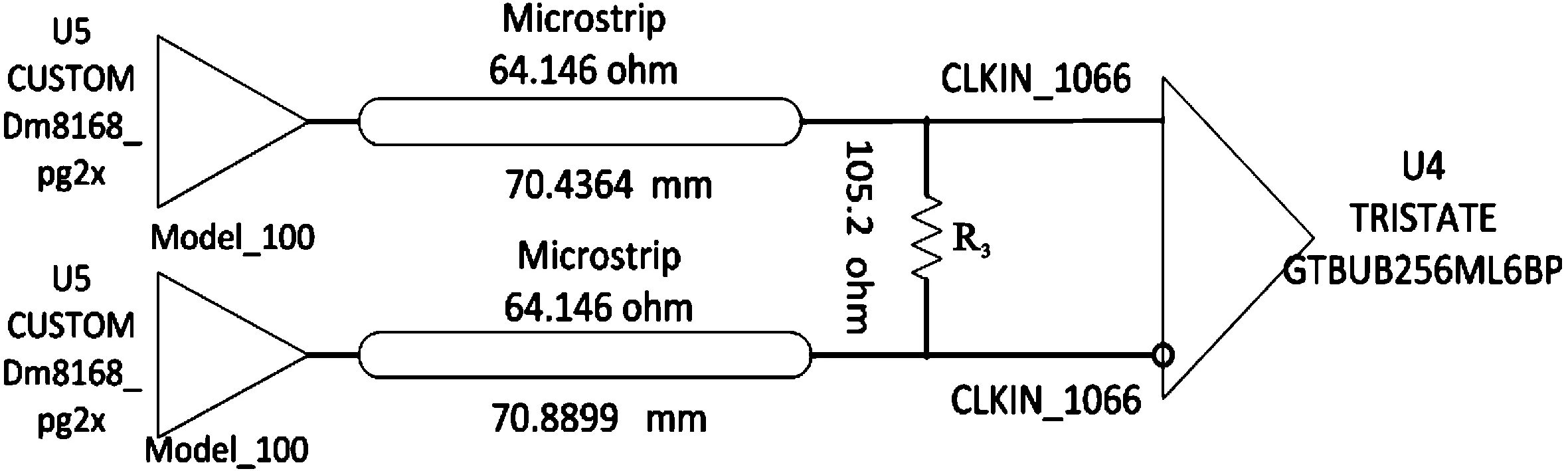

(3)对称设计的传统端接仿真分析

在图8中,由于T型端接电路过于复杂,并且传输线的等长设置导致布线需为蛇形线,从而导致差分传输线的特性阻抗出现突变,端接参数修改困难。因此通过严格控制差分线等长设计,根据实际布线长度选择端接电阻,采用传统端接方法,拓扑结构如图9所示,仿真结果如图10,其中R3可由式(3)得到。

图9 对称设计的传统端接的拓扑结构

图10 对称设计的传统端接的信号仿真

比较图6和图10,图10中差分信号的反射都得到了抑制,这是由于端接电阻与差分传输线的特性阻抗相匹配,而差分信号引起的共模信号的反射被抑制是由于差分线的等长设置和差分信号的完全对称,图10中的两种反射被抑制,振铃进而减小。比较图8和图10可以看出,图10中接收端信号的过冲是37.002mV,噪声容限是197.92mV,差分信号的过冲是73.688mV,噪声容限是395.068mV,图10中信号的噪声容限相对较大,优于图8,过冲也较小,而且信号有较好的高低电平,有利于信号的接收。比较图7和图9这两种拓扑结构,当差分传输线的特性阻抗突变时,图9拓扑结构的端接电阻易于调整,并且电路设计简单。

4 结束语

针对高速集成电路设计中存在的信号完整性的问题,通过讨论基于8168芯片与DDR3芯片时钟信号互连中差分传输线的阻抗匹配导致的反射问题,提出一种适用于工程应用的差分传输线拓扑结构和差分互连端接参数设计方法。仿真结果表明,差分传输线的T型端接电路过于复杂、功耗过大、噪声容限过小,而且传输线的等长设置导致布线为蛇形线,进而差分传输线的特性阻抗出现突变,所以信号波形不理想。而对称设计传统端接的拓扑结构,只要保证差分传输线上只为差分信号且信号传输线等长时,其既可抑制差分信号引起的共模信号的反射和差分信号的反射,又有较大的噪声容限,提高信号传输质量,并且此结构的电路实现简单,参数设计及修改易实现。

[1] Eudes T, Ravelo B, Lacrevaz T, et al. Fast estimation of high-speed signal integrity for coupled PCB interconnects[C]//2013 17th IEEE Workshop on Signal and Power Integrity. Paris: SPI, 2013:1-4.

[2] ZHOU Xiquan, HUI Pengfei, MIAO Fengjuan, et al. High-speed signal transmission on signal integrity analysis[C]//Proceeding of 3rd International Conference on Future Biomedical Information Engineering.Qiqihar:IEEE,2010: 240-242.

[3] Chen Xueping. Analysis and application for integrity of PCB signal[C]//2010 2nd IEEE International Conference on Information and Financial Engineering (ICIFE). Chongqing:IEEE, 2010:328-331.

[4] Shiue Guang-Hwa, WU Ruey-Beei.Reduction in reflections and ground bounce for signal line over slotted power plane using differential coupled microstrip lines[J]. IEEE Transactions on Advanced Packaging, 2009,32(2) : 581-588.

[5] Frederic B, Evelyne C. Crosstalk in balanced interconnections used for differential signal transmission[J].IEEE Transactions on Circuits and Systems I: Regular papers, 2007,54 (7) : 1562-1572.

[6] 郝为强.差分线阻抗控制与匹配的HyperLynx仿真分析[J].印刷电路信息,2006(11):41-43.

[7] 张超,余综.基于DDR3系统互联的信号完整性设计[J].计算机工程与设计,2013,34(2):616-622.

[8] 于争.信号完整性揭秘[M].北京:机械工业出版社,2013:219-229.

[9] 周润景, 苏良碧. Cadence高速电路板设计与仿真:信号完整性与电源完整性仿真[M].北京:电子工业出版社,2011:243-279.

[责任编辑:祝剑]

Design of the high-speed differential transmission line

GONG Jiamin, HOU Bin, YANG Yi

(School of Electrical Engineering, Xi’an University of Posts and Telecommunications, Xi’an 710121, China)

A differential transmission line topology of the completely symmetrical design parameters combining with the traditional termination is presented for differential line reflection problems existing in the high-speed PCB design. Based on the differential line theory, the design parameters of differential lines are

. The termination method and the termination parameters of differential clock signal transmission based on TI8168 and DDR3 chips are quantitatively analyzed. Simulation results show that the topology can effectively inhibit the reflection of the common-mode signal caused by differential signal and the differential signal, and improve the signal transmission quality.

differential transmission line, signal integrity, reflection, termination

2014-11-12

国家高技术研究发展计划( 863 计划) 资助项目(2013AA014504); 西安邮电大学2013年研究生创新基金资助项目(ZL2013-22)

巩稼民(1962-),男,博士,教授,博导,从事电子技术研究。E-mail:gjm@xupt.edu.cn侯斌(1989-),女,硕士研究生,研究方向为电子技术。E-mail:houbin890920@126.com

10.13682/j.issn.2095-6533.2015.02.009

TN

A

2095-6533(2015)02-0041-06