基于FPGA多通道多带宽多速率DDC设计

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

由于日益严峻的目标环境和电磁环境的挑战,现代雷达必须具备高精度、多功能、多波束、多目标处理、抗干扰、自适应和目标识别等功能,数字阵列雷达是一种接收和发射都采用数字波束形成技术的全数字阵列雷达,满足现代雷达的要求[1]。数字阵列雷达的核心内容之一是单元级回波信号中频或射频数字化后,在数字域进行幅/相加权实现接收数字波束形成,基于多通道数字化接收机的数字阵列模块是数字阵列雷达的关键模块。

数字阵列模块是一种采用集成化和数字化技术,将射频前端、分布式时钟本振分配、分布式电源、数字化收发等一体化设计,完成雷达单元级、多通道回波信号数字化收发、预处理和传输的新型多功能模块[2]。

中频/射频数字化接收机通过高速ADC直接对中频或射频模拟信号进行数字化,再对中频或射频数字信号通过DDC处理获得与信号带宽匹配的数字基带信号。目前DDC处理可以采用商用ASIC芯片来实现[3-4],也可以通过基于FPGA的IP核来实现[5]。当前随着雷达多功能一体化应用的需求以及雷达研制周期缩短的迫切需求,DDC处理基本上采用基于FPGA来进行实现,以灵活适应数字阵列雷达多功能带宽、多采样率、多通道一体化设计的需求。

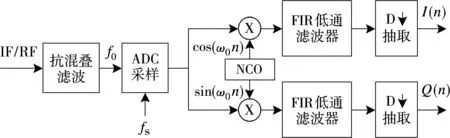

1 多通道多带宽多速率DDC方案设计

1.1 数字下变频处理概述

模拟中频信号可以表示为

式中,f0为中频/射频频率,A(t)和Φ(t)为幅度调制和相位调制信息。

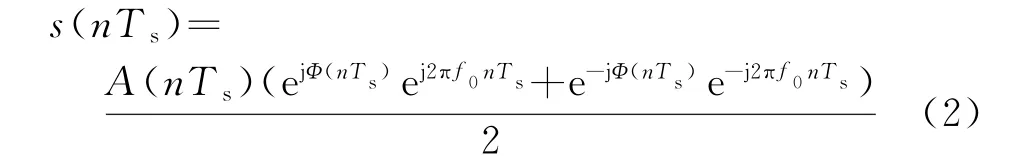

对应离散数字中频信号为

式中,Ts=1/fs为转换器的转换周期。

上式乘以数字本振信号e-j2πf0n=e-jω0n得到数字混频输出:

通过低通滤波滤除e-j2π2f0n高频成分以及带外干扰噪声得到基带信号:

与上述公式推导相对应的常规数字下变频处理的实现结构如图1所示。

图1 常规DDC处理功能框图

DDC处理包括数字混频和后续抗混叠低通匹配滤波抽取处理,实现高采样率数字中频/射频实信号到与信号带宽相匹配的低采样率基带I/Q复信号的变换,其中低通匹配滤波抽取处理是典型的数字多速率信号处理[6-7]。根据并行处理的通道数、信号带宽的数量和对应的抽取比、采样率与信号带宽的比值,DDC滤波抽取处理需要采用不同的类型、实现结构、阶数和级联方式来实现。

DDC处理在实现采样率变换、高频成分抑制、带外干扰抑制的同时可以获得信噪比处理得益或过采样得益,具体信噪比得益大小如式(5)所示(其中BW为信号带宽):

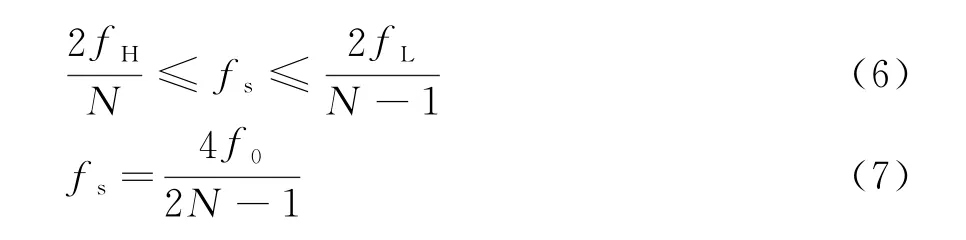

1.2 数字下变频处理实现结构

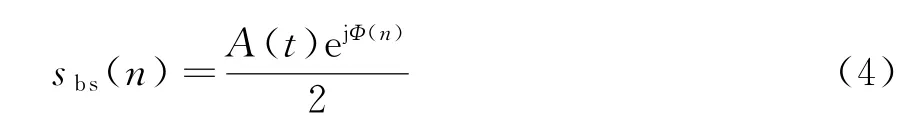

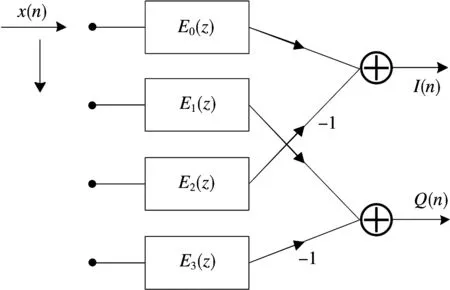

常规低通滤波DDC处理实现结构是采用图2所示的低通滤波结构来实现,即数字混频后对I/Q两路信号进行实数低通滤波处理,再抽取获得匹配采样率,由于信号复数表示采样率可以降为实数的一半,因此DDC处理抽取比至少为2。当ADC采样满足采样定理(式(6))同时信号中心频率满足(式(7))时采样为最佳采样:

满足最佳采样定理的DDC处理数字混频处理数字本振e-j2πf0n退化为抽取和符号变换,此时DDC处理可以采用如图2所示的多相时延滤波法[8]简化结构来实现。该结构混频变成符号变换后直接抽取处理,抽取造成的I/Q时延通过设计一个原型滤波器,对该滤波器进行1/4抽取,获得4个多相子滤波器,间隔选择两相分别对I/Q子路滤波,实现半个样本点延迟校正和低通滤波处理。

图2 多项时延滤波法DDC处理结构

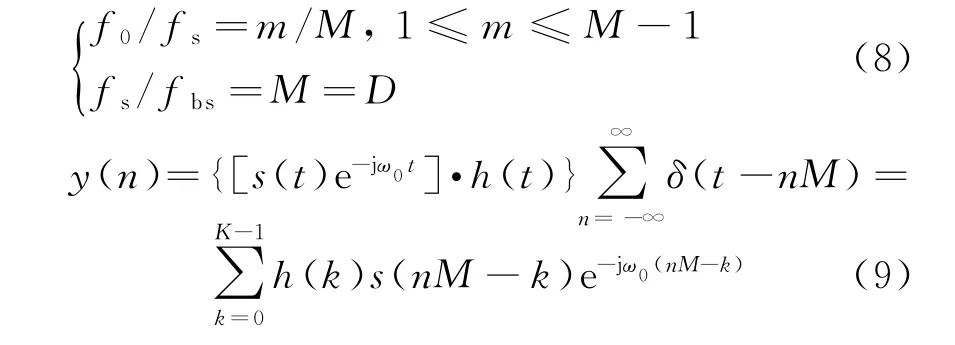

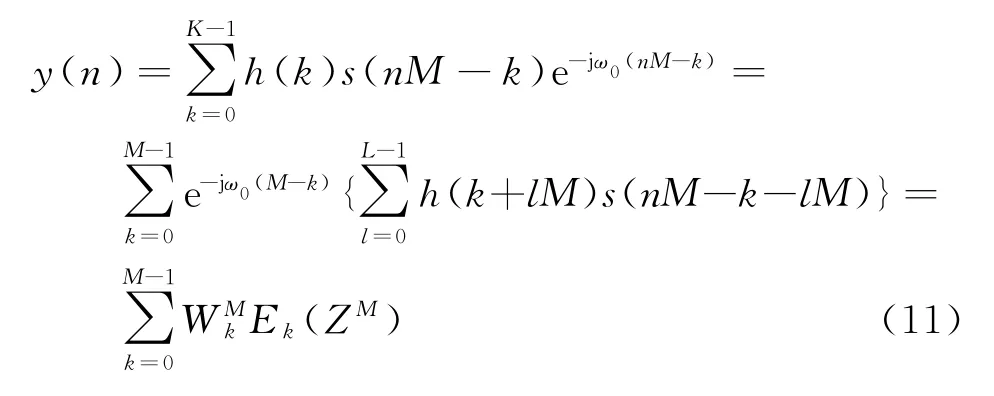

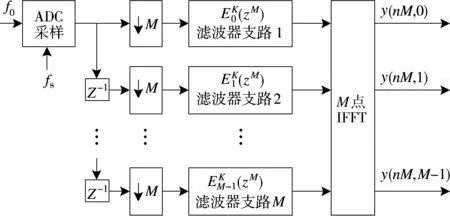

当信号的中频频率f0、采样频率fs和基带输出采样率fbs、抽取比D和NCO周期M满足特定关系式(8)时,可以采用混频后置多相滤波[6,9]高效DDC处理结构来实现。常规采样/混频/滤波/抽取DDC输出如下所示:

式中,h(t),t=0,1,…,K-1为FIR滤波器冲击响应。满足式(8)的数字本振序列可表示为

滤波器设计时系数个数可分解为K=M·L,通过推导可以获得DDC输出为

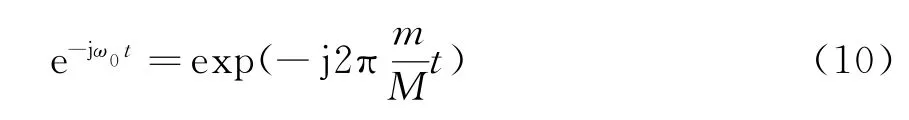

通过选择合适的中频、采样频率抽取比和滤波器系数,保证数字本振周期和抽取比相同,分配到每个多相滤波器支路上的本振信号为常数,因此混频可以放到多相滤波后面,整个DDC实现结构变成采样/抽取/多相滤波/数字混频,功能框图如图3所示。

图3 混频后置多相滤波高效DDC实现结构

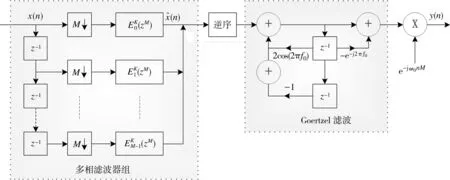

混频后置多相滤波高效DDC实现结构要求中频或射频信号中心频率为基带输出信号采样率的整数倍(fs=mfbs),通过低通滤波和后续复数相位旋转实现频谱搬移和分离混叠。当需要多个子带同时DDC输出时共用滤波器后接多个并行复数相位旋转即可,当通道数为M=log2N时,滤波后的相位旋转多信道输出可以通过IFFT/IDFT来实现[10],具体实现结构如图4所示。

图4 基于IFFT实现的混频后置多信道器

混频后置多相滤波高效DDC实现结构的优点是:1)滤波与混频在低的数据率一端处理,降低了处理速度要求;2)滤波处理在混频前和ADC后实现,为实数滤波,运算量和资源降低一半;3)对于多信道、滤波器组或信道化应用,所有信道共用一个滤波器,后接一组、多组或IFFT复数相位旋转处理可以获得不同子带同时下变频输出。

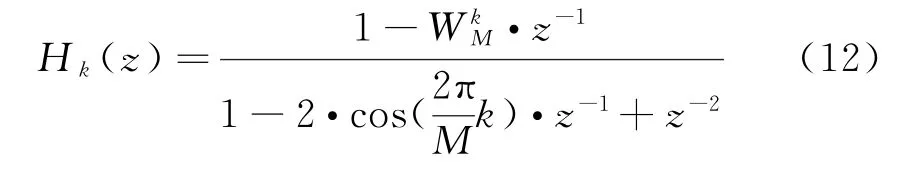

混频后置多相滤波高效结构只能针对固定位置中频信号的DDC处理,对于对抗应用会造成盲区,基于Goertzel算法改进的混频后置多相滤波结构可以实现任意频率位置信号的DDC高效处理[11]。传统Goertzel算法可以实现均匀分布的频率点处的DFT/IDFT处理,通过引入Goertzel滤波概念可以获得频带内任意频点的DFT/IDFT值,Goertzel滤波器传递函数为

根据Goertzel滤波器传递函数可以获得其直接实现形式,基于Goertzel算法改进的混频后置多相滤波结构如图5所示。

图5 基于Goertzel滤波高效DDC实现结构

该DDC处理结构特点是:1)继承了混频后置多相滤波结构所有优点;2)通过Goertzel滤波器精确调谐实现无盲区接收;3)该结构包括多相低通滤波、Goertzel滤波和移相处理,通过一定运算量增加换取混频序列频点位置的灵活性。

对于GHz高速宽带DDC处理,FPGA无法在采样频率的速度下直接处理,并且抽取后的采样率也超出FPGA处理能力的情况下可以采用广义多相滤波结构[12]来实现。该结构通过对常规多相滤波在频域上进行推导获得了并行实现的广义多相滤波结构,可以根据具体应用进行速度与资源的平衡来设计宽带并行DDC处理。

常规DDC处理整个链路抽取比为整数,因此可以通过单级或多级抽取滤波实现,但是对于通信应用、对抗/成像等宽带应用情况下存在抽取比为分数的情况,这时需要通过数字重采样滤波结构[13]来实现DDC处理,该结构通过将内插镜像抑制滤波和抽取抗混叠滤波复用,通过选择合适的滤波器阶数以及结构变换来获得高效实现。

1.3 多通道多带宽多采样率DDC处理实现方案

本文论述的DDC设计针对的应用情况主要如下:

1)并行通道数:16;

2)信号带宽:21MHz,5MHz,1MHz(5个并行子带),0.2MHz;

3)采样率:120MHz,中频270MHz。

该采样系统满足最佳采样定理,21MHz带宽可用于高分辨测距、5MHz带宽可用于高精度跟踪、1MHz带宽用于高效搜索(多个子带用于系统资源优化)、0.2MHz带宽用于连续波高精度测速,具体频带分布如图6所示。

图6 频带分配示意图

DDC处理需要根据系统工作模式输出不同带宽和采样率的多通道并行基带I/Q信号,对带外干扰进行抑制并获得相应过采样处理信噪比得益,同时保证FPGA资源利用最优化,根据采样率、中频频率、信号带宽和抽取比,以及DDC常用处理结构,该多带宽、多采样率单个通道DDC处理实现方案如图7所示(包括每种带宽对应的采样率)。

图7 多带宽、多采样率DDC处理实现方案

第一级滤波抽取获得宽带I/Q信号,根据抽取比为4,同时满足式(8)的要求,因此图4对应的实现结构可以简化为图8所示。

图8 简化最佳采样混频后置DDC处理

第二级5 M Hz带宽信号在前级基础上级联一级多相抽取滤波器来实现,第三级1MHz带宽在5MHz基础上再级联一级多相抽取滤波器实现,由于是同时并行5个子带输出,因此可以采用图4所示结构,将复数相位旋转变成5个并行结构即可。16通道并行设计需要考虑滤波器系数ROM表、相位旋转因子等共用设计以减少资源占用。

2 多通道多带宽多速率DDC仿真设计

DDC处理仿真设计主要包括基于MATLAB的仿真设计以及基于RTL语言的FPGA仿真设计两个方面,以获得满足性能指标要求、FPGA资源要求的DDC设计。

DDC处理MATLAB仿真设计可以通过点频测试激励验证DDC处理级联滤波器性能,包括DDC处理镜像抑制度、带外干扰抑制、SNR得益等,通过有带宽测试信号如线性调频信号验证带内特性如起伏、线性度等指标。

DDC仿真设计的一个重点内容是数字滤波器仿真设计[14],雷达DDC处理需要采用一些高效的线性相位FIR滤波器来实现,包括常规FIR滤波器、半带滤波器、L带滤波器、CIC滤波器等,滤波器设计可以利用MATLAB软件自带的FDATOOL或其自带的函数来设计。具体滤波器阶数的选择、是否多级级联实现、级联方式以及各级滤波器类型选择需要根据采样率、带宽、抽取比、带内纹波和带外干扰抑制度要求等来综合考虑;对于一些特殊应用场合需要考虑采用一些特殊滤波器来进行设计,如应用于米波雷达的干扰环境比较恶劣的情况下,存在密集干扰以及邻近干扰频率干扰抑制的滤波器设计[15],基于半带滤波器或互补滤波器的频谱屏蔽滤波器技术[16]可以应用于该场合,该类型滤波器可以实现陡峭的过渡带同时计算复杂度增加不多。

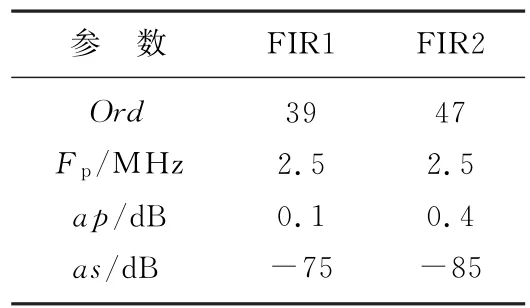

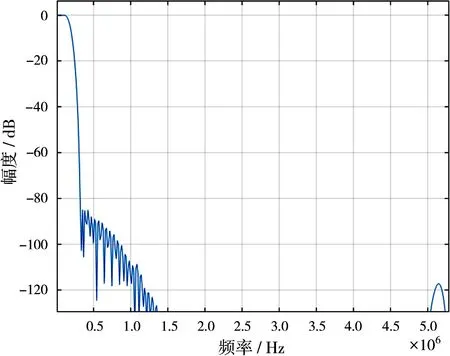

根据设计方案,整个多带宽、多通道、多采样率DDC处理采用三级滤波器来实现,每一级滤波器系数根据系统工作模式动态加载以适应不同带宽和采样率的需求。第一级实数滤波处理获得宽带21MHz采样率30 MS/s基带I/Q数据,仿真滤波器如表1所示。仿真结果如图9~11所示。

表1 21MHz带宽滤波器设计

图9 输入数字中频信号270.1MHz频谱

图10 21MHz带宽滤波器响应

图11 21MHz带宽DDC输出频谱

第二级滤波器获得5MHz带宽5 MS/s采样的基带I/Q信号,滤波器设计如表2所示,仿真结果如图12~13所示。

表2 5MHz带宽滤波器设计

图12 5MHz带宽滤波器级联响应

图13 5MHz带宽DDC输出频谱

第三级滤波器以及后续并行复数相位旋转获得5路并行1.25 MS/s的基带I/Q数据,对应带宽分别是1MHz和0.2MHz。具体滤波器设计如表3~4所示。仿真结果如图14~17所示。

表3 1MHz带宽滤波器设计

表4 0.2MHz带宽滤波器设计

图14 1MHz带宽滤波器级联响应

图15 1MHz带宽DDC输出频谱

图16 0.2MHz带宽滤波器级联响应

图17 0.2MHz带宽DDC输出频谱

基于FPGA的DDC仿真设计另外一个方面的主要内容是基于Verilog语言的RTL级实现,重点需要考虑高效算法实现结构、速度与硬件资源间的平衡、FPGA特定资源的映射等方面。本文论述的DDC实现基于ALTERA公司StratixIV系列的FPGA来实现,主要设计考虑包括:整个DDC处理基于统一的120MHz时钟来实现;滤波器结构采用多相滤波器结构,考虑时间复用以降低乘法器和逻辑资源;滤波器系统动态更新降低并行滤波器数量;采用乘加DSP处理结构最小化FPGA乘法器资源的利用;高抽取比情况下的滤波器采用基于FPGA内容DPRAM来实现FIR滤波器移位寄存器降低寄存器资源利用等。图18给出了基于FPGA内部资源DPRAM和多相结构实现FIR滤波器的功能框图。

图18 基于DPRAM多相FIR滤波器实现

最终RTL级仿真实现结果与MATLAB仿真结果对比一致,同时资源满足系统设计需求即可通过DDC设计仿真。

3 多通道多带宽多速率DDC工程实现

3.1 基于FPGA的DDC处理工程化实现

根据前述DDC处理方案,设计了一个16通道并行数字接收机,模拟抗混叠滤波器为带宽21MHz、中心频率270MHz的固定带通滤波器,通过数字DDC处理获得4种带宽/3种采样率基带I/Q信号输出,同时通过DDC处理获得相应带宽对应灵敏度和瞬时动态。具体实现ADC选择凌特公司八通道并行14位ADC芯片,FPGA选择ALTERA公司Stratix IV系列EP4SGX180芯片。

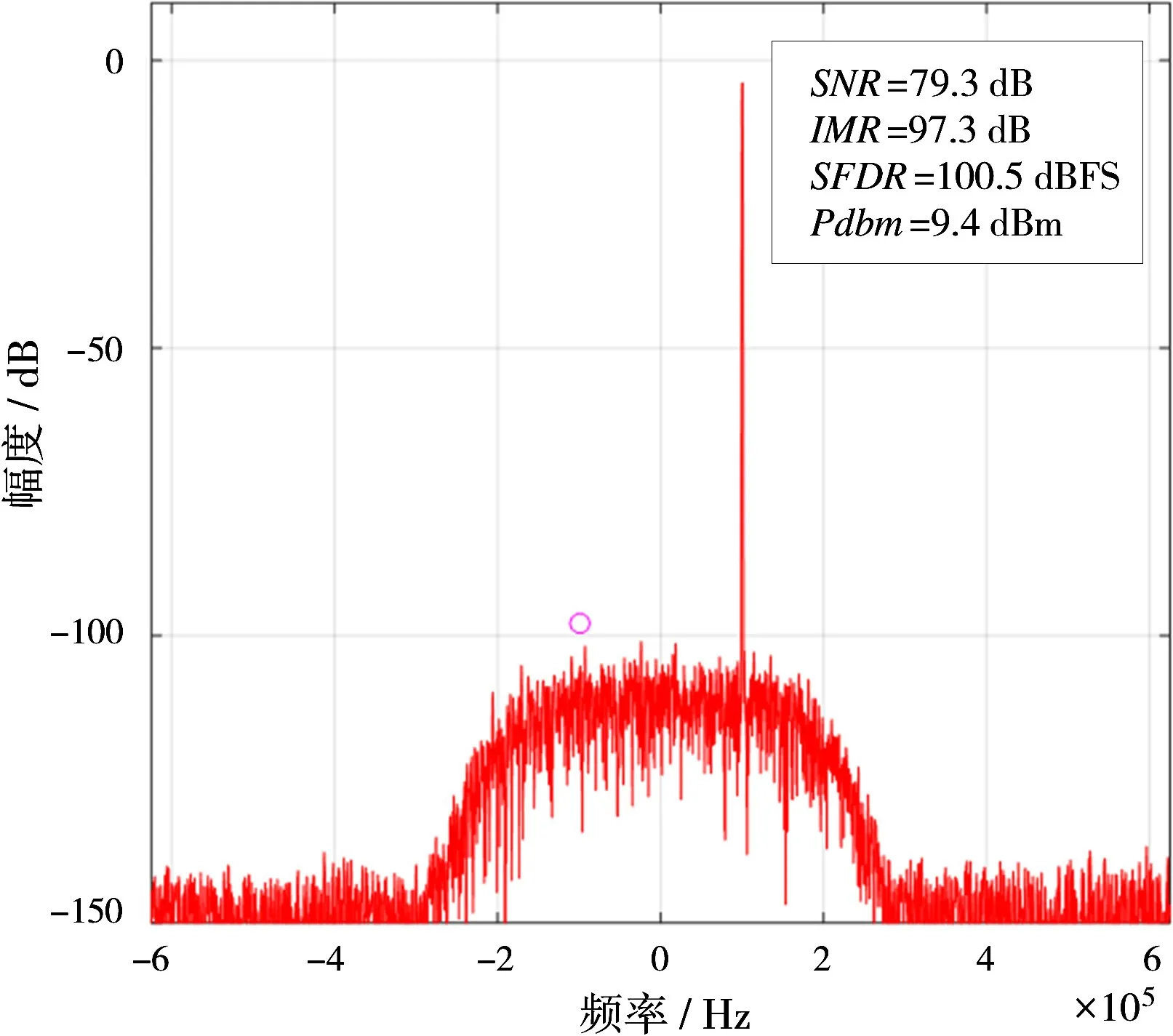

图19给出了多通道多带宽多速率DDC处理的数字接收机实物图;图20给出了5MHz带宽DDC处理实际输出信号的频谱图和测试指标情况;表5给出了该DDC处理FPGA资源利用情况。

图19 16通道数字化接收机实物图

图20 5MHz带宽DDC处理输出频谱

表5 基于FPGA/DDC设计资源利用情况

3.2 DDC工程化实现中需要注意的问题

1)SNR得益:根据式(5)DDC处理可以获得相应SNR处理得益,该得益要求滤波器具有陡峭的过渡带,造成滤波器阶数非常高,实现时占用大量的硬件资源,因此需要在得益和资源间进行平衡,实际设计时SNR得益较理论得益损失0.5~1.0dB,该损失需要在系统设计时加以考虑。

2)滤波器带内纹波:FIR滤波器设计一般基于等纹波设计来实现,造成信号带内频谱由于FIR数字滤波附加了周期调制,对于LFM信号将会造成脉压后成对回波的出现[17],纹波幅度和周期决定成对回波的大小和位置,影响脉压副瓣指标,纹波的大小同时对滤波器阶数影响较大,因此纹波大小、滤波器阶数和脉压副瓣指标间需要折中考虑。

3)直流和截位处理问题:中频采样ADC一般采用差分交流耦合输入,差分信号不平衡会造成直流以及杂散,DDC处理后直流将位于带外,但DDC处理过程中截位处理会造成基带直流出现,影响后续信号处理,因此数字截位处理时必须进行四舍五入处理。截位处理对系统的瞬时动态影响比较大,过多的截位会造成SNR损失[18],过少的截位会造成后续信号处理压力和资源浪费,基本原则是保证SNR没有损失;另外,对于通信等应用场合还可以采用数字AGC作动态截位或增益控制处理。

4)多通道时序同步问题:数字阵列雷达收发相参同时一般要作多脉冲相干积累处理,因此要求在相同波位内的多个脉冲间以及多个通道间相位保持固定的相位关系,多带宽、多速率DDC处理内部有各种不同的计数器,多通道特别是多个板子间上电后计数起始不同,因此必须保证所有路DDC处理在多个脉冲间以及不同模式间切换时必须在同一个触发下同步复位,这需要通过相应的硬件和软件设计加以保证。

4 结束语

本文论述了数字阵列模块内部基于FPGA的多通道、多带宽、多速率数字下变频设计,包括方案设计、仿真设计和工程化设计,同时给出了实际应用设计结果和工程化设计应注意的问题,该设计方法可应用于其他多通道数字化接收机数字下变频器设计。

[1]陈曾平,张月,鲍庆龙,等.数字阵列雷达及其关键技术进展[J].国防科技大学学报,2010,32(6):1-7.

[2]王才华,张德智,张卫清.一种S波段数字阵列模块的研制[J].雷达与对抗,2014,34(4):54-58.

[3]AD6636:150 MSPS Wideband Digital Down-Converter[Z].Analog Devices Product Guide,2005.

[4]伍小保,章仁飞,王冰,等.数字阵列雷达数字下变频器ASIC芯片设计[J].雷达科学与技术,2008,6(6):496-500.WU Xiaobao,ZHANG Renfei,WANG Bing,et al.Design of DDC ASIC Chip for Digital Array Radar[J].Radar Science and Technology,2008,6(6):496-500.(in Chinese)

[5]DUC/DDC Compiler V3.0:LogiCORE IP Product Guide[Z].Xilinx Product Guide,2015.

[6]HARRIS F J.通信系统中的多采样率信号处理[M].王霞,张国梅,刘树棠,译.西安:西安交通大学,2008.

[7]MILIC L.Multi-Rate Filtering for Digital Signal Processing:MATLAB Applications[M].New York:Information Science Reference,2009.

[8]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001:53-56.

[9]WANG Hong,LU Youxin,WAN Yonglun,et al.Design of Wideband Digital Receiver[C]∥International Conference on Communications,Circuits and Systems,Hong Kong:IEEE,2005:794-797.

[10]HARRIS F,DICK C,RICE M.Digital Receiver and Transmitters Using Polyphase Filter Banks for Wireless Communications[J].IEEE Trans on Microwave Theory and Techniques,2003,51(4):1395-1412.

[11]LI Bing,GE Lindong,ZHENG Jin.An Efficient Architecture for Wideband Digital Down Conversion Based on the Goertzel Filter[C]∥International Conference on Wireless Communications,Networking and Mobile Computing,Wuhan:IEEE,2006:1-4.

[12]张飞,伍小保.广义多相滤波及其应用[J].雷达科学与技术,2014,12(3):262-266.ZHANG Fei,WU Xiaobao.Generalized Polyphase Filtering(GPF)and Its Application[J].Radar Science and Technology,2014,12(3):262-266.(in Chinese)

[13]伍小保,王冰.宽带数字下变频和重采样处理Matlab仿真与FPGA实现[J].现代电子技术,2015,38(23):6-9.

[14]MITRA S K.Digital Signal Processing:A Computer-Based Approach[M].4th ed.London:Mc Graw-Hill Companies,Inc,2011.

[15]伍小保,王冰,郑世连,等.米波雷达射频数字化接收机抗干扰设计[J].雷达科学与技术,2015,13(2):214-218.WU Xiaobao,WANG Bing,ZHENG Shilian,et al.Anti-Jamming Design of RF Digitalized Receiver in VHF Radar[J].Radar Science and Technology,2015,13(2):214-218.(in Chinese)

[16]LIM Y C.Frequency-Response Masking Approach for the Synthesis of Sharp Linear Phase Digital Filters[J].IEEE Trans on Circuits and Systems,1986,33(4):357-364.

[17]陆必应,梁甸农.调频线性度对线性调频信号性能影响分析[J].系统工程与电子技术,2005,27(8):1384-1386.

[18]WIDROW B,KOLLAR I.Quantization Noise:Roundoff Error in Digital Computation,Signal Processing,Control,and Communications[M].Cambridge UK:Cambridge University Press,2008.