基于FPGA的高斯白噪声信号源实现*

吴国望 屈晓旭 徐 丹

(海军工程大学电子工程学院 武汉 430033)

基于FPGA的高斯白噪声信号源实现*

吴国望屈晓旭徐丹

(海军工程大学电子工程学院武汉430033)

摘要论文根据直接频率合成理论,对均匀分布的随机数进行白化处理,提出基于FPGA的高斯白噪声发生器实现方法。该方法实现简单快速,可移植性强,可以灵活的在实验或测试中运用。

关键词直接频率合成; 线性反馈移位寄存器; 高斯白噪声; FPGA

Class NumberTP391.1

1引言

在通信和控制系统中,高斯白噪声是很常见的噪声信号。在研究无线通信信道特性时,常常需要高斯白噪声信号源,用于测试和检验系统的抗干扰性能,所以设计实现一个结构简单、性能可靠的高斯白噪声信号源,对系统检测和理论研究都有非常必要的意义。

2实现原理

2.1直接数字频率合成[1~2]

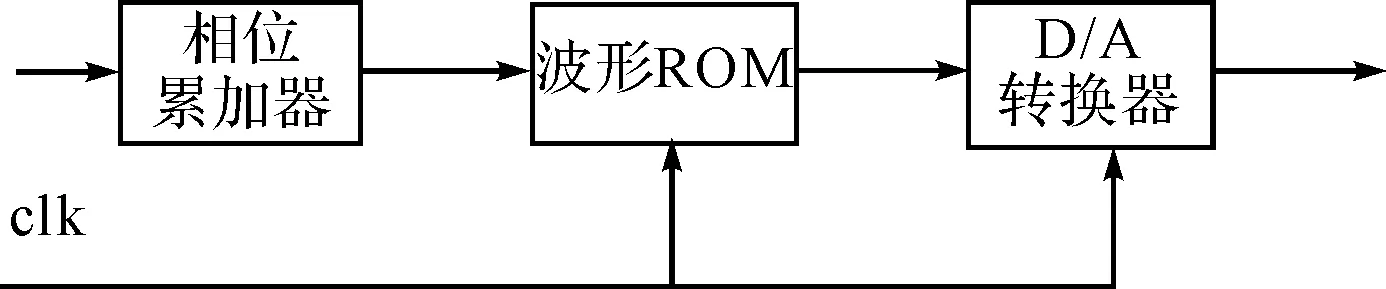

由于数字精度有限,数字高斯白噪声实际上产生的是伪随机数,具有一定的周期性。但只要周期足够长,就能满足工程需要。直接数字频率合成(DDS)是一种比较新颖的频率合成方法。随着科学技术的日益发展,这种频率合成方法也越来越体现它的优越性[3]。DDS是一种全数字化的频率合成方法[4~5],因此适合用于FPGA实现。图1所示是一个DDS的基本结构。本设计通过改变ROM查找表的内容,产生高斯白噪声。

图1 DDS基本结构

Altera公司的QUARTUS软件提供了ROM ip核,只要载入查找表就可以产生对应的波形数据。mif文件常用的一种查找表,在mif文件里除了相应的数据,还需要对数据的类型、位宽和存储单元格数进行说明。可以利用Matlab产生存有高斯白噪声数据的mif文件,避免了类似sin(x)、log(x)等超越函数的计算,适合FPGA实现。通过wgn()函数产生高斯白噪声数据,再把数据放大、量化,并且将数值写入外部文件,按照需要的格式创建.mif文件供ROM核调用。下面列出了实现程序。

N = 10;%N为数据宽度为10位

depth=2^N;%depth存储单元个数;

value = wgn(depth,depth,1); %产生高斯白噪声数据,value为高斯白噪声数据值

value = value*(depth/32 -1);%扩大白噪声幅度值

value = fix((value)+0.5); %对白噪声数据进行量化

2.2伪随机序列产生[6]

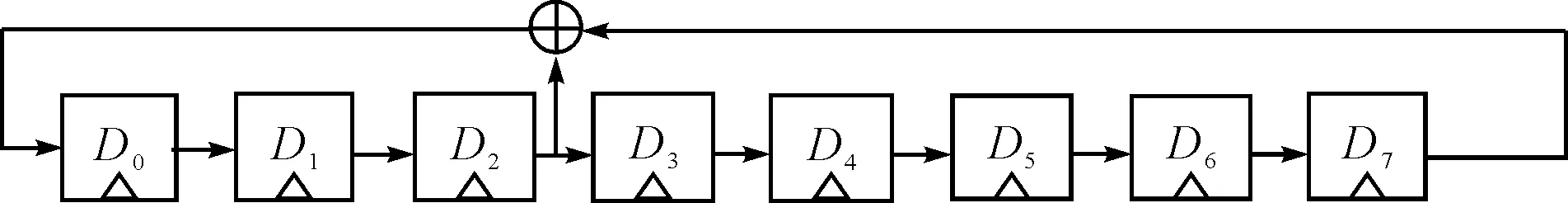

伪随机序列具有类似随机噪声的一些统计特性,且便于重复产生和处理,因此获得了广泛的应用。LFSR(Linear Feedback Shift-Register),即线性反馈移位寄存器[7],是可以用于产生伪随机序列的一种逻辑电路。一个LFSR电路有一系列M寄存器和决定序列转换状态的反馈抽头组成。反馈抽头由模-2多项式描述。对于一个M级LFSR来说,最多可以有2M个状态,全“0”状态不会转入其他状态,所以LFSR的最长周期是2M-1。为了使伪随机序列的周期满足要求,采用的本原多项式为:x8+x3+1[9~10]。连线如图2所示。

图2 LFSR实现结构

3硬件实现

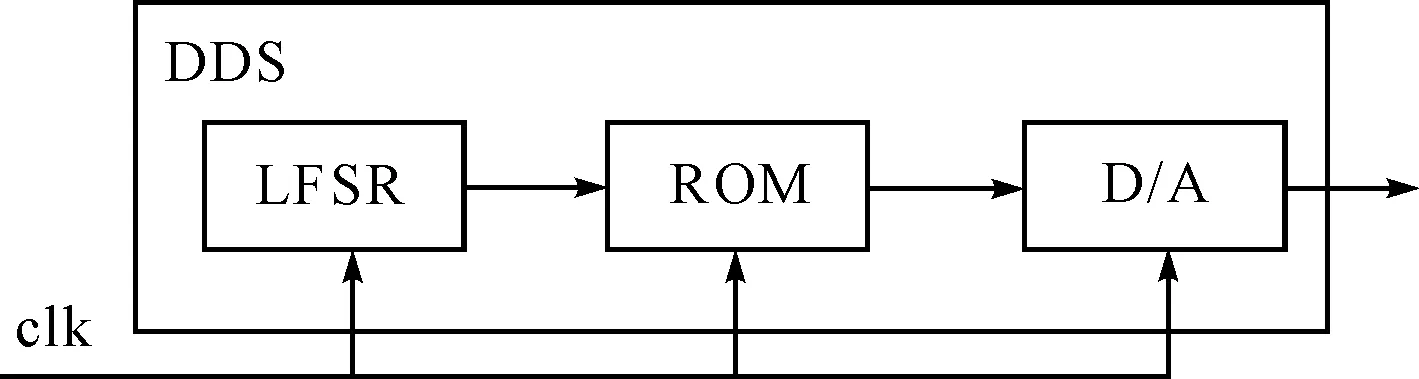

在Quartus9.1开发环境中使用VerilogHDL语言实现上述高斯白噪声发生器的功能,本设计选用友晶公司的DE0作为目标板。其实现框图如图3所示。

图3 硬件实现框图

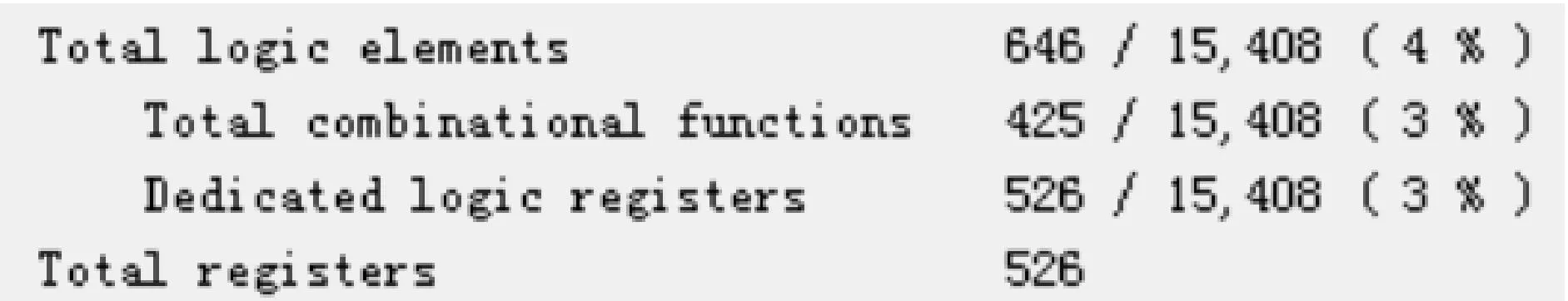

其中DDS模块包括存产生地址的LFSR模块、有高斯白噪声数据的ROM模块和D/A转换器。每一个时钟,LFSR把当前所有寄存器的值整体给ROM,作为是查找ROM的地址。根据地址,ROM有一个输出给D/A模块。D/A模块的功能就是进行数模转换,根据输入的输入产生需要的的模拟白噪声信号。图4为系统消耗资源的情况。可见,该方法实现简单,消耗资源少。

图4 资源消耗情况

4性能分析

将程序下载到开发板,并采用SignalTap将硬件产生的高斯白噪声序列通过JTAG回传,然后将数据导入到Matlab。由于SignalTap要利用FPGA的片内存储空间暂存采样值,所以一次采集的信号数目有限且与FPGA型号有关。实验中将一次采集到的8192个样值导入Matlab后,对结果进行验证。

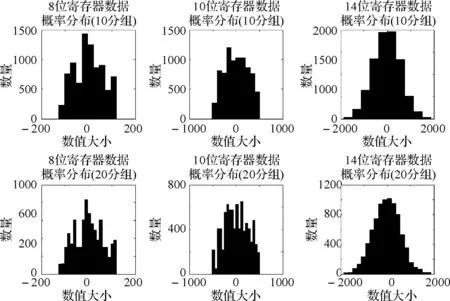

首先对数据的分布特性进行验证。利用Matlab中提供的hist()函数,默认把数据分为10组,都接近高斯分布。为了进一步验证分布特性,可以增加数据分组。如果统计特性良好,随着分组增加数据仍然保持良好的高斯分布。由图5可见,当把数据分为20组时,14位寄存器统计特性较好。

图5 概率分布情况

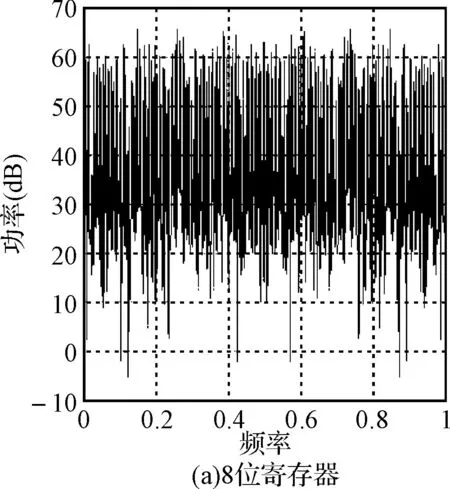

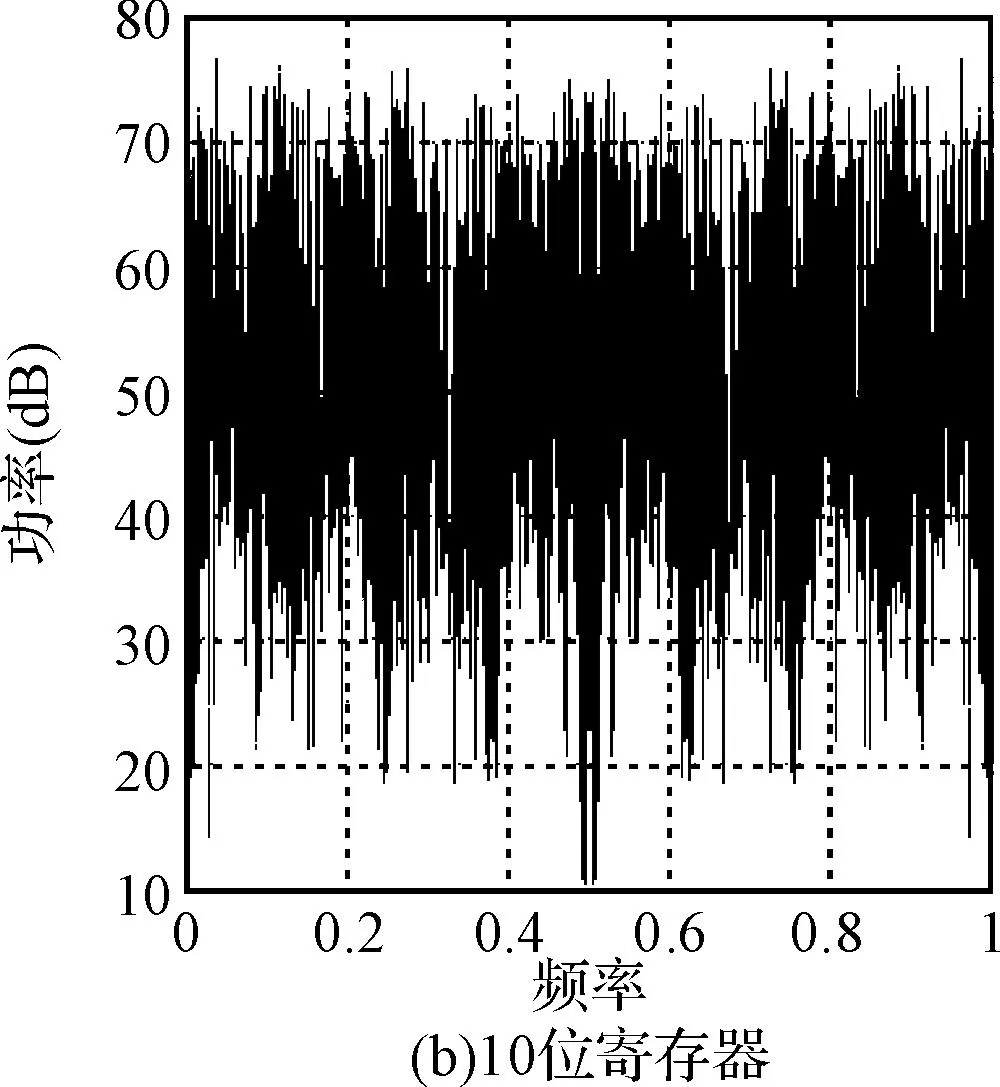

除了对数据的概率分布进行验证,还需要估计出其功率谱。计算功率谱密度,采用1024点周期图谱法。图6为功率谱密度。从结果来看,产生的白噪声功率谱平坦,与理论分析接近。下面给出了计算功率谱密度的程序。

N=1024;

Pxx=10*log10(abs(fft(Y8).^2)/N);

实验结果表明,增加寄存器位数可以提高性能。图6为8、10和14位寄存器的功率谱密度。随着寄存器和ROM空间的增加,统计分布和功率谱密度越来越趋近理论。实际工程中,芯片的存储资源不尽相同,在资源足够的情况下,可以通过增加寄存器位数提高白噪声性能。

图6 功率谱密度

5结论

本文提出了一种在FPGA中产生高斯白噪声的实现方案,该方案基于LFSR和DDS原理,简单易行运算量小,而且实现速度快,占用的硬件资源较少。方案还对系统性能进行分析,得出了通过增加寄存器位数提高性能的结论。

参 考 文 献

[1] 高琴,姜寿山,魏忠义.基于FPGA的 DDS信号源设计与实现[J].西安工程科技学院学报,2006,20(2):211-214.

[2] 张厥胜,曹丽娜.锁相与频率合成技术[M].成都:电子科技大学出版社,1995:140-147.

[3] 姜萍,王建新,吉训生.FPGA实现的直接数字频率合成器[J].电子技术用用,2002, 28(5): 43-44.

[4] 刘晨,王森章.直接数字频率合成器的设计及FPGA实现[J].微电子与计算机,2004,21(5):63-65.

[5] 宋阳,孙肖子,仁爱锋.基于DDS和FPGA的虚拟智能信号源的研究[J].数据采集与处理,2001,16:124-126.

[6] 管宇,徐雷,徐建中.用FPGA产生高斯白噪声序列的一种快速方法[J].电子元器件应用,2008,10(11):55-58.

[7] 张萍,戴光明.高斯随机噪声实时产生实现方法研究[J].技术应用,2004,(4):10-12.

[8] 樊昌信,曹丽娜.通信原理(第6版)[M].北京:国防工业出版社,2014:57-60.

[9] Tezuka, S. Lattice Structure of Pseudorandom Sequences from Shift Register Generator[C]//Proceedings of the 1990 Winter Simulation Conference,1990.

[10] Niederretter. H. New Developments in Uniform Pseudorandom Number and Vector Generation[J].Lecture Notes in Statistics,1995(106):87-120.

[11] 夏宇闻.数字系统设计教程(第3版)[M].北京:北京航天航空大学出版社,2013:39-49.

Realization of Gauss White Noise Signal Generator Based on FPGA

WU GuowangQU XiaowuXU Dan

(College of Electronic Engineering, Naval University of Engineering, Wuhan430033)

AbstractAccording to the theory of DDS, uniformly distributed random numbers whitening process, FPGA-based implementations of Gaussian white noise generator is proposed. The method is simple, rapid, and can be portabally used in experiments or tests flexibly.

Key Wordsdirect digital synthesizer, linear feedback shift-register, white guassian noise, FPGA

*收稿日期:2015年12月24日,修回日期:2016年1月28日

作者简介:吴国望,男,研究方向:数字通信。屈晓旭,男,博士,副教授,研究方向:数字通信。徐丹,女,硕士,讲师,研究方向:无线通信。

中图分类号TP391.1

DOI:10.3969/j.issn.1672-9730.2016.06.032