基于直接数字频率合成器的杂散来源和降低研究

戚 群

(长春理工大学,吉林 长春 130022)

基于直接数字频率合成器的杂散来源和降低研究

戚 群

(长春理工大学,吉林 长春 130022)

通过分析直接数字频率合成器的相位噪声模型,文章推导出相位截断、ROM存储器有限字长以及DAC性能对DDS相位噪声的影响。最后基于扰动技术的注入,文章在给出抑制杂散结构的同时,通过MATLAB仿真进行理论验证。

DDS;相位噪声;杂散结构

DDS(直接式数字频率合成)技术是在DS(直接频率合成)和IS(间接频率合成)之后应运而生的第三代频率合成技术。其主要特点是频率分辨率高,输出的相位不间断,频率的转换周期小,并且可以产生多种可以调制的信号。因为以上的这些优势让DDS在此技术领域占领至高的地位。另外,DDS主要给系统带来比模拟信号源更稳定的性能,所以在雷达、通信、检测等行业都取得了丰富的应用。最后,DDS在工作过程中,全采用数字技术,所以在设计和集成方面使用方便。

但是因为DDS自身的一些特性,必然导致了其缺点的存在:分布难预测、杂散抑制差,这在很大程度上限制了DDS的应用。其中,杂散成为限制DDS技术应用的一个突出因素。专家学者对直接数字频率合成器杂散及其来源进行了研究和详细的分析,并给出了诸多完善的方法。这些方法包括ROM压缩技术,包含利用正弦值的对称性和将ROM表读数分解为粗读和细读之和;采用控制字与2B互质的方法;利用随机化技术等等。

1 DDS相位噪声模型

作为工程简化,以DDS输出正弦波为模型,并假定在理想的情况下不考虑相位查找表的相位截断和波形幅度量化的近似,同时假定D/A转换器是理想的,D/A转换特性可以用门函数h(t)=u(t)-u(t-T)来表示,对其进行傅里叶变换可得:

正弦信号f(t)的频谱可以表示为:

根据频域卷积的性质,可求得抽样信号f(t)的频谱为:

式中:w0为正弦信号角频率,ws为DDS时钟角频率,k=0,±1,±2,±3,…,±n经过D/A后,输出信号的频谱可以表示为:

通过以上计算可知,DDS输出信号的频谱是以Sinc函数为包络的,输出的频率成分为nfs=±f0,DDS相位噪声模型如图1所示。其中3个噪声是加性噪声,最主要的是相位截断误差带来的噪声。

图1 DDS 相位噪声模型

2 DDS杂散来源

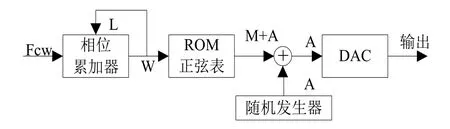

根据模型简化原则,在直接数字频率合成系统的原理款图里,fc的含义是作为参考的时钟频率,Fr的含义是对频率产生的控制字行为,字长是L,二进制序列,W的意思是相位累加器含有的字长,截断位数是B=L-W,字长为L(二进制,以下同),W为相位累加器的字长, ROM存储器输出幅度序列函数S(n),字长为S。DDS系统主要的杂散来源有:时钟泄漏;相位截断误差;ROM幅度量化误差;开关暂态引起的杂散;数模转换的非线性带来的转换误差。

图2 DDS原理框图

2.1 相位截断的影响

DDS输出频率为:

其输出的理想时域函数为:

相位累加器产生相位截断,忽略DAC性能,忽略ROM存储器的有限字长,显然DDS输出为:

式中:int(-)—取整函数;

s(m)—相位累加器输出的误差序列函数:

对一锯齿波函数S'(t)采样得到相位误差序列S'(m)。函

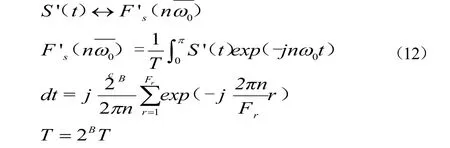

大多情况Fr为奇数,此时,由前述分析,S'(m)的周期为2B,如此就把S'(m)改变为2BTc,由傅氏变换

由式(9),(10),(12)得:

式(13)给出了直接数字频率合成器相位阶段杂散的幅度以及位置。在此需要注意,式(13)给出DDS的杂散位置,幅度是基于对S'(t)周期扩大而进行的,从而避免周期推导繁琐。由此可见DDS中,由相位截断引起的输出相位噪声恶化很小。

2.2 ROM存储器有限字长的影响

当ROM采用S位二进制数保存正弦函数值时量化误差为:

式中:R(x)—对x做最靠近x的取整函数。

式(15)给出,当每增加一位量化位数S,那么信噪比将增加6dB。

2.3 DAC的影响

DAC非线性转换引起的量化噪声与ROM存储器有限字长的影响相同。ROM存储其直接驱动直接数字频率合成器DAC,假设字长相同的情况下,输出相位噪声在式(15)基础上增加3 dB。

3 DDS中相位噪声的抑制

图3 DDS抖动注入方式

3.1 相位扰动动注入

相位扰动技术是在每一个时钟脉冲到来后,通过给相位累加器的输出中加入满足一定统计特性的随机信号来打破误差序列的周期性,从而降低杂散。其原理如图4所示。

图4 DDS相位扰动注入方式

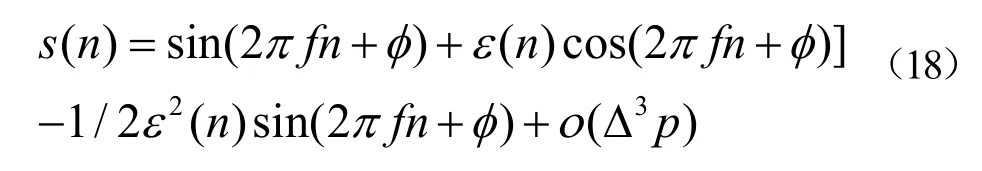

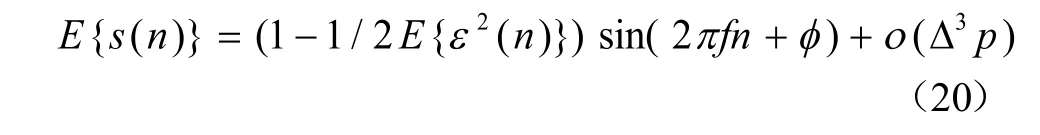

将上式在2πfn+φ处进行泰勒级数展开有:

由扰动信号Z(n)的独立同分布性有:ε(n)与ε(n+m)(m≠0)是独立的(m≠0),则S(n)的自相关函数为:

从上式可以看出除了底噪声外,随机过程的频谱信息包含在E{s(n)}中,又因为E{s(n)}=0,从而有:

通过对上式进行分析,得到了有用信号电平与寄生信号电平之比:

即得出结论:采用这种相位扰动技术,可使得杂散分量的抑制比从每相位6 dB增加到每相位12 dB。

利用MATLAB/SIMULINL软件对上述相位扰动技术进行仿真和性能分析。设计参数为:L=24,Fclk=100 MHZ,Fcw=0X199999,幅度量位数D=10,寻址位数W=10。加入相位扰动信号后的DDS输出频谱与没有加相位扰动信号DDS输出信号的频谱进行比较。加入相位扰动技术信号后的DDS输出信号频谱底噪声大大增多了,如图5所示,仿真结果表明加入相位扰动信号后的DDS输出频谱质量有所改善。

3.2 幅度扰动注入

将类似的扰动技术应用到ROM输出端与DAC之间则构成了幅度随机扰动技术。随机化幅度扰动方法原理如图6所示。

幅度扰动技术该方法实际是将DAC输入信号的最低有效位LSB进行随机化处理。在DAC的输入数据被截断成A bit之前,给正弦查找表输出的(A+M) bit数据加上一个随机数,其范围是:0~2B-1。

图5 相位扰动技术仿真结果

图6 幅度抖动注入原理图

4 结语

本文通过分析相位截断、ROM存储器有限字长以及DAC性能对DDS相位噪声的影响,确定通过抖动注入的技术来破坏信号的相关性以及误差周期性,实现杂散的抑制,通过仿真实验,验证理论。仿真结果表明加入相位扰动信号后的DDS输出频谱质量有所改善。

[1]芦俊,朱卫良,毛伟民,等.基于虚拟仪器的直接频率合成器相位噪声测量[J].计算机与数字工程,2010(9):31-34.

[2]黄旭伟.DDS杂散抑制技术研究[D].重庆:重庆大学,2007.

[3]段宗明,柴文乾,代传堂.时钟抖动和相位噪声对数据采集的影响[J].雷达科学与技术,2010(4):372-375.

[4]詹俊鹏.基于DDS技术的雷达信号模拟器设计与实现[D].西安:西安电子科技大学,2009.

[5]姚宏亮,汪海燕.基于DDS相位噪声分析与抑制[J].长春工业大学学报(自然科学版),2013(2):43-45.

[6]方俊,张平.在DDS波形发生器中相位截断噪声的分析和抑制[J].仪器仪表学报,2003(2):31-34.

Research on the spurious sources and reduction based on direct digital frequency synthesizer

Qi Qun

(Changchun University of Science and Technology, Changchun 130022, China)

Through the analysis of the phase noise model of direct digital frequency synthesizer, the paper deduced the phase truncation effect that the finite word length of ROM memory and DAC properties of the DDS phase noise had on. Finally based on the injection of perturbation technique, while the stray structure was given, the theory is verified by MATLAB simulation.

DDS; phase noise; stray structure

戚群(1991— ),女,辽宁丹东,硕士研究生;研究方向:微波通信技术。