资源数据传输速率提升方法的研究*

徐思毅 夏 泳 陈孟奇 范月霞

(武汉船舶通信研究所 武汉 430200)

资源数据传输速率提升方法的研究*

徐思毅 夏 泳 陈孟奇 范月霞

(武汉船舶通信研究所 武汉 430200)

数据的传输处理速率对资源分发设备的工作效率影响极大,是其极为重要的性能指标之一。论文在探讨影响数据传输速率因素的基础之上尝试了对数据通道各环节及数据处理流程进行优化,并对优化措施的有效性进行了定量分析。

资源分发; 数据通道; 数据传输

Class Number TP391

1 引言

资源分发是指从资源管理服务器获取资源文件,对文件数据经过处理后,再根据需要将处理后的数据通过网络发送至目标。资源分发设备需要支持同时向多个客户端分发相同或不同类型的资源文件。分发的效率取决于数据传输处理的速率。因此,数据传输速率是分发设备最核心的技术指标之一。根据需求,其数据传输速率应不低于200Mbps,但是,当前现有的分发平台的数据传输速率仅为20Mbps,远低于实际应用要求。因此,如何提高当前分发设备的数据传输速率是本文研究的核心内容。

2 问题分析

2.1 数据传输通道介绍

本文所测的数据传输速率指的是数据从加固计算机被送到数据处理平台中完成处理后,再返回到加固计算机这个过程的传输速率,包含数据处理的时间。这个过程的数据通道主要分成四个单元,如图1所示,主机平台接口单元、PCI-E接口单元、主控单元和数据处理单元。

分析该通道的数据传输速率时需要考虑七个环节:除了上述四个单元外,还有连接这四个单元的三处总线A、B、C。

理论上,可以由这七个环节各自的速率估算出平台数据分发的速率。

1) A总线和PCI-E接口单元

A为PCI-E总线,它与PCI-E接口单元组成密码卡的PCI-E通道。

单路PCI-E通道速率理论值为2.5Gbps,分发设备密码卡采用4路PCI-E总线,因此分发设备PCI-E通道速率的理论值为2.5Gbps×4 = 10Gbps。

2) 主控单元

该单元的速率主要由主控软件及主控芯片决定,据经验估算主控单元速率处于330M~550M之间。

3) 数据处理单元

经过对当前设备的测试经验,数据处理单元上的处理速率经测量约为800Mbps。

4) B、C均为EMIF总线

总线100MHz时钟频率,总线位宽为64bit的情况下,B、C两处回环速率理论值最大可达到64×100M/2=3.2Gbps。

综合以上各环节的速率值可以计算出整个环节的加密速率大约为

2.2 数据传输测速方法的设计

在数据传输速率的测试中,对当前设备平台的数据处理及传输速率的测试方法如下:

1) 先对数据处理时间进行计时:当数据从主机平台接口侧驱动送入数据处理平台时,开始计时。途径PCI-E接口芯片进行处理,在经过主控芯片进行处理,再送入数据处理芯片进数据处理运算后,原路经过主控芯片、PCI-E接口芯片后回到主机侧。至此,计时结束。所用时长为数据传输处理时间。

2) 根据测试所用数据量或文件大小及整个流程数据传输时间计算得到传输速率。

3) 分别循环1000次、2000次、 3000次、5000次和10000次进行计时测速。

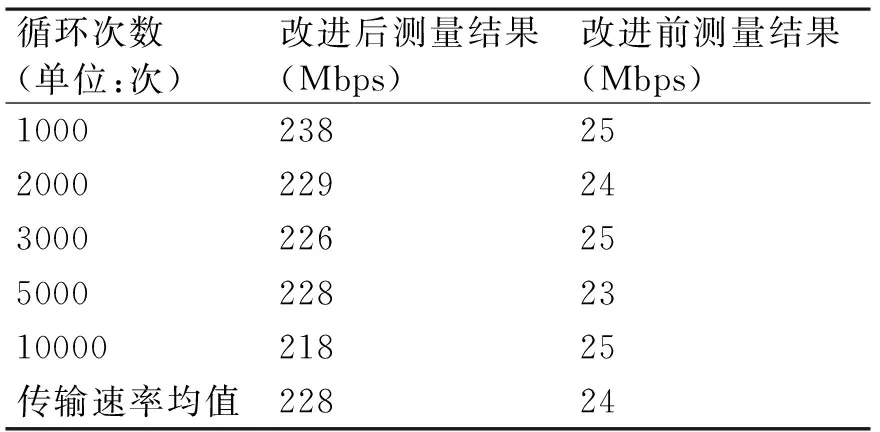

实际测速结果记录表设计表如表1所示。

表1 数据传输速率测试记录表

由表1知,数据的传输速率较低,约25Mbps。该实际测试结果与前述2.1中理论值差距较大,实际值远低于理论值,不能达到研制要求的200Mbps。因此,需要对数据通道各环节进行优化,进而达到提高数据处理平台的数据传输速率的目的。

3 解决措施

3.1 原因分析

上一节的分析中,数据传输通道的四个核心单元是主机平台接口单元、PIC-E接口单元、主控单元和数据处理单元。分析影响数据传输速率的原因,可能有很多,例如:数据处理单元的处理效率低、Linux驱动程序效率低、主控软件效率较低、数据处理单元总线宽度过窄、主频处理器平台主频较低等。

3.2 改进措施

通过对数据处理流程进行分析,可对以下几部分进行优化:

1) 主频处理器平台单元

主频处理器平台CPU由原来的Intel Atom N2600更换为Intel Core i7-3517UE,主要技术参数改变为:主频由1.6G提高到1.7G,L2 cache由1MB提高到4MB,总线带宽由2.5GT/s提高到5GT/s,分发设备PCI-E通道速率为5Gbps×4 = 20Gbps。由于平台速率受到PCI-E总线和处理器局部总线影响较大,因此可以看到总线带宽和cache的提高带来的传输速度的大幅提高。

更换主频处理器平台后再次进行测速,数据传输速率从约25Mbps提升到了约70Mbps,提升了80%,但距离预想要求的200Mbps仍有极大的差距。

2) PIC-E驱动单元

对于对更换主频处理器平台后的驱动代码也进行了优化,数据读取由之前查询方式改为中断方式,并对数据存取的操作采用汇编语言编写。这时候对比1)再进行速度提升,从约70Mbps提升至约为120Mbps,提升了约70%,距离目标200Mbps仍有较大的差距。

3) 主控单元

在对主控单元内数据处理流程进行分析后,发现可以对其进行优化。如图2,简单来说,就是将数据从片外SDRAM改为存储到片内RAM中。

设备模块的主控芯片为DSP,由于协议处理复杂,数据开销增大,需要片外的SDRAM进行缓存,程序进行数据处理的程序结构大致如图3所示。

首先,主机侧以分包方式(每包大小为4kbytes,可增大至15kbytes)通过PCI-E通道将数据传输至DSP,DSP解析协议数据后回复应答,并对每包数据缓存至片外的SDRAM(该SDRAM大小为32Mbytes);

其次,待收齐所有待处理数据后,DSP以分包形式将缓存在SDRAM的数据传输至数据处理单元进行处理工作,处理后的数据缓存于片外SDRAM;

最后,数据处理工作完成,DSP以分包形式将处理后的数据发送至主机侧。

改进的方案在现有的硬件平台上,对平台的应用程序中数据处理流向进行改变,如图4所示。

首先,主机侧通过PCIE通道发送数据(该数据包括第一包待处理数据)给DSP,DSP根据协议解析获取数据的相关信息后,发送给接口FPGA;

其次,接口FPGA接收来自DSP应答后,如果是待处理的信息,则将该应答中的相关信息(或全部信息)与第一包处理前数据发送给数据处理单元,待数据处理单元处理完成并回复后,接口FPGA将该处理后数据返还给主机侧;否则接口FPGA将该数据直接发送至主机侧;

最后,主机侧以分包方式将余下的待处理数据经接口FPGA直接发送至数据处理单元进行处理,不再经过DSP缓存转发。

如此改进后,再次进行测试,数据处理传输速率得到了一定的提升,从120Mbps提升至约190Mbps,提升了约60%,距离目标200Mbps仍有一定的差距。

4) 流水线设计

对于DSP这种单处理器来说,软件过程处理是串行的,但由于数据处理单元均用硬件实现,硬件优于软件的最明显的地方就是其并行处理的功能结构。其中最重要的优点就是,在某个时钟的控制下,硬件的每个模块均可同时进行,对于几个没有数据相互依赖性的模块,可以在控制模块的协调下完全相互独立的执行自己的工作。而对于有数据依赖的模块,虽然前一个模块的数据处理完之后才将数据交给下一级处理,但是,在下一个模块执行时,上级模块又可以进行下一次操作。即使两个模块的执行速度不一致,只要将执行时间调整到两者中的较大值即可。

流水线技术正是体现了这一设计思想,它是一种非常经济且对于提高硬件处理能力非常有效的技术,采用流水线技术可以在不增加硬件或者仅仅需要增加少量硬件就可以将数据处理速度提高好几倍。

在本研究中,数据处理单元建立两个FIFO:输入FIFO和输出FIFO;主机侧缓存两个存储空间:传输缓存区和接收缓存区。主机侧中将传输缓存区分成几个子模块,每个子模块就是一个专门的功能单元。在总线控制下,数据处理单元每次只要在输入FIFO收到子模块发过来的数据,就进行处理,并清空输入FIFO后将处理之后的数据放入输出FIFO,等待主机侧进行数据读取,并缓存至接收缓存区。如此完成多数据流的数据处理,其流水设计流程图如图5所示。

增加流水线的段数可以提高流水线的吞吐率,但如果段数过多,总的处理时间也会增加,也会增加缓冲区的数据量,所以需要根据处理的需要,选择性价比最高的方法来选择流水线的最佳段数。本研究中,以15kbytes数据大小为例,4kbytes为最佳段数,可达到数据传输的最大值。

经流水线设计后,再次进行测试,此时数据处理传输速率得到了进一步提升,从190Mbps提升到了约230Mbps,提升了约20%,达到了预期的性能指标,详细的测试数据记录在表2中。

3.3 效果验证

经过改进后,对设备的数据传输速率再次进行测试,结果见表2,与改进前的对比见表3。

表2 改进后数据处理传输速率统计表

表3 改进前后数据处理传输速率对比

与改进前的测试结果对比,改进后分发设备的数据处理传输速率有了极大的提升,从约24Mbps提升至约228Mbps,达到了性能指标。

4 结语

通过对数据分发处理平台的分析,不仅对数据通道各部分提出了优化措施,还对数据传输处理的过程也进行了优化。经过对优化前后的传输速率的测试对比,证明了优化措施的有效性。经过一系列的改进,最终资源分发平台的数据传输速率从20Mbps提升到了220Mbps以上,达到了性能指标。

[1] 刘娟,田泽,黎小玉.PCI_E接口驱动软件设计与实现[J].计算机技术与发展,2012(8):53-55.

[2] 杨志强,王厚军,李力.Linux系统下的 PCI串口设备驱动[J].电子测量技术,2011(9):58-60.

[3] 杨健.文件传输加密原则及处理方式研究[J].科技创新与应用,2014(20):59.

[4] 马雪英,章华,金勤.一个数据传输加密方案的设计与实现[J].计算机应用研究,2005(5):173-175.

[5] 米根锁,王瑞峰.基于PCI总线流水式高速数据采集系统设计[J].自动化仪表,2006(8):32-33.

[6] 崔俊杰,郭宏.基于FPGA的实时数据采集与远程传输系统设计[J].数据采集与处理,2005(3):366-370.

[7] X Pang, W Hu. The Design and Implementation of High Speed Data Acquisition System[J]. Chinese Journal os Scientific Instrument,2000:47-49.

[8] XY Wang, LU YingHua, LK Zhang. Design and Implementation of high-speed real-time Data Acquisition System based on FPGA[D].中国邮电高校学报(英文版),2006(4):61-66.

[9] XH Tian, K Zhang, Y Sun. The Design and Implementation of High-speed Data Acquisition System Based on FPGA[J]. Journal of Yangzhou Polytechnic College,2009:63-65.

[10] FU Xue, BU Xiongzhu, BY Shen. Design and Implementation of High Speed Acquisition and Storage System Based on FPGA[J]. Instrumentation Technology,2013:112-114.

Improvement of Data Transmission Rate of Data Distribution

XU Siyi XIA Yong CHEN Mengqi FAN Yuexia

(Wuhan Ship Communication Research Institute, Wuhan 430200)

The data distribution equipment is the mainstay of the data distribution system. The data transmission rate is one of the most important key performance indicators. Based on the analysis of factors which offect data transmission rate, this paper tries to improve various aspects of data channel and process of data and the efficiency of optimization measures is analyzed quantitatively in this paper.

data distribution, data channel, data transmission

2016年10月10日,

2016年11月11日

徐思毅,女,硕士研究生,研究方向:信息安全。夏泳,男,研究员,研究方向:信息安全。陈孟奇,男,工程师,研究方向:信息安全。范月霞,女,工程师,研究方向:信息安全。

TP391

10.3969/j.issn.1672-9730.2017.04.012