新思科技数字与定制设计平台通过TSMC 5 nm EUV工艺技术认证

2018-04-16 16:46

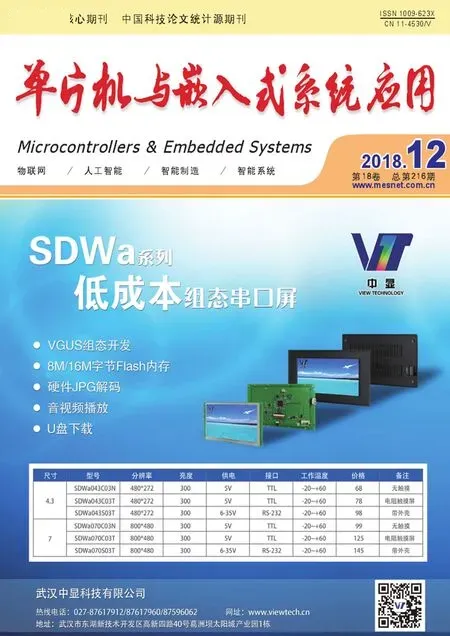

单片机与嵌入式系统应用 2018年12期

新思科技(Synopsys, Inc.)宣布,新思科技数字和定制设计平台通过了TSMC最先进的5 nm EUV工艺技术认证。该认证是多年广泛合作的结果,旨在提供更优化的设计解决方案,加快下一代设计的发展进程。

Design Compiler Graphical综合工具经过了严格的5 nm启用验证,并证明了与IC Compiler II布局布线工具在时序、面积、功耗和布线拥塞方面的相关一致性。Design Compiler Graphical 5 nm创新技术可以实现最佳性能、最低功耗和最优面积,这些新技术包括过孔支柱优化、多位库和引脚接入优化。

IC Compiler II的增强功能是满足设计密度要求的关键。在优化过程中可内在地处理复杂的、多变量以及二维的单元布局,同时最大限度提高下游可布线性以及整体的设计收敛。

新思科技PrimeTime时序分析和signoff解决方案中的POCV分析已得到增强,能够准确地捕获由于工艺缩放和通常用于实现能源效率而采用的低电压操作导致的非线性变化。此外,PrimeTime物理感知ECO已扩展到能够支持更复杂的版图规则,以改善拥塞、布局和引脚接入感知。

猜你喜欢

成都信息工程大学学报(2021年1期)2021-07-22

家庭影院技术(2020年2期)2020-03-25

中国化肥信息(2019年1期)2019-04-03

石油化工自动化(2018年5期)2018-11-14

通信电源技术(2018年3期)2018-06-26

山东工业技术(2016年15期)2016-12-01

当代化工研究(2016年5期)2016-03-20

电子设计工程(2014年17期)2014-02-27

电子设计工程(2014年12期)2014-02-27

山西大同大学学报(自然科学版)(2014年3期)2014-01-23