CMOS射频前端LNA的设计

尹 强,黄海生,曹新亮,杨 锐

(1.西安邮电大学 电子工程学院,陕西 西安 710121;2.延安大学 物理学与电子信息学院,陕西 延安 716000)

无线接收机系统在射频集成电路的设计应用中最广泛,也最具有挑战性[1-2]。随着移动通讯技术的发展,移动通讯终端对低压低功耗的要求越来越高,也越来越迫切,能否使用更低的电压实现性能良好的低噪声放大器是能否实现接收终端的关键[3-4]。随着深亚微米CMOS工艺的快速发展,其高频特性和噪声特性正在不断提高。而CMOS工艺所独具的工艺成熟、低成本、低功耗、高集成度以及应用广泛[5-6]等不可替代的优点使其在实现射频前端方面具有相当大的潜力。现代无线通信的快速发展,使1.95~2.05 GHz能很好地用CMOS实现,因此本文设计了一种新型的工作在此频段上基于CMOS工艺的窄带低噪声放大器。

1 理论分析

1.1 关键单元

射频前端收发结构如图1所示[7],低噪声放大器位于射频接收机的第一级,在天线和混频电路之间,它是射频接收机前端的主要部分[8-10]。LNA用于放大接收机天线接收的微弱信号,再经选频滤波器输出至混频器单元[11]。

图1 射频前端收发结构Fig.1 RF front-end transceiver

1.2 噪声分析

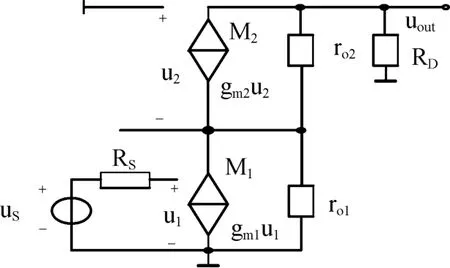

低噪声放大器的拓扑结构有很多种,本文采用源端电感负反馈结构的LNA,如图2所示,选择这种结构的LNA原因在于其用纯电抗元件使输入阻抗为50 Ω而不增加额外的噪声。共源管M1可提供较高的电压增益,并呈现较低的噪声系数和较高的输入阻抗;连接共栅管M2可以有效抑制密勒效应并提高输出阻抗。图3是图2的小信号等效模型,为了简化分析,忽略了衬底的背栅效应以及M1、M2的栅、源、漏之间的寄生电容。

图2 共源共栅结构的LNAFig.2 LNA of cascode structure

式中:ωT为晶体管的截止频率,设gm为跨导,其表达式为

由图2的简化模型可以得到输入阻抗表达式为

图3 共源共栅结构LNA小信号等效电路Fig.3 Small signal equivalent circuit of cascode LNA

Cgs为M1的栅源间电容。通过选择负反馈电感Ls的值来调节实部阻抗,而虚部等效为LC串联谐振电路。通过调节各元件的值,可以使LC串联谐振电路在工作频率处谐振,也就是虚部为零。即

输出阻抗Ro表达式为

式中:ro1和ro2分别为M1管和M2管的输出电阻;为M2管源极和衬底之间的跨导。假设,则M2管把M1管的输出阻抗提高至原来的倍,提高了输出阻抗。

2 LNA电路设计

2.1 设计思路

低噪声放大器电路设计可分为四个部分:放大电路、偏置电路、输入匹配电路和输出匹配电路。其中核心是放大电路部分,用偏置电路来提供电源供电。本次设计采用共源共栅电路结构(Cascode),偏置电路采用直流电压源偏置。如图4所示。其中M1管是共源管,作为放大电路的主放大管,提供足够高的增益。M2管是共栅管,用来减少M1管栅漏间电容Cgd引起的密勒效应,以增加电路的反向隔离特性,同时提高放大器的输出阻抗。偏置电路采用直流电压源与大电阻串联的方式来实现M1管的直流偏置,大电阻保证交流信号不会进入直流通路。C1、L1和L2主要是实现输入端口的匹配,L3、L4、C2、C3、R3为输出端口的匹配网络,通过调节L3、C1和M1的宽长比控制系统的稳定性。

图4 LNA电路结构Fig.4 LNA circuit structure

2.2 电路参数选择

从TSMC RF COMS 0.13 μm 工艺库文件中查到相关参数如表1所示。

表1 工艺参数Tab.1 Process parameters

由Cox=εox/tox可知,Cox=13.73 nF/m2。 进一步就很容易得到μnCox的值。根据功耗要求确定电路的工作电流,从而确定偏置电压。因为工作电压是1.2 V,根据功耗要求将电路设置工作在3 mA左右,之后确定过驱动电压为0.1 V,把偏置电压设置在0.4 V。低噪声放大器的前一级对后级噪声的影响至关重要,因此电路的噪声性能主要由M1决定,栅宽越大,噪声越小,但是为了能够在规定功耗限制下设计出合理器件尺寸使噪声系数最小,于是采用功耗约束噪声优化技术[12]。达到最小噪声的最佳品质因数公式:

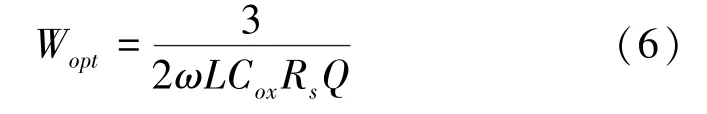

式中:c为栅-漏极噪声的相关系数;γ是沟道热噪声系数,为常数;δ跟工艺相关的噪声参数,且δ=2γ。最佳品质因数Q的取值范围为3.5~4.5,经过分析取Q值为4。那么在功耗约束下最优器件栅宽计算公式[13]为

式中:L为器件有效栅长;ω为工作频率;Cox是单位面积的栅氧化层电容;Rs为50 Ω。根据

计算出Wopt=210 μm。

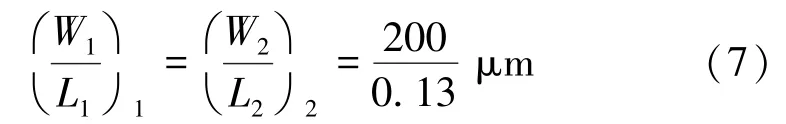

考虑到功耗会偏大的影响,最终得到M1管和M2管的宽长比为:

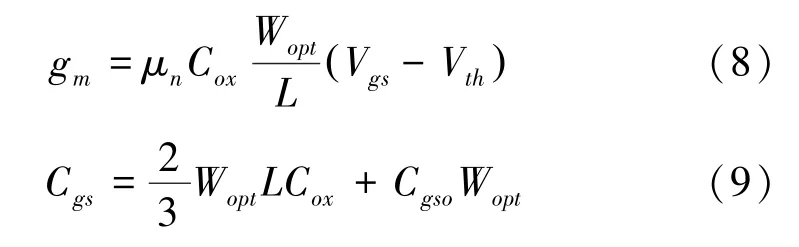

根据得到的偏置电压和工作电流,这时可以计算出截止频率ωT。已知式(8)和式(9):

由式(8)、(9)和(2)可知MOS管的截止频率ωT约为86 GHz。由噪声系数公式:

得到噪声系数Fmin约为0.79 dB。将输入匹配到50 Ω可计算电感L1和L2的值。由式(1)可知在谐振频率ω=2 GHz处可得到L1=22.8 nH,L2=0.45 nH。L3,R3,C2,L4,C3的取值可根据共源共栅结构的等效电路和该匹配网络的总等效电路实现输出 50 Ω。

3 仿真及结果分析

本文提出的共源共栅结构的低噪声放大器采用TSMC RF CMOS 0.13 μm 工艺库,在安捷伦射频集成电路设计工具ADS 2009平台上进行仿真验证[14]。在1.2 V电源电压下,电路的静态功耗为3 mW,中心工作频率为2 GHz。

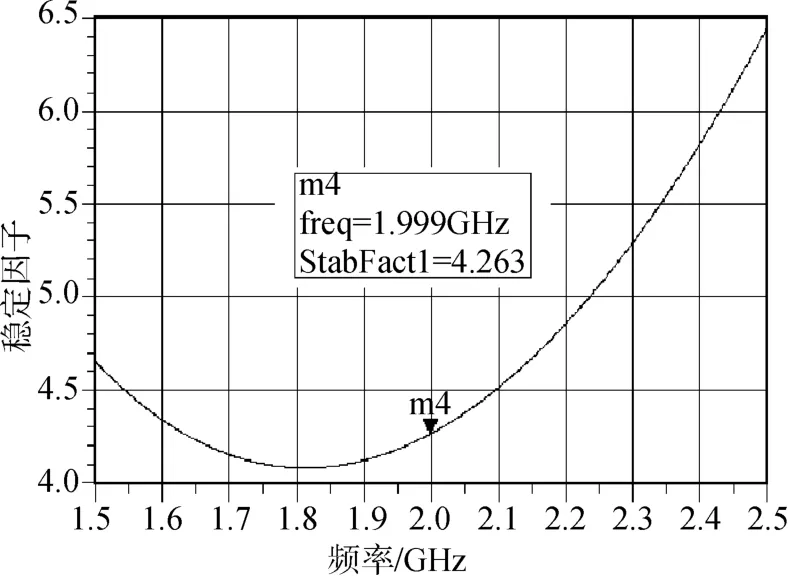

如图5所示,在中心频率2 GHz处,稳定因子大约为4.26,并且稳定因子在整个通带内都大于1,保证了系统的稳定性。

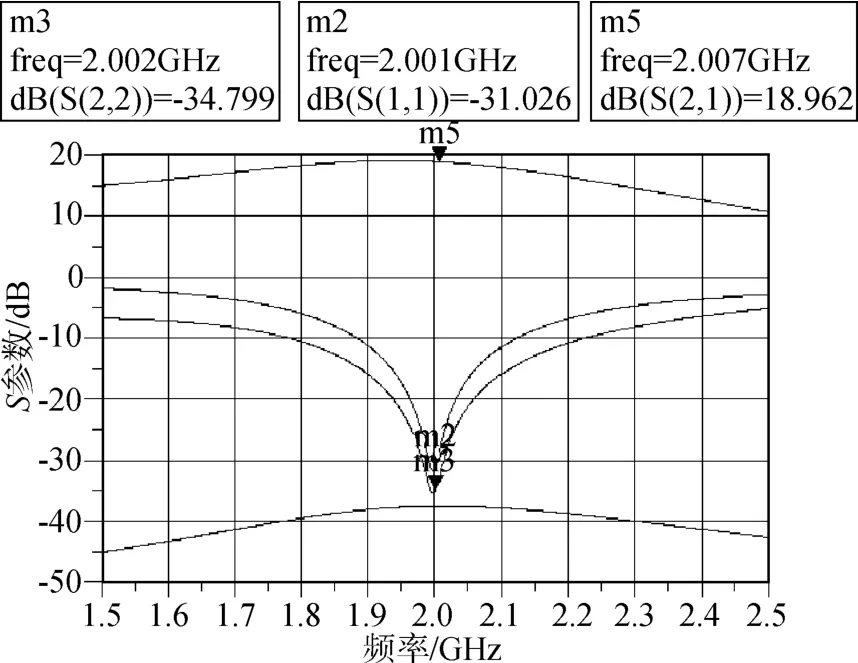

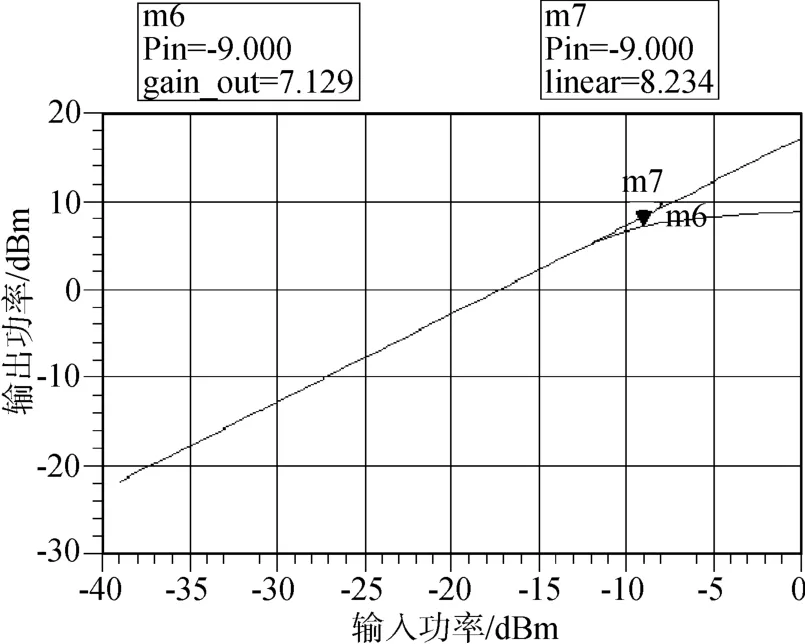

S参数随频率变化的曲线如图6所示,在中心频率2 GHz处,S(1,1)=-31.03 dB,S(2,2)=-34.80 dB,实现了很好的输入输出阻抗匹配;S(2,1)=18.96 dB,说明电路具有足够高的增益。噪声系数仿真如图7所示,在2 GHz处,噪声系数为1.15 dB,与计算的较小噪声系数相差0.36 dB。1 dB压缩点(P1dB)仿真结果如图8所示,该LNA的输入1 dB压缩点为-9.0 dBm,满足一定的线性指标要求。

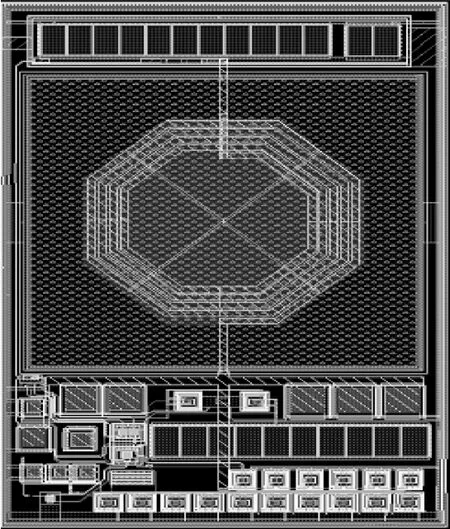

最终进行了版图设计及绘制,LNA的整体版图如图9所示,面积为0.18 mm2。

图5 LNA的稳定因子仿真Fig.5 Stability factor simulation of LNA

图6 LNA的S参数仿真Fig.6 S-parameter simulation of LNA

图7 LNA的噪声系数仿真Fig.7 Noise figure simulation of LNA

图8 LNA的1 dB压缩点仿真Fig.8 Compression point of LNA simulation at 1dB

图9 LNA的版图Fig.9 Layout of LNA

经过仿真验证,本文又与近年来已发表的有关文献中LNA的性能指标进行了比较,如表2所示,本文所设计的LNA在功耗、噪声、匹配和线性度等方面具有一定的优势。

表2 本文LNA的性能与其他文献的比较Tab.2 Comparison of the performance of the LNA and other thesises

4 结论

本文分析并设计了一个采用共源共栅结构的低噪声放大器。电路采用 TSMC RF CMOS 0.13 μm工艺,工作在中心频率为2 GHz处。在1.2 V工作电源下,静态功耗仅为3 mW,为整个系统提供18.96 dB的增益,噪声系数为1.15 dB,输入输出匹配均在-30 dB以下。实验结果表明,本文提出的低噪声放大器具有较好的性能,满足移动通信主流标准TD-SCDMA 2 GHz射频前端的要求。