基于FPGA的通用可编程雷达接收机控制系统设计

,

(南京电子技术研究所,南京 210039)

0 引言

雷达接收机是雷达系统的重要组成部分,主要用于回波信号的放大。雷达接收机调试测试时需要各种外部支撑信号,如多路定时时序、串行总线控制、射频输入、输出、供电等,接收机控制系统提供定时信号及总线信号用于状态的控制及转换,满足接收机的工作需求。目前,雷达系统大都采用超外差雷达接收机[1],不同种类接收机工作原理基本相同,但在各型接收机中定时信号和工作模式编码有所不同,即使部分接口在传输时采用相同的数据格式,数据传输速率也固定不变,但接口协议[2]不同,每个接收机的设计要求不一致,导致不同的接收机只能采用不同的控制系统实现控制。

本文为解决采用不同控制接口的接收机的控制兼容性问题,构建了通用型的接收机控制系统,依据不同的被测接收机的选择,通过匹配专用的适配电缆、加载相应控制程序的方式,满足不同接收机工作时支撑信号的需求,实现了对不同种类接收机的兼容,具有良好的通用性。

1 系统设计的结构及原理

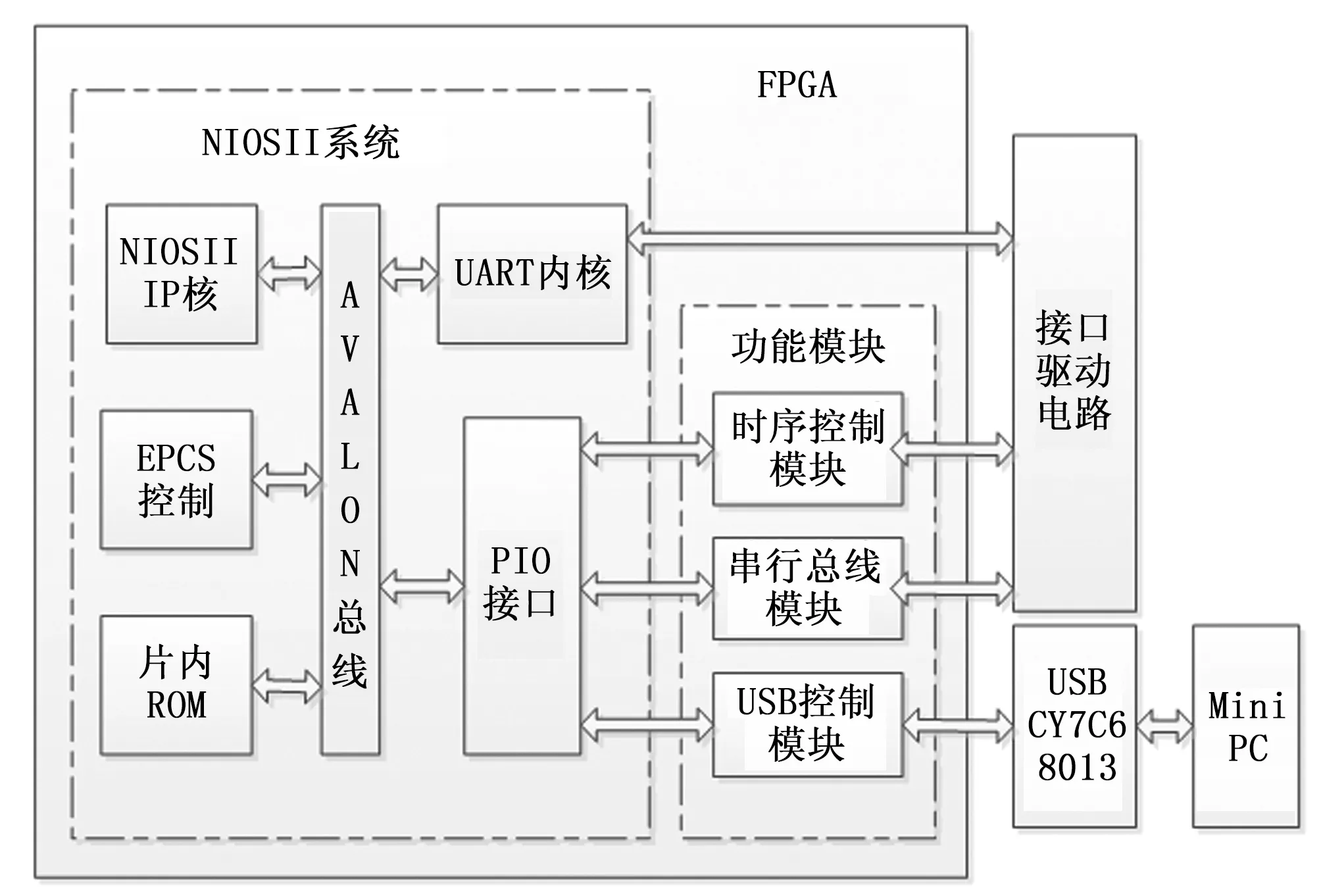

雷达接收机控制系统主要由触摸显示屏、FPGA芯片、接口驱动电路、USB接口芯片、外围配置电路、适配电缆及Mini-PC组成。其中FPGA为核心功能器件,内部包括USB控制模块、时序控制模块、串行总线模块和UART(通用异步收发传输器)模块。系统框图如图1所示。

图1 测试系统组成框图

通过触摸显示屏控制由Mini-PC机发送控制指令,包含状态转换、总线数据、重频周期、延时时间等参数,通过USB芯片(CY7C68103)传送至FPGA芯片中USB控制模块,包含控制参数的USB数据包被解析后依据主控模块协议转换成相应的控制字及配置参数,分别控制各个功能模块。串行总线模块和UART模块将接收到的数据按协议要求进行传输;时序控制模块接收到时序参数后,可产生最多8路的时序控制信号,其中波形起始位置、脉宽、周期可在一定范围内调整。

2 硬件设计

接收机控制系统的主要硬件设计是主控模块和适配电缆的设计。

2.1 主控模块

主控模块是该系统的核心部分,主要用于与上位机通讯并通过各类总线提供被测接收机所需要的控制模式、工作时序,完成与被测单元的互交工作。根据被测接收机的控制需求,总结出主控模块的设计要求:

1)与上位机具备通讯功能;

2)时序波形可产生8路,重频在一定范围内可配置,各路时序关系可配置,否则无法满足不同工作模式下要求的各种时序;

3)数据接口协议可定制,以满足多种接口要求。

基于上述设计要求,以及设备的通用性,主控模块设计为USB通用接口形式。总线接口芯片采用Cypress公司推出的CY768013芯片,通过USB 2.0接口数据传输速率高达480 Mb/s,支持热插拔,实现主控模块与PC之间的数据交换。逻辑功能、数据处理功能和接口功能通过Altera公司的Cyclone IV系列FPGA芯片实现[3]。

2.1.1 FPGA硬件设计

FPGA硬件系统采用Altera公司的Cyclone IV系列FPGA芯片来实现,其具有功耗低、性能高的特点,可配置32位的NIOSⅡ系统,通过Avalon总线结构与其他功能模块进行连接。采用SOPC(可编程片上系统)技术构建了NIOSⅡ系统,实现各模块的并行工作,并使用IP软核实现UART功能;应用Verilog HDL硬件语言设计了串行总线模块、时序控制模块及USB控制模块[4-6]。

图2 FPGA硬件系统框图

2.1.2 串行总线模块

系统控制命令经过转换后形成控制码字,位宽为18至30 bit,经过并串转换模块,转换成同步串行数据,输入被测接收机。并串转换模块结构图如图3所示,由位移寄存器、定时电路、延时电路组成。本设计中,采用定时转换的方式,由定时电路产生转换速率,在每个固定延时点上将位移寄存器中数据输出(DATA),并在半个延时周期后将同步信号(CP)送出,然后进行计数器的计数,在完成控制数据转换后,提供命令更新信号(UPDATA)。采用100M晶振作为计数输入,可达到100 M转换速度。

图3 串行总线模块结构图

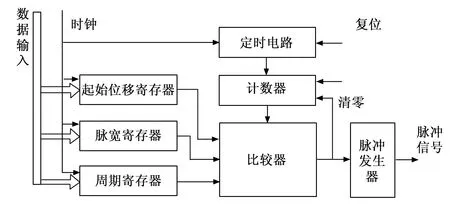

2.1.3 时序控制模块

该模块采用100 MHz的时钟,主要产生8路精度可控、脉宽可控的脉冲信号。在100 MHz时钟下,定时电路通过匹配定时寄存器确定计数频率。起始寄存器、脉宽寄存器、周期寄存器接收命令转换模块传输的参数,通过与比较器的比较产生触发信号控制脉冲发生器输出相应的脉冲信号。图4为一路信号的模块结构图,本设计中,共使用8个相同模块,以其中一路为基准输出,设计出相关联的信号,定时信号采用10分频数据,其他寄存器采用18 bits设计,设计重频38 Hz~10 M可变,满足系统要求。

图4 时序控制模块结构图

2.1.4 USB控制模块的设计

CYPRESS公司的EZ-USB FX2 系列芯片CY7C68013是最早符合USB2.0协议的微控制器之一。通过将 USB2.0收发器、串行接口引擎(SIE)、增强型8051微控制器以及可编程外设接口集成到一个芯片中,形成了一个极具成本优势的USB总线解决方案[7]。

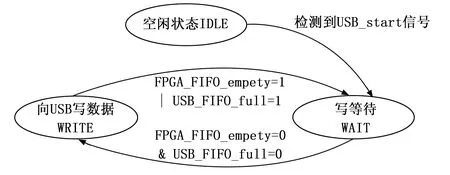

本设计中USB控制传输模块的设计实现了两种USB传输模式,控制传输模式和批量传输模式。控制传输模式主要用于发送和接收与USB设备的配置信息有关的数据,批量传输实现USB2.0接口与上位机的高速通讯,使用Slave FIFO传输方式。Slave FIFO方式的外部主控器由FPGA实现,CY7C68013与FPGA直接连接,CY7C68013的CPU不直接参与USB数据处理与分析,仅把CY7C68013作为外部数据处理的USB通道,通过对CY7C68013的内部端点FIFO的直接传输,完成数据的传输。对于外部主控器而言,可以把CY7C68013的端点FIFO当做一般的FIFO缓冲区来使用,外部主控器对芯片的端点FIFO进行控制,同时为FIFO提供所需的时序信号、空满信号以及输出使能等。

状态转换图如图5所示。系统初始化后,USB传输模块处于空闲状态,在接收到驱动信号USB_Start信号时进入写等待状态,准备将FIFO中数据发送到CY7C68013芯片;一旦端点FIFO不满(USB_FIFO_full为低)且FPGA_FIFO不为空(FPGA_FIFO_empety为低),模块将进入写状态,产生FIFO写信号sl_write,将数据写入芯片内部端点FIFO,由USB2.0收发器将数据打包传送到上位机;当端点FIFO满(USB_FIFO_full为高)或者FPGA_FIFO为空(FPGA_FIFO_empety为高),主控器将停止发送数据,sl_write无效,再次进入等待状态,依次循环。

图5 USB传输状态转换图

2.2 适配电缆

适配电缆主要实现接收机与主控模块的连接,实现系统资源与被测件之间信号的匹配和转换。实现适配电缆有2种方式:第一种将控制资源信号接入专用控制板,专用控制板提供对外统一接口,利用信号转接或者专用测试电缆连接被测件;第二种是将控制资源引入通用阵列设计专用适配器与通用阵列对接,通过专用电缆实现物理连接。

本设计采用第一种方式进行设计,在主控模块中集成接口驱动模块,可以提供单端信号和差分信号2种不同的驱动模式,系统资源连接至统一对外接口,不同接口关系的接收机依据各自接口定义关系选择相应的资源,设计成不同的适配电缆用于实现接收机与主控模块之间数据和控制信号的连接。

3 软件设计

控制系统软件主要由软件平台、控制程序集及主控模块程序组成。使用VISUAL C++开发的运行在上位机Mini-PC上的软件平台为控制系统提供了形象直观的可视化人机交互界面,并且能够根据软件配置调用相应的控制程序集构建软件系统,通过主控模块程序控制硬件设备正常工作,完成对接收机的控制。

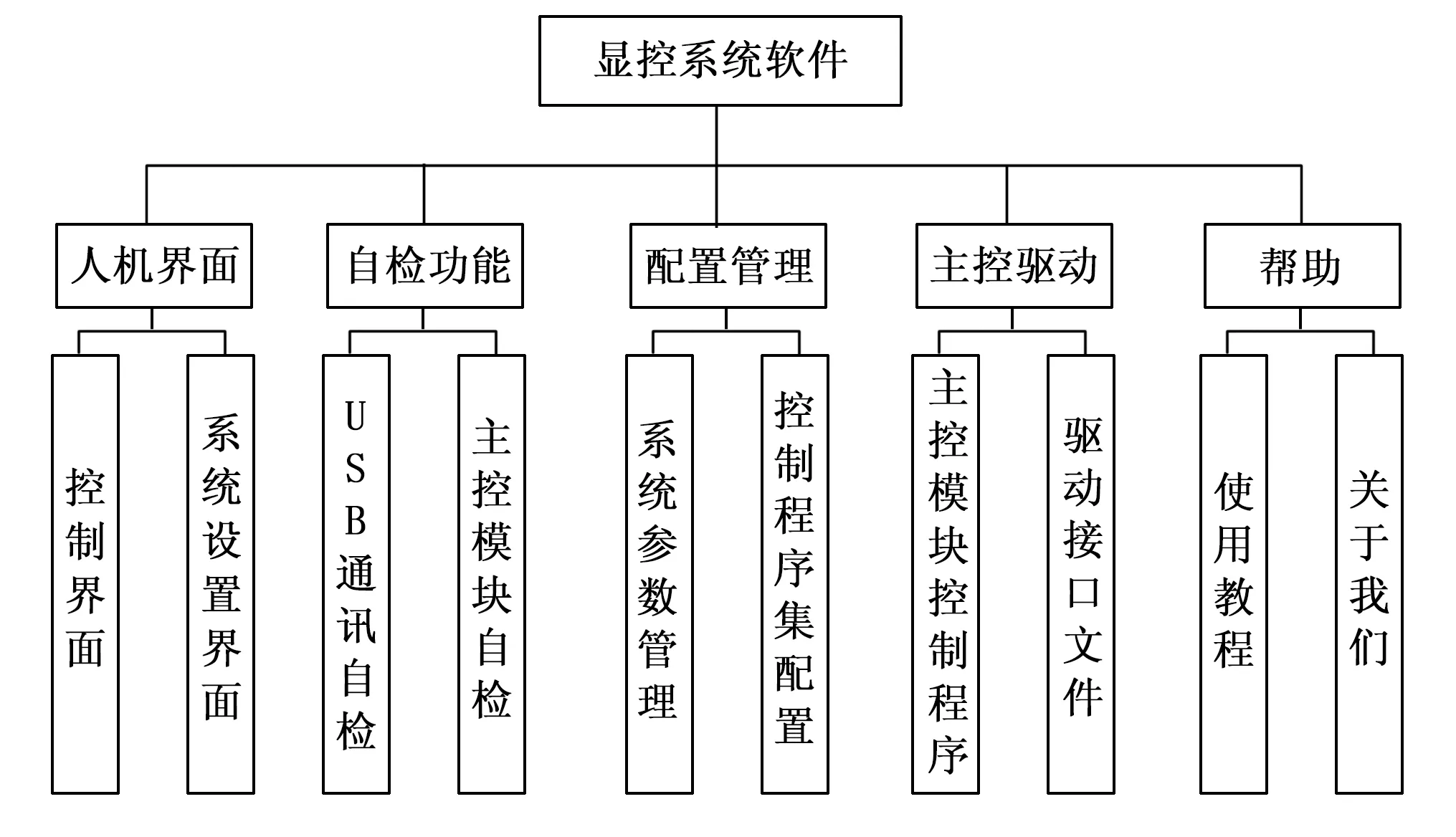

软件平台的设计采用模块化、层次化、可扩展的构建思路[8],各功能模块相互独立。在上层软件框架下根据不同被测单元的控制要求,开发对应的控制子程序。控制人员调用不同的子程序,则可以快速构建对应的软件环境。软件平台主要功能模块包括:人机界面、自检功能、配置管理、主控驱动和帮助。

系统软件对主控模块的控制进行了封装,能够轻松实现主控模块参数的配置和控制,解决了模块功能升级造成的软件升级障碍,提高了系统升级维护的效率[9],降低了维护成本。

控制系统软件的功能框图如6所示。

图6 控制系统软件功能框图

Mini-PC软件开始工作时,首先自动进行系统自检,自检功能包括USB通讯自检、主控模块自检,如若自检失败,系统会给出提示。自检通过后,进入系统设置界面,软件根据被测件的选择通过配置管理程序调用相应的控制程序集配置文件进行初始化配置,配置完成后系统切换到控制界面,依据控制界面的选择及控制完成对被测单元的控制,并返回控制状态。

控制程序集是指被测件的状态转换所需的控制程序集合,每个不同被测件对应一个控制程序集,涵盖被测接收机不同状态的控制命令。控制程序集以模块化形式设计,与软件平台相互独立,不同的被测件按需选取模块、配置参数形成不同的程序集,便于程序的移植和升级。控制系统软件使用时,从系统设置界面选取被测件对应的控制程序集,根据控制程序配置进行控制软件初始化,包括软件界面初始化、设备初始化、控制项目及参数的初始化、功能函数调用,驱动接口调用等。

主控模块控制程序运行在Mini-PC主控计算机上,负责主控模块与主控计算机之间的通讯处理,控制主控模块按指令参数进行运行。驱动接口文件为主控模块的驱动程序,主要由USB通讯程序、时序控制模块驱动程序、串行总线模块驱动组成。USB通讯程序负责主控计算机与主控模块之间的数据通讯功能,主要功能包括指令的接收、解析、封装和传输;时序控制模块驱动控制程序负责控制时序模块的初始化、脉冲参数的设置;串行总线模块驱动程序负责控制总线模块将接收到的数据按协议完成时序的转换。

整个系统软件工作流程如图7所示。

图7 控制系统软件工作流程图

4 仿真与测试

为验证系统设计的正确性,采用仿真和实际测试相结合的方式对雷达接收机控制系统进行评估。首先通过Modelsim[10]对功能模块进行仿真,测试功能模块能否满足使用需求,然后通过控制系统对接收机的进行控制,验证控制系统能否完成接收机的控制,达到预定的功能。

4.1 功能模块仿真

针对不同的功能模块编写不同的进行测试文件进行功能仿真,观察时序,验证功能模块的正确性。对于串行总线模块在测试文件中生成需要转换的20位数据,按通信转换要求,将数据转换为20位的串行数据,并提供同步CP信号及传输结束的更新信号update。如图8所示,串行总线模块将20位数据0XB31A5从高位至低位按串行数据发出,满足使用要求。对于时序控制模块输入不同的时序参数,产生8路相关的时序信号,如图9所示。

图8 串行总线时序图

图9 时序信号图

4.2 接收机控制系统测试

在完成控制系统硬件系统和软件系统的调试后,重点测试了控制系统对各型接收机的控制功能。不同的被测件使用配套的适配电缆,控制系统通过软件配置控制程序集初始化主控模块,完成控制指令包括时序的重频周期、相对位置、频率控制、中频增益控制、消隐、自动增益控制等参数的下发以及返回参数的处理,能够稳定的实现对接收机的频率、增益及各种状态的控制,经过多次和长时间的试验,接收机工作稳定,验证了接收机控制系统有效性,达到了良好的使用效果。

5 结束语

本文设计并实现了一种基于FPGA的雷达接收机控制系统,利用VerilogHDL语言和SOPC技术,采用通用性的设计在FPGA上设计了接收机控制系统的硬件系统,实现不同总线转换功能及不同的定时时序要求;控制软件采用柔性设计,通过不同的软件程序集配置,配合专用的适配电缆能够完成不同接收机的控制,达到了设计要求。目前,该系统已投入实际工程应用。

本文构建的控制系统,除了可以应用于各种接收机的控制,还可以应用到其他设备的控制中,具有一定的通用性和可扩展性,有一定的市场应用前景。