10G以太网高速CRC的FPGA实现与优化

◆张 颖 郭志君

10G以太网高速CRC的FPGA实现与优化

◆张 颖 郭志君

(1.陆军参谋部第一通讯站 北京 101100;2.中国电子科技集团第三十研究所 四川 610212)

在现今的以太网中,CRC校验已经得到了广泛的应用。为了解决大流量的CRC校验的实时处理问题,本文提出了一种基于FPGA的流水线式的并行处理结构。并拓展出了通用的校验模块。最后采用工业级的FPGA,并用Verilog硬件描述语言实现。并搭建环境进行试验与验证。

可编程逻辑阵列(FPGA);循环沉余校验(CRC);10G以太网;并行结构;流水线结构

0 前言

0.1 研究背景

在现今的高速网络中,为了保证传输质量和差错控制[1],循环沉余校验(CRC)因其具有很强的误码检验能力和抗干扰能力,被广泛的应用。

在IEEE802.3以太网的标准协议中,CRC校验码是以太网传输帧的重要造成部分。但是常用的传统的CRC校验码的实现方式都是采用串行方式实现,其通过串行移位的方式编码实现,这种方式通过较高的频率得以用简单的电路。但其也存在着很多缺陷,最致命的就是处理数据吞吐量较低,已经难以适应现今网络对于吞吐量日益增长的要求[2]。

随着以FPGA为代表的可编程逻辑器件在网络设备中大规模的应用,给CRC的高速实现提供了一个新的实现途径。CRC校验易于在FPGA中实现,其占用资源少,且很容易实现较高的吞吐量,因此其可以成为高速以太网中差错检验的一种重要实现方式[3]。

0.2 研究现状

在以太网的发展过程中,研究人员对CRC校验进行了很多的研究。Ahmad等人提出过基于流水线的CRC校验算法,该方式的优点是资源占用少,但是处理仍然需要较多个时钟周期[4]。Stavinov等人对CRC的逻辑电路进行了优化,但由于其逻辑表并没有改变,所以其资源占用依然较多[5]。毕占坤等人针对不同位宽的数据设计CRC校验方式,该方法能大大的提升性能,但因为其复杂性以及资源占用高,而无法大规模使用[6]。徐展琦等人提出了一种多通道的CRC实现方式,该方式在性能上有很大的提升,但其设计难度较高,并且对处理器自身的性能要求很高,因而也不适宜大规模使用[7]。

基于上文中等人的研究,在这里提出一种并行方式和流水线方式相结合的CRC实现方法。该方法可以很容易的计算出任意比特长度的CRC校验的值。该方法充分利用的FPGA硬件本身所具有的并行特性、流水线特性、以及高性能的特性;并且设计了任意比特(小于64bit)位宽的CRC效验处理单元,极大的节省了资源。最后通过Verilog进行编码,并进行试验验证。

1 CRC原理

1.1. CRC校验原理

CRC校验[8]的基本原理是线性编码理论。当发送方要发送K位信息序列时,以一定规则产生长度为l位的校验序列,并跟随信息位一起传送给对端。接收方接到序列后,根据校验序列来判断传输是否出现错误。

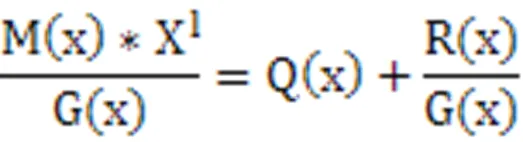

CRC校验码的实现方法就是采用多项式方式循环编码。其先将信息多项式左移l位,然后进行模2除的运算。可以表示为:

如图1所示。

其中R(x)即为CRC序列,M(x)为数据序列,G(x)为生成多项式。

在接收端,接收到比特串后,用模二整除G(x),如果得到的结果等于R(x),那么说明该CRC校验正确,反之则错误。

在IEEE802.3的规定中,生成多项式G(x)的标准格式为:

例如CRC32的表达式即为:

1.2. CRC算法实现

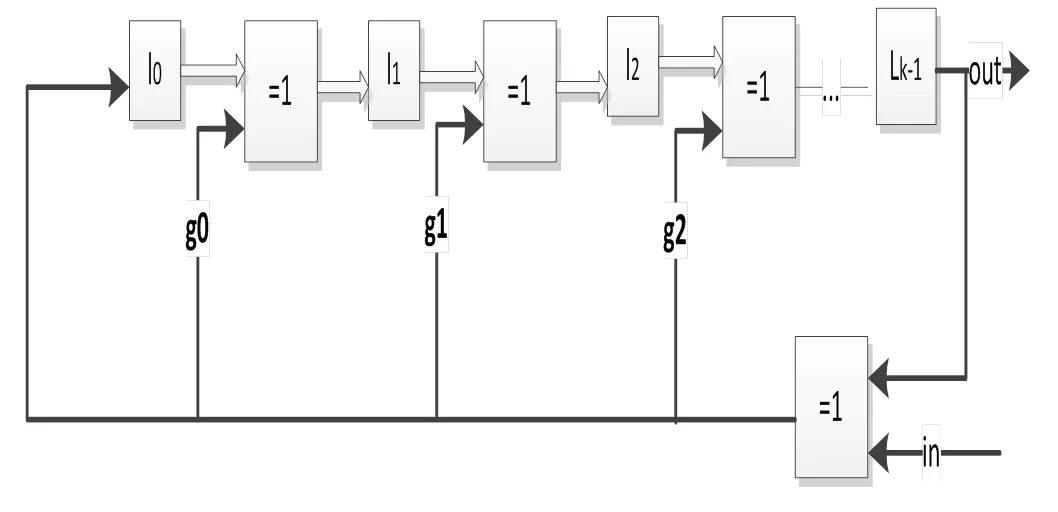

传统的CRC效验实现方法,是通过移位异或的迭代运算来实现的。在实际电路中,是通过线性移位寄存器的级联来实现。其具体实现过程如图2所示。

图2 CRC原理

图2中寄存器状态表示余数,异或表示模2除。l0,、l1、...、lk-1为寄存器的状态,g0,、g1、...、gk-1为生成多项式。其值为0表示断开,为1表示连通。这种电路只需要最基本的寄存器与异或门电路来实现。

但是在实际的应用中,这种实现方式虽然简单,但是其处理速度非常慢,其每个周期只处理一位数据,这样对于较长的数据流来说其时延会非常高。并且这种方式,当有n比特的数据流需要进行处理时,就需要n个寄存器和2n个异或门,这对资源的占用也是一种很大的挑战。

为了适应于硬件加速与高速处理,递推算法和矩阵算法相继被提出[9]。

(1)递推法

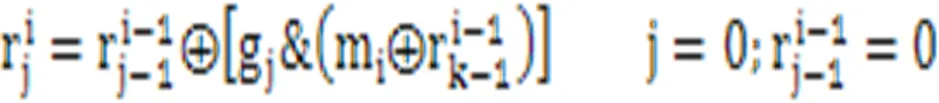

由于CRC算法的串行特性,其CRC当前值只与前一CRC值与输入的前一值相关。若假如数据以8位并行输入,其计算方式应该和8位串行输入计算方式一样。其计算方法为下式。

以此类推就可得到更多的CRC计算式。并且此方法有较好的通用性,并且其可拓展性也较强。

(2)矩阵法

矩阵法适用于并行程度较高的数据。以CRC32为例。

由图2可推倒得出:

其中:

第一,企业应强化相关管理意识,承担共享单车回收管理的主要责任。第二,企业应加强与政府之间的合作,合理有效利用政府的资金、技术、人员等支持,同时发挥企业与政府双重作用,更好地建立健全共享单车回收维修管理制度,实现资源更优配置。第三,企业可与相关同行企业合作,降低人力成本,更好的回收损坏报废共享单车,减轻城市交通压力以便方便政府对于城市慢行交通系统管理。第四,企业应建立健全单车回收维修管理体制,为相关维修人员提供学习培训的机会。

由上式可以得出:

矩阵运算适合大规模并行数据的运算,但由于其运算复杂,资源消耗多,应用并不是十分广泛。

2 以太网中的CRC设计

现今高速的10G以太网已经广发的普及。FPGA+PHY芯片的以太网处理方案也变得越来越多。所以基于FPGA的CRC设计就显得尤为重要。

2.1. 以太网中的CRC校验控制

根据IEEE802.3协议,以太网帧(包含CRC校验字段)的结构如图3所示。

图3 以太网帧结构

在实际的网络应用中,发送和接收双方约定生成多项式和位宽,以实现数据通信的差错控制。其具体步骤如图4所示。

图4 以太网帧的CRC校验

在网络设备接收到以太网数据帧后,先送到MAC层进行编码处理。在MAC层中进行CRC校验。当校验结果正确,则传输到上层进行更多的处理;当校验错误时就进行重传操作。这样便保证了数据传输的完整性和可靠性。

具体的CRC校验过程为:(1)FCS效验区域字段高低比特翻转。(2)寄存器初值置为1。(3)计算CRC(采用CRC算法逻辑)。(4)CRC取反。(5)取反后的CRC字段高低比特翻转。这样就得到了以太网的CRC字段的值。

2.2.流水线CRC校验设计

在10G以太网中,通常采用64位并行数据来进行处理。而以太网的数据不都是64的整数倍,那么肯定就会出现不够64位的边界问题。在传统的设计中,对于满64位的则采用CRC32进行校验计算,对于不够64位的部分,采用CRC8、CRC16等来进行计算。这就导致设计中必须有以上对应的CRC计算模块,这样就占用了资源。

本文现设计一个流水线结构的CRC编码器。

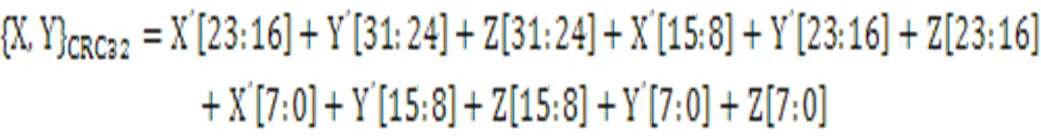

设X的CRC32为X’[31:0],Y的CRC32为Y’[31:0],X’的CRC32为Z[31:0],则可以得出X的拓展序列{X,Y}的CRC32为:

那么对于8-64位的任意位宽的输入,的计算中间节点可以表示为:

图5表示一个流水线的CRC编码器。

图5 流水线CRC编码器

模块CRC8为8位输入的CRC模块,CRC_EXPEND模块为N位CRC模块(N=8*k,k=1,2,...)

以上的流水线模块可以输出任意N位的CRC校验值。通过SIZE选择器来控制不同位宽的输出。这样就降低了存储空间。

CRC校验计算包含大量的异或运算。采用适当的方式对异或运算并行,也可以大大的降低总的时延。

图6 传统异或运算

图7 优化后的异或运算

这样虽然所进行的异或次数一样,但是前三次可以并行运算,这样跟传统的方式相比就大大的降低了时延。对于多维的数据,这种方式的优化效果更明显。

3 试验与验证

3.1 仿真验证

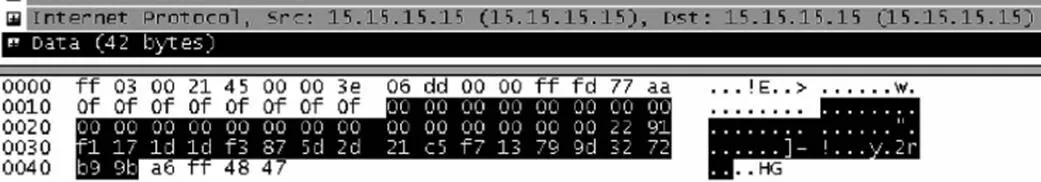

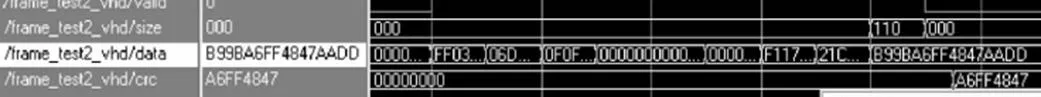

验证CRC算法的正确性,通过Wireshark和ISE仿真软件来抓包来进行验证。验证结果如图8,图9所示。

图8 一个以太网数据包

图9 ISE仿真结果

从上图可以看出,仿真结果的CRC运算结果的值为A6FF4878,与Wireshark抓包的结果一致,这样就验证了其正确性。

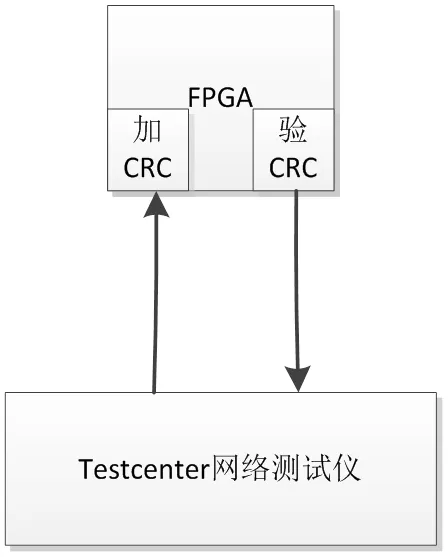

3.2 试验验证

采用Verilog语言,在赛灵思的Spartan-6,FPGA进行编码验证。采用10G的Testcenter网络测试仪进行吞吐量的测试。10G网络测试仪试验环境如图10所示。

图10 测试环境

本试验采用200M时钟,64位,即12.8GB的吞吐量,完全满足10G的要求,经测试,也完全能达到10G吞吐量。

本文所设计的CRC编码器的资源占用情况对比,如表1所示。可以看出在资源节省方面也有很大的提升。

表1 本文所设计的CRC编码器的资源占用情况对比

4 结束与总结

本文CRC运算的效率问题。提出了一种流水线的CRC效验短发,并对其中的组合逻辑部分进行了并行化的改进。通过这两种方式,节省了芯片的逻辑资源,并且降低了时延,提高了系统的性能。并且通过软件仿真,以及实际网络测试仪测试两种方式进行了验证,证实了上述的性能的提升。

[1]王新梅,肖国振.纠错码:原理与方法[M],西安:西安电子科技大学出版社,1991.

[2]张友亮,刘志军,马成海.万兆以太网MAC层控制器的FPGA设计与实现[J].计算机工程与应用,2018.

[3]刘璐,武明亮,何俊强.基于循环冗余校验码的差错控制分析与实现[J].成都大学学报(自然科学版),2011.

[4]AhmadA, Hayatl. Selection of polynomials forcyclic redundancy check for the use of high speed embedded: An algorithmic procedure [J]. WSEAS Transactions on Computers, 2011.

[5]Stavinov E. A practical parallel CRC generation method [J]. Circuit Cellar the Magazine for Computer Applications, 2010.

[6]毕占坤,张羿猛,黄芝平,等。基于逻辑设计的高速 CRC并行算法研究及其FPGA实现[J]。仪器仪表学报,2007.

[7]徐展琦,裴昌幸,董淮南。一种通用多通道并行CRC计算及其实[J]。南京邮电大学学报,2008.

[8]Ramabadran T V, Gaitonde S S, A tutorial on CRC computations [J]. IEEE Micro, 1988.

[9]张树刚,张遂南.CRC校验码并行计算的FPGA实 现[J]。计算机技术与发展,2007.