基于A T 24C 01 的存储电路设计与应用

徐锦钢 鄢 妍

(1.江西师范大学科学技术学院,江西 南昌 330032;2.江西机电职业技术学院,江西 南昌 330032)

0 引言

工程人员在从事电路设计工作时, 有时会提出数据存储的功能需求, 此时在电路中就必须加入存储器。 目前市面上的存储芯片种类繁多, 比如NAND flash、NOR flash、EEPROM、磁盘等。 本文采用的存储芯片AT24C01 属于EEPROM 类型, 具有价格低廉、 功耗低、 易操作等优点, 特别适合存储数据量不太大的场合,故本文选用AT24C01 作为电路的存储芯片。

1 电路连接

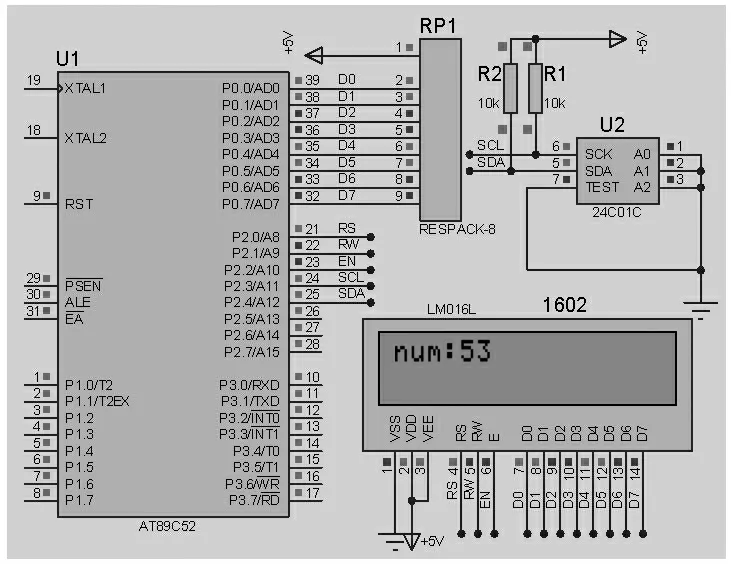

图1 电路连接图

电路连接图如图1 所示, 主要包括AT89C52 单片机、AT24C01、1602 液晶屏和2 个10K 上拉电阻等元器件,系统上电后,每秒让num 值加1,0-99 循环计数,通过仿真,从图1 中可以看到在num 计到53 时,断电再次上电,系统从53 开始加1 计数,说明断电前的53已经顺利写入到了AT24C01 中, 再次上电时又顺利地从AT24C01 中读取了53, 说明在本文设计的电路中,存储器读写正常,软硬件设计正确,功能正常。

1.1 AT24C01 存储芯片介绍及其与单片机的接口电路

AT24C01 是ATMEL 公司生产的一种EEPROM 型存储芯片,可以电擦除,存储容量为1024 位。也有其他容量的型号可供选择, 比如AT24C02 的容量为2048 位。通过2 线制IIC 总线接口与单片机或其他MCU 进行数据传输,传输遵循IIC 通信协议标准。

下面阐述AT24C01 的电路连接问题:AT24C01 一共有8 个管脚,其中4 脚GND 接地;8 脚VCC 为电源端,接+5V。1、2、3 脚共同组成器件地址选择端,本设计因为只使用了1 片AT24C01,所以将1、2、3 脚接地,表示本设计中的AT24C01 器件地址为0 号地址。 5 脚SDA和6 脚SCK 是1 组IIC 总线接口, 分别接至单片机的P2.4 和P2.5 脚,同时分别通过10K 电阻上拉,使得总线空闲时,SDA 和SCK 均明确为高电平。

1.2 IIC 串行总线介绍

1.2.1 IIC 总线的主要特点

IIC 总线是飞利浦推出的一种串行总线,具备多主机系统所需的包括总线裁决和高低速器件同步功能。IIC 只有两根双向信号线: 数据线SDA 和时钟线SCK,使得在设计时大大减少了硬件接口开销。 每个连接到总线上的IIC 器件都有一个用于识别的器件地址编码, 该地址由外部地址引线和内部硬件电路同时决定, 每个器件既可作为接收器, 也可作为发送器。 因此,IIC 总线上可以挂多个器件, 而每个器件都有唯一的地址, 这样可以标识通信目标。 数据的通信的方式采用主从方式, 主机负责主动联系从机, 而从机则被动回应数据。

1.2.2 IIC 总线的数据传输

(1)数据传输格式

每个字节须保证是8 位长度。数据传输时,先传最高位, 每个被传输字节的最后都须跟随一位应答位,即一帧数据共有9 位。

(2)数据帧格式

IIC 总线上传输的数据除了包括真正的数据信号,也包括地址信号。 在起始信号后面必须传送一个从机地 址 (7 位), 第8 位 是 数 据 的 传 送 方 向 位 (接 收/发送),“1”表示接收数据,“0”表示发送数据。 数据传送总是由主机产生的终止信号结束。 但是, 若主机希望继续占用总线进行新的数据传送, 则可以不产生终止信号,马上再次发出起始信号对另一从机进行寻址。

(3)数据有效性

在SCL=1 期间, 数据线SDA 必须保持稳定;在SCL=0 时,数据线SDA 才允许改变。

(4)起始信号和终止信号

起始信号为: 在SCL=1 期间,SDA 出现下降沿;终止信号为:SCL=1 期间,SDA 出现上升沿, 并且保持的时间也做了限制。

(5)应答信号和非应答信号

主机往总线上发送一个字节的数据后,释放总线,从机会把总线拉低(即产生应答信号),以表示这一字节发送成功。 同理主机从总线上读取完一个字节的数据后, 主机会把总线拉低, 通知从机该字节的数据接收成功。

(6)器件地址

对 于AT24C01, 由 于 在 本 设 计 中,A2、A1、A0 已 固定接低电平,即000,而高四位固定为1010,这7 位组成了器件地址。 最后一位R/W 是读写方向控制位,0为写方向,1 为读方向,所以本设计中的AT24C01 器件地 址 为: 读 地 址 为 10100001, 即 0x91; 写 地 址 为10100000,即0x90。

(7)写操作

向AT24C01 的某个单元地址里写一个字节的数据,其操作顺序为:起始,写器件地址,应答,写单元地址,应答,写数据,应答,终止。 单片机发送起始信号,然后发送1 个字节的控制字, 再发送1 个字节的AT24C01 单元地址, 在发出这些字节都得到AT24C01应答后, 单片机接着发送8 位数据, 最后发送1 位停止信号, 这样1 个字节数据被写入了AT24C01 的指定单元中。

(8)读操作

从AT24C01 某个指定单元地址读取数据, 其操作顺序为:起始,写器件地址+0(下一个字节为写),应答,写单元地址,应答,起始,写器件地址+1(下一个字节为读取),读取数据,终止。 单片机在起始信号后先发送含片选地址的写操作控制字,AT24C01 应答后再发送1 个字节的指定单元地址,AT24C01 应答后再发送1个含有片选地址的读操作控制字, 此时如果AT24C01做出应答,该指定单元的数据就会被读出[1]。

2 程序编写

读操作和写操作是AT24C01 最关键的两个操作,根据上文中对读字节和写字节操作时序的分析, 本文编写了完整的AT24C01 读、写操作函数,如下文所述。

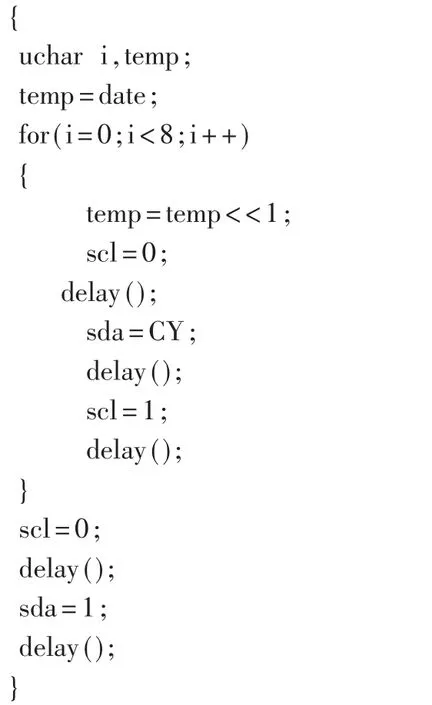

2.1 AT24C01 写操作函数

void write_byte(uchar date)//写1 个字节数据

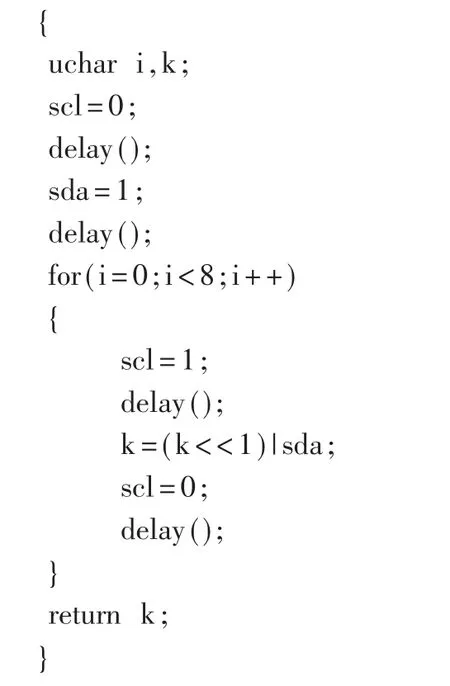

2.2 AT24C01 读字节操作函数

uchar read_byte()//读1 个字节数据

3 结束语

本文阐述了基于单片机的AT24C01 数据读写操作方法,描述了AT24C01 的特点、读写操作时序,编写了完整的AT24C01 读写操作程序代码。 通过AT24C01 存储器的软硬件设计和仿真, 为以后在电路设计领域中进行更为深入的研究打下了基础。