基于Sigrity的高速串行总线GTX仿真分析

闫哲 张艳飞 杜晓华

摘要:GTX是一种高速串行收发器,具备高速率、低功耗的特点,可用于实现收发双向独立传输。在Xilinx的Virtex6 FPGA中灵活配置,且与其他逻辑资源紧密联系。在Cadence Sigrity环境下调用GTX的IBIS模型,添加从PCB板提取的S参数,对Virtex6 FPGA GTX收发器进行信号完整性仿真,模拟真实应用环境,对接收眼图进行分析。仿真结果证明,GTX能够实现在6 Gbps以下数据速率的高可靠性传输,能够满足大容量高速数据传输的要求,通过修改过孔,提出了一种优化传输系统的方法。

关键词:GTX;Sigrity;信号完整性;仿真;眼图

中图分类号:TP336文献标志码:A文章编号:1008-1739(2019)13-63-4

0引言

随着超大规模集成电路技术的发展,IC芯片的内核供电电压逐渐降低,但系统时钟频率和I/O数据传输速率不断提升,这就要求具备低压差电平标准的高速传输总线需要具备良好的信号完整性才能应对传输线带来的噪声和干扰[1]。Xilinx Virtex6系列FPGA的高速串行GTX收发器发送和接收端双向独立,具备单工和全双工模式,数据传输速率范围600 Mb/s~6.6 Gb/s。

本文利用Cadence公司的仿真分析软件,在Sigrity环境下对GTX收发器的高速传输性能进行信号完整性仿真分析,利用仿真结果来加强对GTX高速收发器的传输特性的认识,以指导PCB布线设计工作,提高传输可靠性。

1 GTX高速串行仿真

随着高速集成电路信号切换速率的不断提高,IBIS模型作为一种准确、公开的仿真模型,是反映芯片驱动和接收电气特性的一种国际标准,所记录的驱动源输出阻抗的上升、下降时间和输入负载等参数,适合于对高频效应进行计算与仿真(如振铃、串扰等),能够在不涉及器件的内部细节的情况下,更快、更准确地得到仿真结果[2]。因此,采用Virtex6 GTX的IBIS模型进行仿真分析。

1.1 IBIS模型

IBIS模型的基本输入结构包括电源(Power Clamp)和地的电平钳位(GNDClamp)保护电路、引脚封装的寄生参数(C_pkg,R_pkg,L_pkg)以及硅片本身固有的寄生电容(C_comp),对于输入结构而言,没有缓冲器的上拉和下拉结构电路[3]。

1.2 Sigrity仿真环境

Cadence Sigrity工具包内有Sigrity Power SI,Sigrity Power DC,SPEED2000等仿真工具,可以完成高速电路设计中的信号完整性(SI)分析、电源完整性(PI)分析和Sigrity System SI,并提供宽带S参数提取及频域仿真等,针对于高速芯片的全面自动化信号完整性系统设计,准确地仿真评估环境,确保串行链路接口的可靠实现。采用Sigrity Power SI对Virtex6 FPGA的PCB信号网络进行仿真,提取GTX发射和接收端的S参数;采用Sigrity System SI,建立从发射到接收端的串行传输链路模型。

1.3 IBIS模型在Sigrity仿真软件中的应用

IBIS在板级仿真中应用广泛,可精确模拟PCB使用情况,对避免PCB投产前的信号完整性问题能起到参考作用。

使用Sigrity Power SI对GTX发射和接收的S参数进行提取。S参数为散射参数,它是对传输路径上的各端口之间频率相应关系的数学表达。对于一个多端口的S参数模型器件,当一个信号从器件的某一端口进入时,S参数描述的是该信号在传输网络中通过不同端口的传输特性和反射特性[4]。

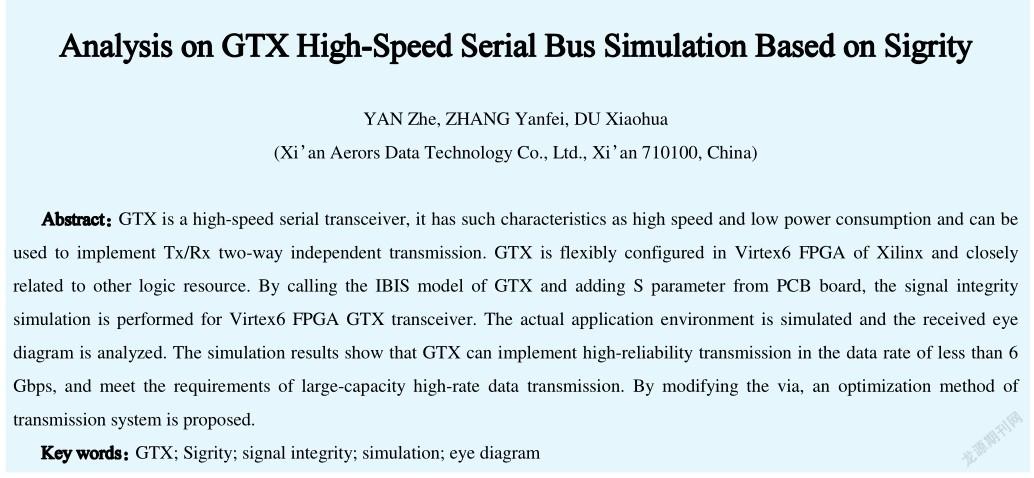

在Sigrity System SI中,建立通道模型,加载GTX输入输出模型,将Power SI中得到的S参数加载到通道模型中,进行高速串行仿真,模拟GTX收发器的收发过程,得到GTX发射波形、接收波形以及接收眼图。整个仿真流程侧重在模拟受应用环境影响后的信号的波形,是进行PCB布线设计验证仿真的重要方法。GTX高速串行通道模型如图1所示。

完成建立模型后,分别加载GTX_TX,GTX_RX的IBIS模型,同时加载S参数。

设置编解码方式为8B/10B的编解码方式,8B/10B是面向字节的编码规范,目的是将8B位宽数据转换为5个以上不连续的“1”或“0”的10位比特碼,减小数据流中长连“1”和长连“0”字符串,从而平衡“0”和“1”的概率,获取更好的直流平衡型,进而提高传输速率。GTX收发器内部包含一个执行8B/10B编码的硬核单元,实现对发送端数据进行编码,不需要消耗FPGA资源。

设置激励码流为PRBS7,它是7阶伪随机序列,因为最接近8B/10B编码的游程长度5,因此一般用来测试8B/10B高速通道。

1.4眼图

眼图是一种观察信号完整性直观有效的方法,串行信号在传输过程中受到传输介质特性、噪声等因素的影响发生码间干扰和抖动等问题,都可以通过眼图测量来进行评价,以此判断系统性能和串行信号质量。

通常,用相关的眼图参数来定义眼图的属性,如眼高(Eye Height)、眼宽(Eye Width)、Q因子(Q factor)、抖动(Jitter)、眼幅度(Eye Amplitude)和眼交叉比(Eye Crossing Percentage)等。其中,眼高是眼睛垂直张开度的度量,理想的眼图眼睛张开度等于垂直眼幅度。实际情况下,噪声会使眼睛闭合,因此,眼高的测量决定了噪声引起的眼睛闭合程度,垂直方向越高,信号则可以抵抗较大的干扰或者串扰;高速数据信号的信噪比也直接用眼高值来表示。眼宽是眼睛水平张开度的测量,是通过计算测量眼图2个交叉点的统计平均值之间的差异而得,水平方向越宽,则说明干扰越小。

眼高和眼宽表征了系统抗干扰能力的大小。抖动是数据码元发生变化的实际位置与理想位置的时间偏差,抖动是信号的水平波动,会随数据速率提高而增加,造成误码。

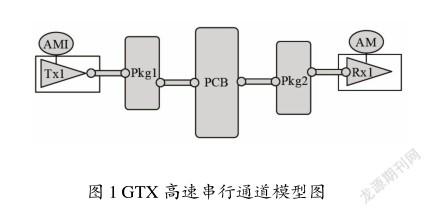

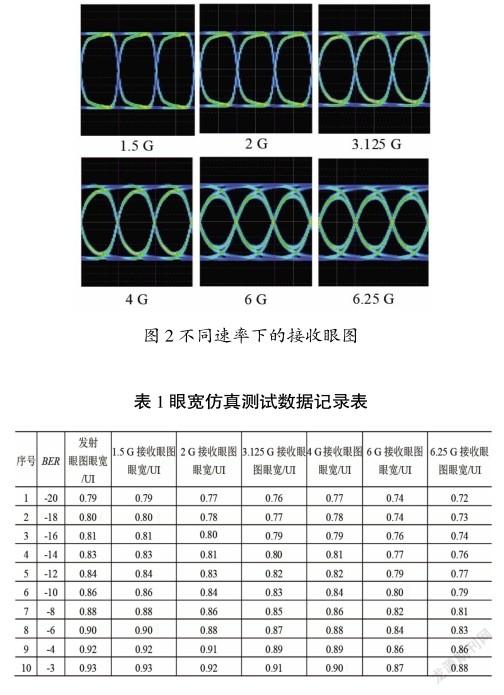

将数据速率从0.5 G设置到6 G开始仿真,在不同速率下,获得接收端的眼图结果如图2所示。眼高仿真结果数据记录表如表1所示,眼宽仿真结果数据记录表如表2所示。

2仿真結果分析

分析图2、表1和表2可以得出:

①随着速率的提升,在1.5,2 G速率下,接收端眼图与发送端眼图的眼高相差不大,说明仿真链路受串扰和码间干扰的影响很小。

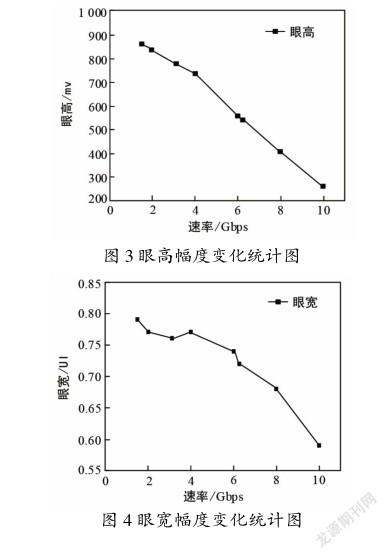

②在3.125,4 G速率下,接收端的眼图眼宽虽然变化很小,但眼高开始出现大幅度下降,尤其在4~6 G之间的眼高值急速下降,如图3所示,说明在系统链路传输大于4 G高速信号时,已经受到码间干扰的影响。

③由图4观察4~8 G眼图,从6 G开始,眼图抖动变得明显,说明系统链路间出现了大量误码。

3仿真结果

在信号完整性的干扰分析中,噪声耦合到临近的传输线上,会因为传输线、过孔孔径大小和厚度的变化引起临近线上有的多处阻抗不连续点,干扰的噪声也会反复震荡叠加,最终可能会产生更大的噪声。本文提出通过优化过孔孔径的方法对系统链路进行优化,通过眼图仿真分析优化效果。

3.1过孔模型

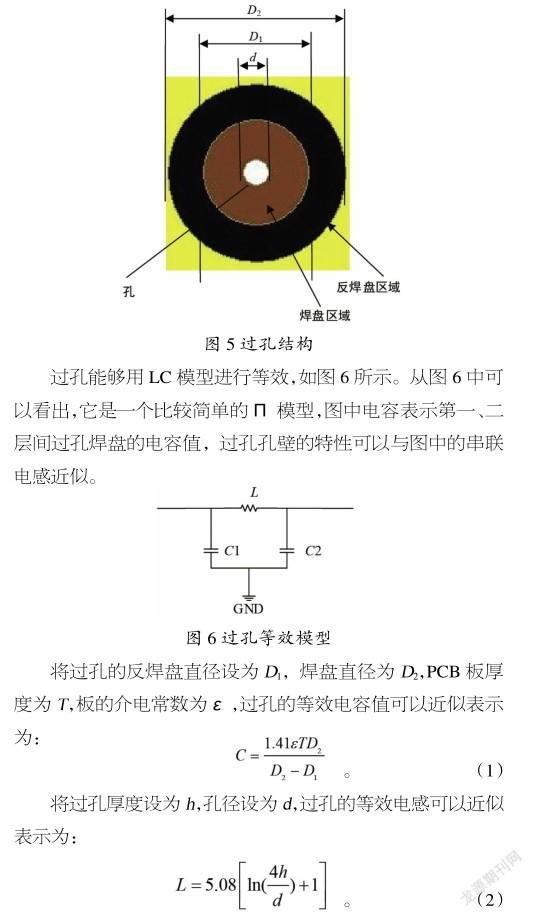

过孔结构图如图5所示,焊盘直径、反焊盘直径和过孔残桩长度等因素影响过孔上的寄生电感和电容,进而引起过孔等效阻抗的变化。

对过孔寄生电容的感性分析可知,这种电容效应会影响信号的边沿速率,也会使特性阻抗发生变化,影响高速信号的上升时间。由式(1)和式(2)可知,使用相同材料,在孔径厚度、PCB板厚度不变的情况下,减小孔径可以减小寄生电容,进而减小高速信号边沿上升时间。

3.2仿真优化

以4.8 GHz传输信号为例,对过孔孔径进行优化,从0.2mm降低至0.1 mm。仿真眼图眼高如表3所示。

从图7可以看出,对过孔进行优化后,眼高的值增大,更改过孔孔径,优化了输入端的反射系数,码间干扰减小,对系统传输链路干扰的影响减小。

4结束语

通过加载IBIS模型,提取实际PCB板传输线S参数,在Cadence Sigrity环境下对Virtex6 GTX高速串行收发器进行信号完整性仿真,说明Virtex6 GTX可以实现6 Gbps以下信号的高速串行传输,但对于6 Gbps以上的高速信号传输则会出现噪声干扰、串扰和码间干扰等问题,容易造成较大传输误码。分析过孔结构,对过孔的孔径进行优化,通过对眼图的对比测试,可以优化传输端口的反射系数、减小码间干扰,提高了高速信号传输的性能。

参考文献

[1]陈兰兵,钟章民,肖定如,等.Cadence高速电路设计:Allegro Sigrity SI/PI/EMI设计指南[M].北京:电子工业出版社,2014.

[2]方国华,刘光斌,余志勇.基于IBIS模型的信号完整性仿真分析[J].电子产品可靠性与环境试验,2004(6):68-71.

[3]黄贵帅.基于IBIS模型的数字IC应用验证仿真技术研究[D].西安:西安电子科技大学,2014.

[4] Bogatin E.信号完整性与电源完整性分析:第2版[M].李玉山,刘洋,等,译.北京:电子工业出版社,2015.