基于FPGA的AMI编解码设计

左磊 程煜洋 赵晓东 方圆

摘 要:在基于FPGA的基带传输系统研究中,通过对AMI码型的研究,提出了一种通过Altera公司Cyclone Ⅱ系列EP2C35F672C6芯片实现AMI编解码设计的方法。使用Quartus Ⅱ和ModelSim仿真平台对设计方法进行仿真,结果符合AMI编解码原理,解码输出与基带信号一致,最终结果符合预期。AMI编解码能够实现在电路相对简单的情况下,即使码元极性与发端相反,接收端也能正确接收,为信号传输带来了一种可靠的方法。

关键词:FPGA;AMI;编解码

中图分类号:TN912.3 文献标识码:A 文章编号:2096-4706(2020)20-0085-03

AMI CODEC Design Based on FPGA

ZUO Lei,CHENG Yuyang,ZHAO Xiaodong,FANG Yuan

(North China University of Technology,Beijing 100144,China)

Abstract:In the research of FPGA-based baseband transmission system,through the study of AMI code pattern,a method to realize AMI CODEC function through Alteras Cyclone Ⅱ series EP2C35F672C6 chip is proposed. Using Quartus Ⅱ and ModelSim simulation platform to simulate the design method,the result conforms to the AMI CODEC principle,the decoding output is consistent with the baseband signal,and the final result is in line with expectations. AMI CODEC can realize that under the condition that the circuit is relatively simple and the polarity of the code is opposite to that of the originator,the receiver can receive it correctly,which brings a reliable method for signal transmission.

Keywords:FPGA;CMI;CODEC

0 引 言

AMI码全称是传号交替反转码,其对应的波形正负脉冲交替,无直流成分,且具有很小的低频成分,在不允许直流、低频成分通过的信道传输中大量使用。常见的数字基带传输码有:AMI码、NRZ码、RZ码、CMI码和曼切斯特码。AMI是一个比较有代表性的码型,高、低电频分量少,能量集中在频率为1/2码速处;编解码电路简单,且可以利用传号极性交替这一规律来观察误码情况。随着科技的快速发展,电子计算机、大规模集成电路、超大规模集成电路以及微处理器技术得以更新换代,FPGA器件作为超大规模、超高速的可编程逻辑器件,也得以迅猛发展。由于其具有高集成度、高速、可编程、硬件描述语言的可修改性、低功耗、开发周期短、硬件与软件并行性等优点而被广泛应用。笔者所在实验室在2020北京市的大学生科学研究与创业计划项目中,研究的对象是基于FPGA的程序设计,在相关专业知识的的启发下,对基于FPGA的AMI编解码的设计展开了研究。对AMI的编码规则、解码方法进行详细分析,利用Quartus Ⅱ软件设计程序,再通过ModelSim平台进行仿真。本论文阐述了对基于FPGA的AMI编解码的设计实现,设计原理和结果分析。

1 AMI编解码规则

AMI码是传号交替反转码,编码规则是将消息码中的“1”(传号)交替变换为“+1”和“-1”,而“0”(空号)保持不变。例如:

消息码:1 0 1 1 0 0 0 1 1 0

AMI码:-1 0 1 -1 0 0 0 1 -1 0

AMI码是具有正、负、零三种电平的脉冲序列。可以看成单极性波形的变形,“0”仍然为低电平,“1”时正负电平交替变换。

由AMI碼的编码规则,就有了解码的设计思路:当AMI码为“+1”或“-1”时,输出“1”;AMI码为低电平时,输出为“0”。

2 AMI编解码系统设计

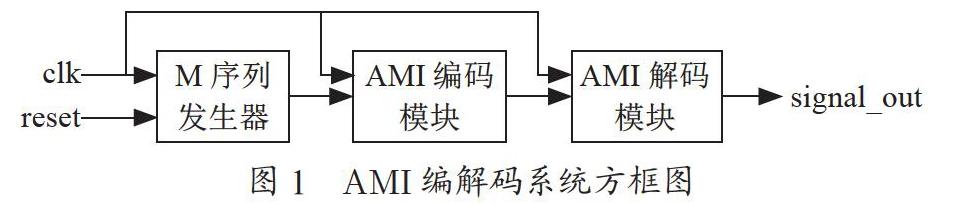

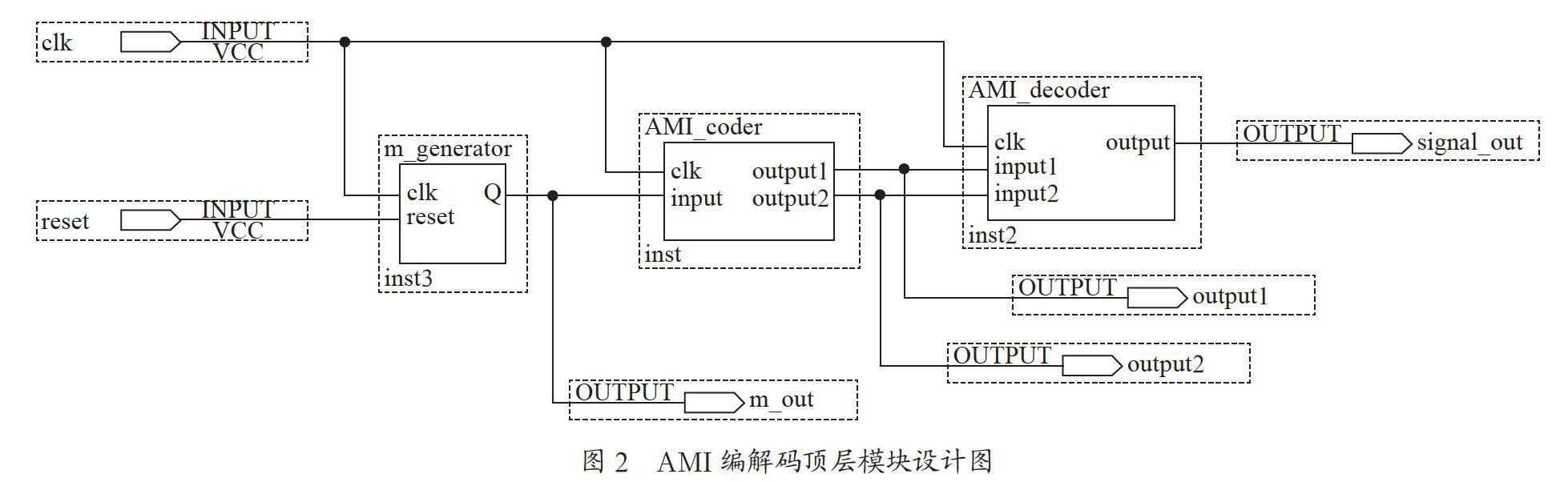

AMI编解码系统方框图如图1所示,该系统由输入信号clk、reset、M序列发生器模块、AMI编码模块和AMI译码模块组成。

顶层模块设计图如图2所示,顶层设计模块以Altera公司旗下的Quartus Ⅱ软件作为开发平台;采用的FPGA芯片为Cyclone Ⅱ:EP2C35F672C6,该芯片工作电压低,适应温度范围大,逻辑数组块数量多,可实现高集成度,高速的逻辑运算;各个模块的设计语言为VHDL语言,将各模块设计完成后生成bsf文件,将各模块的bsf文件搭建构成了AMI编解码的顶层模块。顶层模块输入为时钟信号clk和复位信号reset;输出为M序列发生器输出m_out、编码模块两路输出output1,output2、译码模块输出signal_out。

M序列发生器模块:伪随机序列用的是M序列作为基波信号,特征多项式为1+X3+X4,产生了周期为15的伪随机序列;M序列发生器产生伪随机序列在受复位信号reset控制,当复位信号为低电平时,开始产生伪随机序列。

AMI编码器模块:输入信号为M序列信号m_out和时钟信号clk,输出为两路输出信号output1和output2,规定输出“1”“0”为AMI码中的“+1”,输出“0”“1”为AMI码中的“-1”。当“1”进入AMI编码器时,两路输出信号“0”“1”交替变换输出;当信号为“0”时,输出信号都为“0”;两路输出信号都在时钟上升沿处发生变化。

AMI译码器模块:输入信号为AMI编码器输出的两路信号,由编码器的设计思路,将两路信号相或的值输出,如果输入的两路信号是“0”“1”或者“1”“0”时,相或的结果为“1”;如果两路信号都为“0”时,相或结果为也“0”。由此就能得到编码前的原M序列信号signal_out。

2.1 伪随机序列发生器设计

产生M序列的原理图如图3所示,产生的M序列码满足特征关系式1+X3+X4。每个时钟上升沿到达,在复位信号为高电平时复位,输出为高电平;在复位信号为低电平,每个时钟上升沿到达时,各个寄存器依次移位,每次将a0与a1的值相或赋给a4,并输出a0。

2.2 AMI编码模块

如图4所示,是AMI编码模块的流程图,初始状态下c为“0”。AMI编码方式是先判断输入的M码为“1”还是“0”;如果是“1”且c=“0”则两路输出信号交替“0”,“1”输出;如果M码是“0”且c=“1”,则两路信号均输出“0”。c为标志位,当每次输出为1时,无论输出是‘1‘0,还是‘0‘1,标志位c都取反。

代码实现如下:

if input='1' then

if c='0' then --初始标志位c为0

output1 <='1';

output2<='0'; --“10”为“+1电平”

c:=not c; --交替變换信号

else

output1<='0';

output2<='1'; --“01”为“-1”电平

c:=not c; --交替变换信号

end if;

else

output1<='0';

output2<='0'; --“00”时为“0”电平

end if;

end if;

2.3 译码模块

AMI译码模块较简单,这里不再给出流程图,将两路输入input1和input2相或输出,当输入是“01”或者是“10”时,相或的结果为“1”,当输入是“00”时,相或结果为“0”。代码实现为:

begin

if clk'event and clk='0' then ----时钟上升沿到达

output<=input1 or input2; ----将两路输入相或输出

end if;

3 仿真结果与分析

利用Quartus Ⅱ作为编译设计软件,设计结果在ModelSim上进行仿真。对AMI编解码顶层模块进行仿真,仿真结果如图5所示。在测试文件testbench中,设置时钟周期为20 ns,且时钟初始时刻为0;设置复位信号reset初始为高电平,持续100 ns后变为低电平。

由顶层模块仿真波形图可以看出,复位信号reset=1时,产生的M序列信号为1;在100 ns时,复位信号reset=0,M序列输出为1,此时刚好是时钟上升沿,电路开始编码,输出的引脚output1和output2信号依次“0”,“1”变换,符合编码规则;在下一个时钟上升沿到来时,开始译码,此时输出的波形是signal_out,等于output1和output2信号的相或,输出为高电平,符合译码规则。输出的m_out在第一个时钟上升沿开始编码,然后再经过一个时钟上升沿开始译码输出,所以m_out信号与signal_out信号相差两个时钟上升沿。之后的output1和output2也符合AMI编码规则,译码后的signal_out信号也与m_out信号一致,符合预期设计。

4 结 论

本次设计基于Altera公司的Quartus Ⅱ软件开发平台和ModelSim仿真实验平台,使用FPGA器件EP2C35F672C6芯片,利用VHDL硬件描述语言完成了AMI编解码电路的设计与仿真。AMI编码确定的基带信号无直流分量,且低频分量很小,使得调制与解调的误码率大大减小;AMI码还具有检错能力,如果因为极性交替使得传输过程中出现了误码情况,很容易检查出这种错误,如果若码元极性与发端相反,收端也能正确接收,AMI码为信号传输过程提供了可靠的方式。运用FPGA来实现AMI码,与采用专用集成电路相比较,前者不仅给调试带来方便,而且可以把编解码电路以及其他辅助电路集成在同一块FPGA芯片中,减少了外界元件,提高了集成度,具有很大的编程灵活性。

参考文献:

[1] 顾涵.基于FPGA的类曼彻斯特编码发送模块设计 [J].科技传播,2014,6(4):209-210.

[2] 李永军,田亚芳,徐晓蓉,等.基带传输系统中AMI码性能分析与仿真 [J].河南大学学报(自然科学版),2012,42(2):203-207.

[3] 谢维华,庹新宇,楊瑞娟.一种用VHDL语言实现的帧同步算法 [J].空军雷达学院学报,2003(2):17-19.

[4] 綦晓华.基于FPGA的数字视频监控系统的研究与设计 [D].武汉:武汉理工大学,2009.

[5] 吴成静.模拟信号在光纤中的传输方案研究 [D].西安:西安工业大学,2015.

[6] 孔利东.基于FPGA的数据采集与处理技术的研究 [D].武汉:武汉理工大学,2007.

[7] 包晗.FPGA器件的应用研究 [D].大连:大连海事大学,2006.

[8] 李雨璇,任峻.数字基带系统(AMI码)的仿真设计与分析 [J].福建电脑,2018,34(4):137-138+5.

[9] 沈媛媛,梁浩.基于FPGA的HDB3编码器设计与仿真 [J].仪器仪表与分析监测,2012(4):17-19.

作者简介:左磊(2000—),男,穿青人,贵州毕节人,本科在读,研究方向:通信工程;程煜洋(2000—),女,汉族,湖北武汉人,本科在读,研究方向:通信工程;赵晓东(2000—),男,汉族,宁夏石嘴山人,本科在读,研究方向:通信工程;方圆(1999—),女,汉族,福建福州人,本科在读,研究方向:通信工程。