基于FPGA的CMI编解码设计

赵晓东 程煜洋 左磊 方圆

摘 要:在基于FPGA的基带传输系统研究中,对基带传输信号的码型有严格的要求。通过对CMI码型的研究,提出了一种通过Altera公司Cyclone Ⅱ系列EP2C35F672C6芯片实现CMI编解码功能的方法,并给出了Quartus Ⅱ仿真平台实现CMI编解码的设计方案。通过这种方法得出的CMI编解码码型符合编解码原理,解码输出与基带信号一致,最终结果符合预期。能够适应多种集成电子电路设计场合,通过仿真帮助达到预期效果。

关键词:FPGA;CMI;编解码

Abstract:In the research of baseband transmission system based on FPGA,there are strict requirements for the code type of baseband transmission signal. Through the research of CMI code type,a method to realize CMI coding and decoding function through Alteras Cyclone Ⅱ series EP2C35F672C6 chip is proposed,and the design scheme of Quartus Ⅱ simulation platform to realize CMI coding and decoding is given. The CMI codec pattern obtained by this method accords with the principle of CODEC,the decoding output is consistent with the baseband signal and the final result meets the expectations. It can adapt to a variety of integrated electronic circuit design occasions,and help achieve the desired effect through simulation.

Keywords:FPGA;CMI;CODEC(coder-decoder)

0 引 言

随着科技的快速发展,电子计算机、大规模集成电路、超大规模集成电路以及微处理器技术的迅猛发展。基带传输系统设计成为了必要。在集成电路领域中,FPGA器件是超大规模、超高速的可编程逻辑器件,由于其具有高集成度、高速、可编程、硬件描述语言的可修改性、低功耗、开发周期短、硬件与软件并行性等优点而被广泛应用。文献[1]针对数字光纤通信传输信号码型的要求,提出了一种基于可编程逻辑器件EPM240T100C5实现CMI编解码的方法。文献[2]介绍了一种新的编程思路实现CMI编码,在Max+ Plus Ⅱ开发平台上使用VHDL编程实现CMI编码,并得到仿真波形。文献[3]针对LDPC码进行了两种算法的设计,一种是直接基于校验矩阵进行递归求取,另一种则通过部分生成矩阵进行设计,并对两种架构分别进行设计、分析和比较。文献[4]研究了八路视频信号传输中数字复分接的设计和反向数据信号传输中线路码的编解码设计。在文献[5]中,研究者设计出一种将数字化信号的传输和光纤通信结合到一起的方案,通过串并转换及CMI编码后,经过光纤将信号传输到光接收端。文献[6]对FPGA的数据采集与处理技术进行研究,基于FPGA在数据采样控制和信号处理方面的高性能和单片系统发展的新热点,把FPGA作为整个数据采集与处理系统的控制核心。在文献[7]中,研究者完成了FPGA器件之间以及与其他同类器件性能上的比较,并对分析结果给出了相应的建议。文献[8]、[9]中,研究者提出包括物理层、传输层以及应用层在内的光纤数据传输模型,在此基础上设计光纤传输协议,确定光纤传输帧格式和数据编码规则。CMI编码作为一种容易实现、有恒定的直流分量、频带宽等特点在工程中被广泛应用。笔者所在实验室基于2020北京市大学生科学研究与创业行动计划项目,结合当前与专业相关的问题,开展了基于FPGA的基带传输系统的相关研究。本文在前人不同设计思想的基础上,面向实际应用的需求,将CMI编码用FPGA器件实现,并进行仿真和验证。

1 CMI编解码原理

CMI码全称为Code Mark Inversion,它是一种二电平的不归零1B2B码型(一位二元信息,二位二元码元),与数字双相码类似,其中的二电平分别为“0”和“1”,简称反转码。CMI码在编码时轮流使用正电平“11”和负电平“00”来表示“1”;用固定相位的一个方波“01”来表示“0”。“10”为禁用码组,不会出现三个以上的连码,这种方式使得CMI码码流中可以包含大量的可提取的定时信号,而且易于进行错误检查,也易于实现。在光纤通信中,光源只能发出正的光脉冲,而简单的二电平码信息流中“0”“1”的组合情况会造成起伏,造成判决出现问题,此时CMI码就非常适用。

2 CMI编解码系统设計

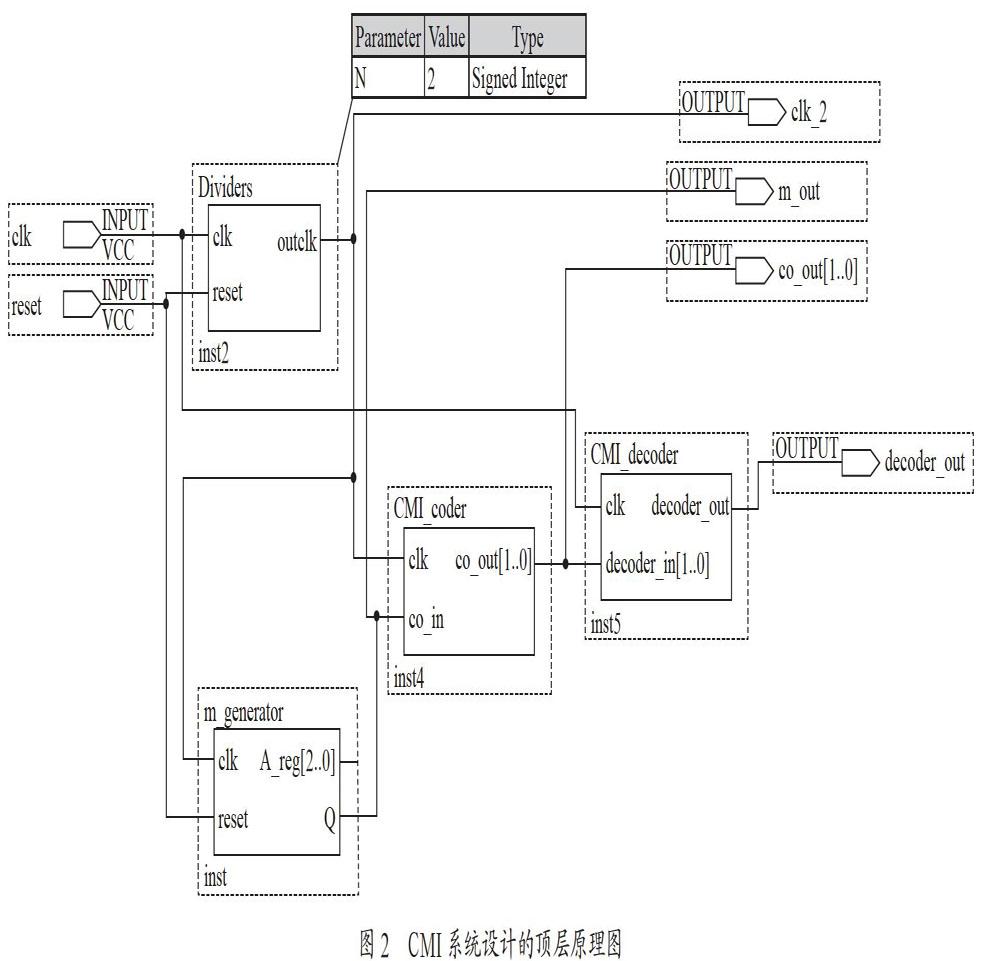

CMI编解码系统设计方框图如图1所示。由图1可见,系统包括分频器、伪随机序列发生器、CMI编码、CMI解码四个模块。

分频器:由于CMI码元速率是基带信号的两倍,所以采用二分频模块来进行分频。该模块输入信号为时钟信号和异步复位信号,复位信号高电平有效,时钟信号上升沿触发,输出信号为分频时钟信号。

伪随机序列发生器:特征多项式使用f(x)=1+x2+x3,生成周期为7的伪随机二值序列。采用线性移位寄存器来产生。电路在适当的时钟信号控制下工作,上升沿触发,其中设置了reset端,reset高电平时电路异步复位。

CMI编码:当输入的码流为‘0码时,输出的码流为“01”,当输入的码流为‘1时,设置一个标志位flag,使得flag<=‘0,输出“11”,然后将标志位置1,即flag<= ‘1,当接下来的码流依旧为‘1时,此时输出为“00”,flag<=‘0。通过标志位的设立,来达到输入为‘1时,输出“00”“11”码流交替出现。输出都是采用二位二进制代码输出。根据CMI编码的原理可知,CMI码元的速率为基带信号的两倍,所以通过对基带信号的二分频方式来使得编码模块和其他模块工作在同一个系统中。

CMI解码:解码电路相对于编码就比较简单一些,因为无须检测变化系数,由于输入是来自上一个模块的编码电路,输入是二位二进制代码,因此不用对输入的码流进行分割。当解码电路的输入为“00”或“11”时,输出为‘1。当输入为“01”时,输出为‘0。

3 系统实现

本系统以Altera公司旗下的Quartus Ⅱ软件作为开发平台,采用的FPGA芯片为Cyclone Ⅱ系列EP2C35F672C6,时钟周期设置为10 kHz。

系統顶层设计原理图如图2所示,其中生成的伪随机序列作为基带信号分别经CMI编码模块和CMI解码模块输出。

3.1 伪随机序列发生器

3.2 CMI编码实现

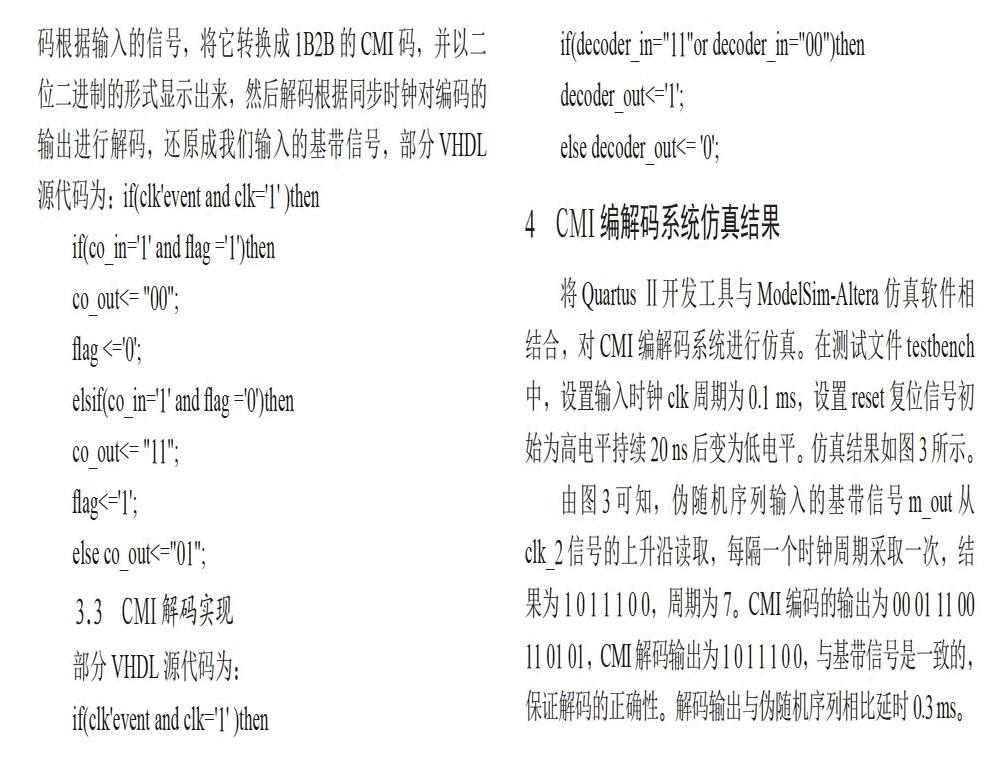

在CMI编解码设计中,输入为伪随机序列发生器,编码根据输入的信号,将它转换成1B2B的CMI码,并以二位二进制的形式显示出来,然后解码根据同步时钟对编码的输出进行解码,还原成我们输入的基带信号,部分VHDL源代码为:if(clk'event and clk='1' )then

4 CMI编解码系统仿真结果

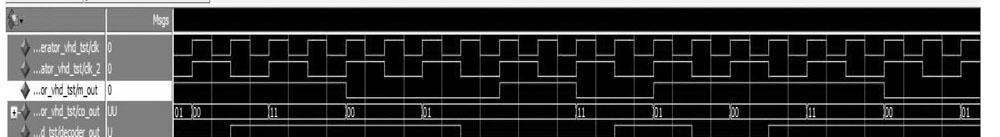

将Quartus Ⅱ开发工具与ModelSim-Altera仿真软件相结合,对CMI编解码系统进行仿真。在测试文件testbench中,设置输入时钟clk周期为0.1 ms,设置reset复位信号初始为高电平持续20 ns后变为低电平。仿真结果如图3所示。

由图3可知,伪随机序列输入的基带信号m_out从clk_2信号的上升沿读取,每隔一个时钟周期采取一次,结果为1 0 1 1 1 0 0,周期为7。CMI编码的输出为00 01 11 00 11 01 01,CMI解码输出为1 0 1 1 1 0 0,与基带信号是一致的,保证解码的正确性。解码输出与伪随机序列相比延时0.3 ms。

5 结 论

本设计基于Altera公司的Quartus Ⅱ软件开发平台和ModelSim-Altera仿真实验平台,使用FPGA器件EP2C35F 672C6芯片,利用VHDL硬件描述语言完成了CMI编解码电路的设计与仿真。本系统是由许多独立的可编程逻辑模块组成,逻辑模块之间通过顶层设计连接,具有逻辑单元灵活、集成度高、适用范围广等优点。在集成电子电路工程上具有一定的应用价值。

参考文献:

[1] 陈适,綦晓华.基于CPLD的CMI编解码电路的设计与实现 [J].武汉理工大学学报(信息与管理工程版),2010,32(1):8-11.

[2] 李莉.基于CPLD/FPGA的CMI编码设计与实现 [J].现代电子技术,2010,33(11):86-87.

[3] 郝晓博.LDPC编译码器的实现 [D].成都:电子科技大学,2019.

[4] 綦晓华.基于FPGA的数字视频监控系统的研究与设计 [D].武汉:武汉理工大学,2009.

[5] 吴成静.模拟信号在光纤中的传输方案研究 [D].西安:西安工业大学,2015.

[6] 孔利东.基于FPGA的数据采集与处理技术的研究 [D].武汉:武汉理工大学,2007.

[7] 包晗.FPGA器件的应用研究 [D].大连:大连海事大学,2006.

[8] 沙启迪.基于FPGA的光纤通信数据传输技术研究 [D].哈尔滨:哈尔滨工业大学,2015.

[9] 李亮.基于FPGA的高速光纤通信数据传输技术的研究与实现 [D].长春:吉林大学,2017.

作者简介:赵晓东(2000—),男,汉族,宁夏石嘴山人,本科在读,研究方向:通信工程;程煜洋(2000—),女,汉族,湖北武汉人,本科在读,研究方向:通信工程;左磊(2000—),男,穿青人,贵州毕节人,本科在读,研究方向:通信工程;方圆(1999—),女,汉族,福建福州人,本科在读,研究方向:通信工程。