不同晶向BiFeO3薄膜的表征及导电性研究*

刘少清

(复旦大学 微电子学院,专用集成电路与系统国家重点实验室,上海 200433)

0 引 言

1921年罗息盐被证明具有铁电性,随后铁电体材料就引起了广泛的关注。到目前为止,被发现的铁电体超过了200种,其中钙钛矿结构铁电体是最为热门的研究对象[1]。从1993年开始,铁电薄膜的制备工艺开始与硅基电路结合,之后,有科学家首次提出了铁电存储器的概念[2-3],这对铁电薄膜的研究起到了关键的推动作用。最近Jiang等人[4]还提出了铁酸铋(BiFeO3,简记为BFO)畴壁导电机制的新型纳米尺寸铁电存储器结构。

BFO是在室温下同时表现出铁电性和铁磁性的材料,居里温度约为1103 K[5],具有良好的电学性能和阻变特性,可以用于制备非挥发铁电阻变存储器。BFO的禁带宽度约为2.67 eV,功函数约4.7 eV[6],目前研究者提出了多种BFO薄膜中的导电机制,包括Fowler-Nordheim(FN)遂穿机制、Poole-Frenkel(PF)发射机制、肖特基(Schottky)发射机制以及空间电荷限制导电机制(space charge limited conduction, 简记为SCLC)等[7-10]。

本文首先对(100)和(110)两种不同晶向的BFO铁电薄膜的质量进行表征,之后测出基于Au/BiFeO3/SrRuO3电容存储结构的BFO薄膜的电流-电压(I-V)特性曲线,再通过拟合的方法对其导电机制进行了深入的研究,并总结出导致不同晶向的BFO薄膜导电性出现差别的原因。本文研究所得到的BFO薄膜特性对高质量纳米

尺度铁电存储器的制备提供支撑,并且能够帮助加深对铁电二极管理论的研究。

1 实 验

1.1 薄膜的制备

1.1.1 制备条件

铁电薄膜的外延生长条件十分严苛,单晶衬底基片的挑选也直接影响到生长的薄膜质量。本文选用的钛酸锶(SrTiO3,简记为STO)基片,其晶格常数为0.3905 nm,与BiFeO3的晶格失配比约为1%。J.Wang等人[14]最早提出了通过脉冲激光沉积(PLD)方法制备的BFO薄膜具备良好的铁电性能。BFO薄膜结晶温度很窄,相结构不稳定、易分解,因此生长要求比其他大部分钙钛矿结构铁电薄膜要高。本文采用KrF(λ=248 nm)分子束激光器作为PLD的激光源,将打到靶材表面的能量密度控制在2 J/cm2左右,生长环境的本底真空为1×10-7Pa。在8 Pa的氧分压、620 ℃的沉积温度条件下,分别在(100)和(110)两种晶向的STO衬底上生长50 nm的钌酸锶(SrRuO3,简记为SRO)作为底电极;之后在10 Pa的氧分压、610 ℃的沉积温度中生长200 nm的BFO,形成(100)和(110)晶向的两组BFO/SRO/STO结构薄膜样品。

1.1.2 薄膜的表征

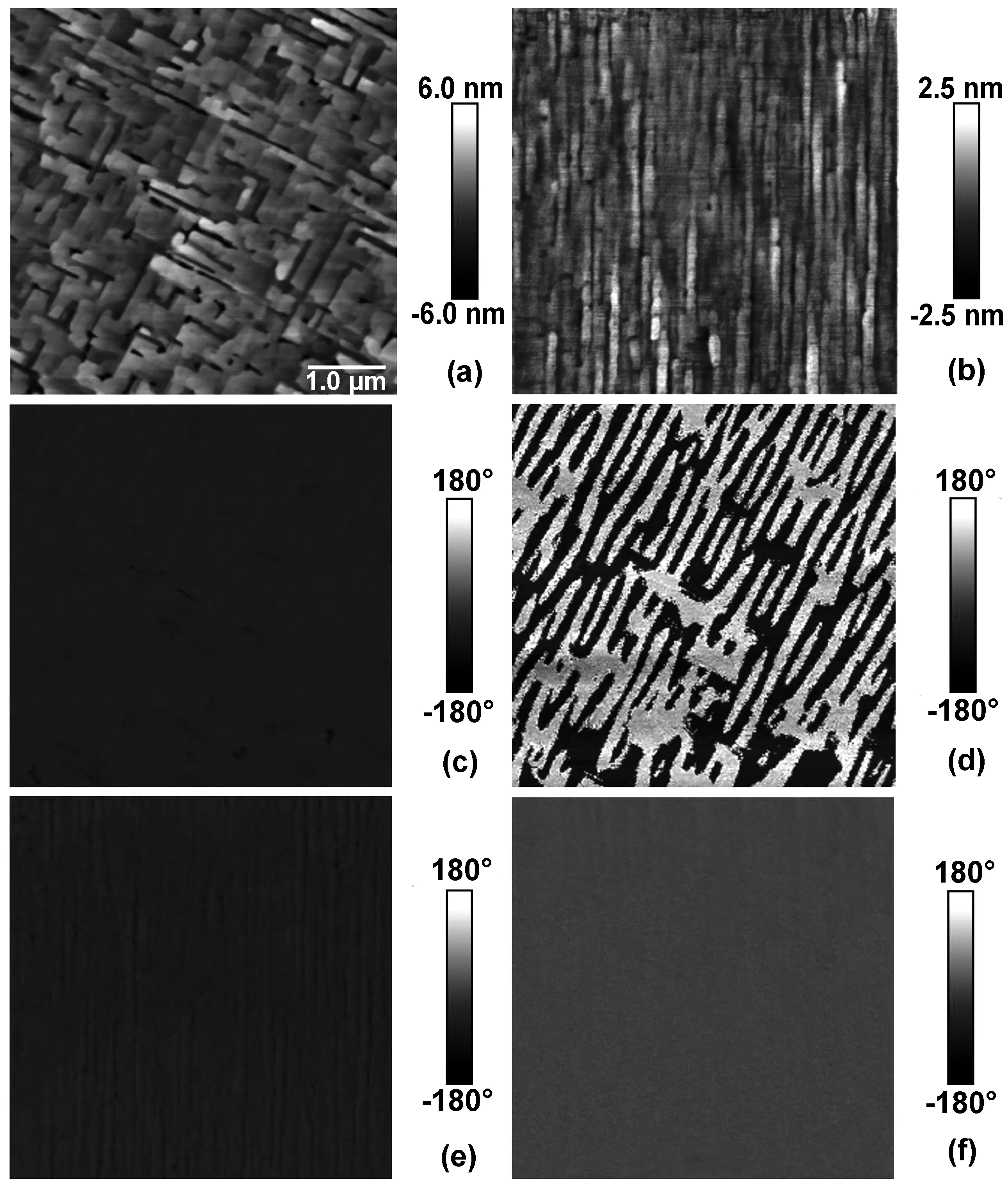

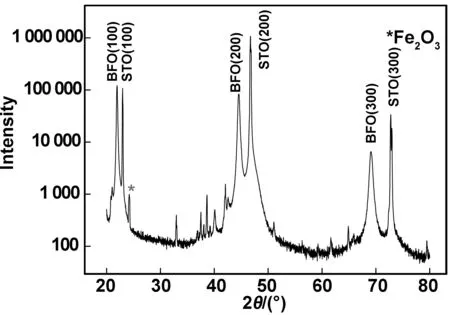

本文中薄膜的表面形貌和电畴结构使用原子力显微镜(AFM,Bruker Icon)和压电力显微镜(PFM,Bruker Icon)进行表征。实验中选用的SRO底电极材料的晶格常数为3.928,与STO衬底晶格匹配的同时也起到了缓冲层作用。图1(a)、(b)分别为(100)和(110)晶向BFO薄膜表面的AFM形貌图。可以看出(110)晶向的BFO薄膜表面更平整、致密,但是在BFO(100)薄膜表面则出现了沟壑状结构。结合图2的XRD衍射图谱,可以看出BFO薄膜尽管在(100)晶向上衍射峰峰值很高,但仍然出现了由Bi3+挥发形成的Fe2O3组分的衍射峰。

图1 BFO薄膜的表面形貌和电畴结构(a)BFO(100)表面形貌(b)BFO(110)表面形貌(c)、(d)BFO(100)面外、面内电畴结构(e)、(f)BFO(110)面外、面内电畴结构

铁电薄膜的表征除了形貌,更重要的是其内部电畴结构。图1(c)、(d)展示了BFO(100)薄膜的面外单畴结构,以及在面内形成的规则条纹状周期性畴结构;图1(e)、(f)则表明BFO(110)薄膜整体的电畴方向一致,形成完美地单畴结构。证明本文中BFO薄膜样品的电畴并非是杂乱的自由取向,而是受生长机制的影响,最终表现为择优取向[15]。

图2 BFO(100)薄膜的XRD衍射图谱

1.2 性能测试

为表征BFO铁电薄膜的宏观铁电性能和电流导电机制,本实验利用三靶等离子溅射仪,通过铜网掩膜,在样品上生长面积为100 μm×100 μm的Au上电极,构成图3所示Au/BFO/SRO结构的金属-铁电体-金属(MFM)面外电容器。PFM的表征结果显示薄膜自发极化的择优取向为指向薄膜内部,因此规定在SRO底电极上施加正向电压时产生正向极化,电流由SRO流向Au电极为正向导通。

图3 Au/BFO/SRO的MFM结构

图4为BFO(100)和BFO(110)的电滞回线。BFO薄膜中的晶胞因为受STO基片外延压缩应力调制,使得薄膜的自发极化在z轴方向上的分量增强[16],两个样品的剩余极化强度在Vmax=12 V时达到约60 μC/cm2。为了进一步研究BFO铁电薄膜的电流导电机制,本文采用安捷伦公司的半导体分析仪(Agilent, B1500)对样品进行I-V曲线测试,如图5所示,电压范围-9~9 V。测试结果表明BFO薄膜具有一定的单向导通性,并且可以发现BFO(110)薄膜的电流更小、导电性能更弱,并且负向电流更是比(100)晶向的BFO薄膜低了将近一个量级。

图4 P-V电滞回线

2 结果与讨论

2.1 导电机制

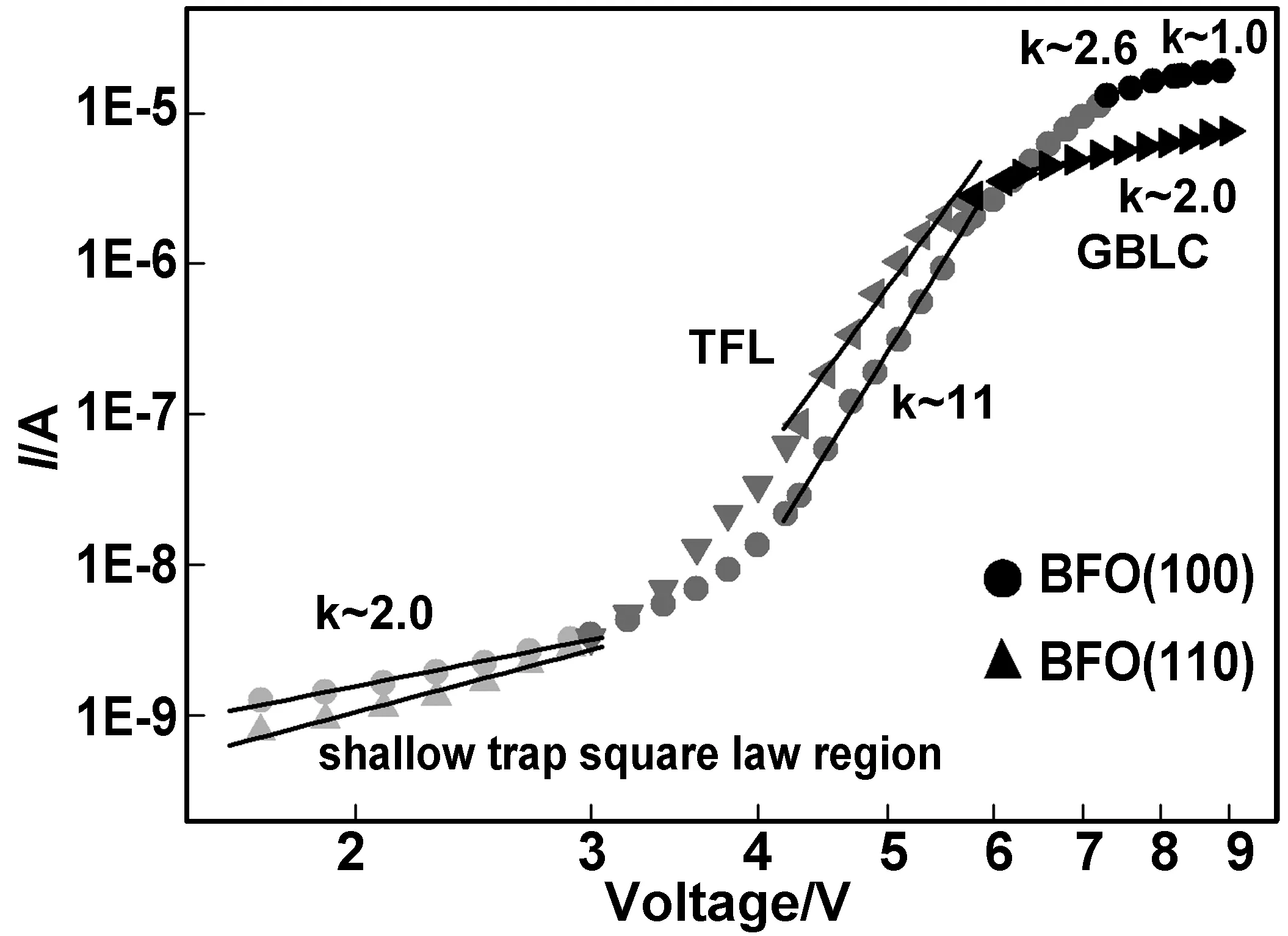

BFO薄膜的导电机理和N型半导体类似,是基于氧空位和表面缺陷等陷阱所产生的电子参与导电[17],其导电机制有FN遂穿、PF发射、肖特基发射以及空间电荷限制导电(SCLC)等。本文采用线性拟合的方法,确认所测样品局部电流主要的导电机制为SCLC,对应的lgI-lgV拟合曲线如图6、7。

图5 BFO(100)和BFO(110)的I-V曲线

理想的SCLC机制包含以下几个部分[18]:当电场强度很弱时,薄膜的注入载流子浓度非常小,此时膜内的自由载流子起主要作用,图6显示在低于2 V时,BFO(100)和BFO(110)两个样品的拟合曲线斜率约为1,此时为欧姆导电机制,不过BFO的自由载流子密度很低,所以该过程持续时间很短。

图6 低电场下的欧姆导电机制

随着电压上升,注入载流子的浓度逐渐增加,开始填充薄膜内的陷阱能级。第二部分为注入载流子填充低能级陷阱的过程,被称为浅能级陷阱的填充区(shallow trap square law region),如图7的第一段曲线,此时lgI-lgV斜率约为2;第三部分是陷阱能级填充限制区(trap filled limit,简记为TFL),lgI-lgV拟合曲线呈现出很大的斜率,电流以指数方式快速上升,如图7的中间段曲线;当注入载流子填充陷阱能级结束,根据SCLC导电机制,这时电流将符合以下方程19]

其中μ为电荷迁移率,εr为相对介电常数,ε0为真空介电常数,d为薄膜厚度,S为电极面积,E为电场强度,但真实的薄膜样品由于受到晶界限制导电(grain boundary limited conduction,简记为GBLC)的影响,lgI与lgV之间的线性关系比例应修正为大于2的非线性系数α[20],即:

I=K·Vα

其中K为常量。图7最后一段即为此时的拟合曲线,可以看出BFO(100)薄膜样品由于Fe2O3杂相的存在导致单晶薄膜的结晶度降低,在高电场下明显受到GBLC机制影响,其拟合曲线在该阶段斜率为2.6,超过了理想SCLC机制的上升速率;而结晶度足够高的单晶薄膜几乎不会受GBLC影响[18],BFO(110)拟合曲线的斜率仍然为2。

除此之外,BFO(100)的拟合曲线在8.3~9.0 V部分还出现Morrison 等[17]提到的斜率约为1的准欧姆区(quasi-Ohmic region),其同样由GBLC机制产生[16]。施加负向电压时,SCLC仍然为主导机制,是陷阱能级由满状态逐步释放电子的过程。

图7 高电场区域内的SCLC导电机制

2.2 导电性不同的原因

通过对BFO薄膜导电机制的研究,下面对两种晶向的BFO薄膜导电性存在差异的原因进行分析。本文中(100)和(110)晶向的两个BFO薄膜样品自发极化均由表面指向薄膜内部,因此在退极化场的作用下,薄膜表面由缺陷和氧空位产生的电子会流向底电极,而其自身则因为失去电子表现为带正电的离化状态,形成陷阱。由AFM的表征以及XRD图谱可以看出,生长在(110)晶向STO衬底上的BFO薄膜表面致密,粗糙度更小;而生长在(100)晶向STO衬底上的BFO由于Bi3+挥发形成了沟壑状形貌和Fe2O3杂相,引入了更多缺陷,因此其表面陷阱密度更大。

当逐渐增大正向电压,在注入载流子不断填充陷阱能级的TFL机制主导的时间里,电流呈指数上升趋势,而陷阱密度越大,载流子填充的持续时间越久,从图7中也可以看出,BFO(100)薄膜填充陷阱能级的过程更长,当载流子完全填充陷阱能级后,其电流达到11.2 μA,相对地,BFO(110)薄膜在该阶段完成时电流仅增长到3.7 μA;随后在高电场区,受GBLC机制的影响,BFO(100)薄膜的电流增长速度更快,最终经过准欧姆区,电流达到了19.2 μA。同理,当施加负向电压,电流的变化也是由于SCLC机制主导的将陷阱能级内电子逐步释放,BFO(100)样品负向的漏电流在-9 V时约为5 μA,超过BFO(110)样品将近10倍。

而电畴的择优取向产生的自发极化电场虽然能够改变内部能带结构,使BFO薄膜样品在I-V曲线上表现出一定的单边导通特征,但是由于主要的导电机制为空间电荷限制导电,即陷阱能级内电子的填充与释放,因此正向电流大的同时,负向漏电流也会增加,最终维持在同一量级。

3 结 论

本文利用PLD技术,在同样的条件下异质外延生长BFO/SRO/STO(100)和BFO/SRO/STO(110)两组铁电薄膜样品。对比其AFM、PFM的表征结果,再结合XRD衍射图谱以及电滞回线,可以看出BFO(110)样品拥有更加致密的表面和更少的缺陷。后续的I-V拟合曲线证明BFO(100)和BFO(110)薄膜主要的导电机制为SCLC。再经过深入分析,证明(100)晶向的BFO薄膜由于其表面和内部缺陷密度更大、结晶度相对更低,致使载流子填充陷阱能级的过程更长。即电流指数增长的持续时间更久,并且在高电场区域更是受GBLC机制影响,电流上升曲线脱离了理想SCLC机制,最终表现出更强的导电性能。