重离子治癌装置中γ-γ 符合时间测量系统设计

颜俊伟,柯凌云,陈金达,张秀玲,杜成名,杨海波,王长鑫,3,吴俊达,苏 弘,千 奕,佘乾顺,赵红赟,蒲天磊,孔 洁*

(1. 中国科学院近代物理研究所 兰州 730000;2. 中国科学院大学核科学与技术学院 北京 石景山区 100049;3. 华南师范大学物理与电信工程学院 广州 510631)

重离子束治癌是生物医学与核技术深度交叉和融合的产物。由于重离子具有倒转的深度剂量分布曲线(Bragg 曲线)和较高的相对生物效应,重离子束治癌技术可以克服常规放射疗法的局限性[1-2]。在重离子治癌装置[3-5]中,12C 束流轰击靶组织(肿瘤)会引发弹核碎裂产生β+发射体(11C、15O、10C),因此在径迹末端遇负电子会产生湮灭反应,同时释放两个在同一直线上沿相反方向发射的511 keV γ光子。在患者受辐射后立即对该反应空间进行测量,可以测得有效的照射剂量信息[6]。重离子治癌装置要求采用符合探测技术进行γ-γ 符合测量,能够从不同探测器的输出脉冲中挑选相关的时间脉冲,进而确认关联事件,甄别排除无效事件,提高探测器的探测效率。符合测量系统通过一对相对放置的探测器测量两个511 keV γ 光子击中探测器的时间信息和能量信息,并基于时间窗和能量窗的判选,进而获取符合事件和精确推断出湮灭位置[7]。能量符合的目的是为了消除正电子发射断层扫描成像(positron emission tomography, PET)系统中由康普顿散射造成的散射符合事件,时间符合的目的为了消除系统中的随机符合事件。因此,设计用于重离子治癌装置的符合测量系统必须满足高分辨率和高精度时间测量。

时间量在核物理与粒子物理实验中具有重要意义,时间-数字转换(time digital conversion, TDC)是时间间隔测量的基本方法之一[8-9],广泛应用于现代物理测量系统,可采用模拟方法、数字方法以及专用的集成电路实现[10]。采用专用集成电路(ASIC)获取高分辨率时间间隔测量,如GP2、HPTDC 等专用TDC ASIC 芯片[11],虽然简化了设计复杂度,但是其开发周期长、通用性差。采用现场可编程逻辑阵列(FPGA)技术,由于其编程灵活性强、精度高、可靠性高、通道多特性,同时拥有丰富的延迟链单元、时钟、触发器等资源,使其成为实现数字TDC 的主要手段[12]。

传统的符合测量电路通常采用NIM(nuclear instrument module)机箱、线性放大插件、符合插件等,存在着设计复杂,抗干扰性、测量再现、易操作性和系统升级等方面的不足,探索开发新型的符合测量系统迫在眉睫[13]。本文设计基于Altera 公司Cyclone Ⅴ系列FPGA 实现重离子治癌装置中γγ 符合时间测量系统,实现高分辨率及高精度的时间间隔测量,本征时间测量精度达百皮秒量级,符合时间谱分辨达1.5 ns (FWHM)。

1 符合时间测量系统结构

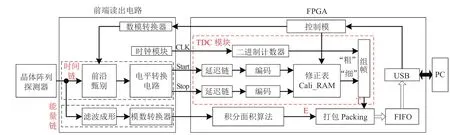

研制的γ-γ 符合时间测量系统结构如图1 所示,包括晶体阵列探测器、前端读出电路和FPGA电路和PC。前端读出电路包括时间链、能量链、数模转换器(DAC)和时钟模块组成,其中时间链负责处理晶体阵列探测器打拿极输出的时间信号,产生定时脉冲信号;能量链完成电荷信号的滤波成形和模数转换;时钟模块提供FPGA 所需的系统时钟。FPGA 设计实现了控制模块、TDC 模块、积分面积算法模块、数据打包模块及通信模块(USB),其中控制模块用于配置修正表(Cali_RAM)及控制DAC 的阈值电平。TDC 模块标记信号的时间戳信息,即通过记录每个击中信号发生的时刻,利用修正表对记录的时间信息进行修正,得到精确的“细”时间,由组帧模块将“细”时间与“粗”时间测量结果合成时间戳。组帧模块根据帧格式将时间戳(T)与能量(E)数据打包暂存于先进先出缓冲器(FIFO)中,而后通过USB[14]进行数据传输和配置。在PC 上利用MATLAB 编写分析代码读取上传的数据包,顺序提取各个通道的时间和能量信息,基于设置的时间窗筛选符合的事件同时做差处理,得到时间谱。

该系统电路结构简单,具有较强的灵活性和可扩展性,易于系统升级。

图1 γ-γ 符合时间测量系统结构框图

2 符合时间电路设计与实现

图2 符合时间电路时间链和FPGA-TDC 模块

符合时间电路中时间链和FPGA-TDC 逻辑框图如图2 所示。光电倍增管打拿极输出信号为固定的脉冲波形,其宽度、幅度、周期及边沿特性一致性好,适合选用前沿定时甄别。其中时间链采用LEMO 接头,阻抗50 Ω,交流耦合至由超高速比较器构成的定时甄别电路,同向端是DAC 产生的阈值电平输入,经甄别给出触发信号(start/stop)。由于比较器是PECL 电平标准输出,选用的FPGA的IO 端口为LVDS 电平标准,故电路采用Micrel公司的高速电平转换芯片SY55855 将PECL 转为LVDS 电平送给FPGA,提高信号的抗干扰性。FPGA-TDC 设计采用“粗细”时间测量相结合的方法实现。“粗”时间测量采用计数器型TDC构建,分辨率为系统时钟f2 的周期,实际工作中为了消除亚稳态现象,计数器系统时钟f2 与f1 有180°的相位差。“细”时间测量单元分为3 个部分:缓冲器和寄存器阵列构成的级联延迟链、编码逻辑和Cali_RAM 修正模块。在触发电平信号通道中插入一条延迟链,信号在延迟链上传播,在其到来后的第一个时钟上升沿进行锁存寄存器阵列上的电平信号,将输出的多bit 电平称为温度码。在编码逻辑中对温度码进行二进制编码,输出“细”时间结果。考虑到由于器件工艺、布局布线、温度以及硬件电路等因素影响,延迟链单元存在非线性,每个单元延迟时间不一致,从而降低“细”时间测量精度。故在本设计中,通过将修正查找表载入Cali_RAM 来修正非线性以提高测量精度,得到最后的“细”时间,最终输出“细”和“粗”的时间测量结果,并将时间测量数据按数据帧格式打包暂存于先进先出缓冲器FIFO 中;之后通过USB 数据通信模块将数据传输至PC 机完成后续的处理。

2.1 “粗细”时间测量

图4 粗时间测量和细时间测量逻辑框图

2.2 Cali_RAM 修正表实现

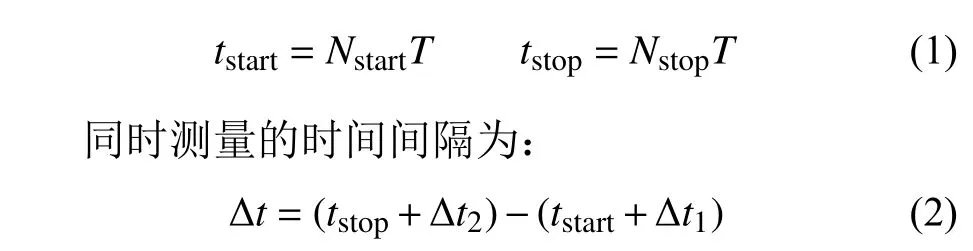

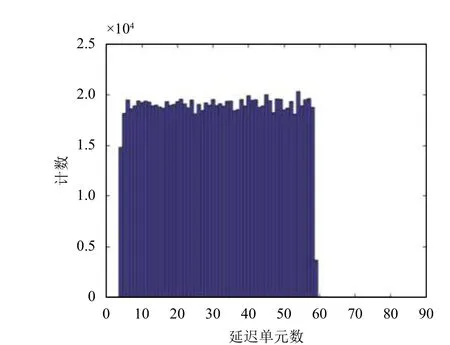

为减少非线性的影响,本文设计Cali_RAM 存储码密度查找表进行“细”时间码的修正。实验中start 或stop 的频率与系统时钟频率呈弱相关,累计大量数据,将有输出的延迟单元个数作统计分布图,即码密度图,如图5 所示。

图5 码密度示意图

在呈弱相关且大量数据前提下,认为信号的前沿到来时刻均匀分布在一个时钟周期内部,故有输出的延迟单元的个数的统计差异性取决于自身的延迟时间大小,单元的延时计算为:

把有效输出的延迟单元对应的总延迟时间计算出来后,将其转化为二进制并写入到Cali_RAM中。正常工作状态下得到未修正的“细”计数编码值作为Cali_RAM 的地址查找到对应的真实延时值,即可完成时间测量的修正。

2.3 FPGA-TDC 的布局布线

符合时间测量系统采用Altera 高性能Cyclone V 系列。底层架构由4 输入查找表(LUTs)构成的自适应逻辑模块(ALM)、存储器模块以及乘法器组成。图6a 为实现延迟链底层布线图,每一级均由ALM 左端的输入引脚到右端的寄存器输出。图6b 为10 个ALM 组成的1 个LAB 单元。ALM是Cyclone V 中最小的逻辑单元,每一个ALM 中包括6 个LUT,4 个可编程寄存器。

图6 延迟链底层布局布线

3 性能测试与讨论

3.1 TDC 的本征时间分辨

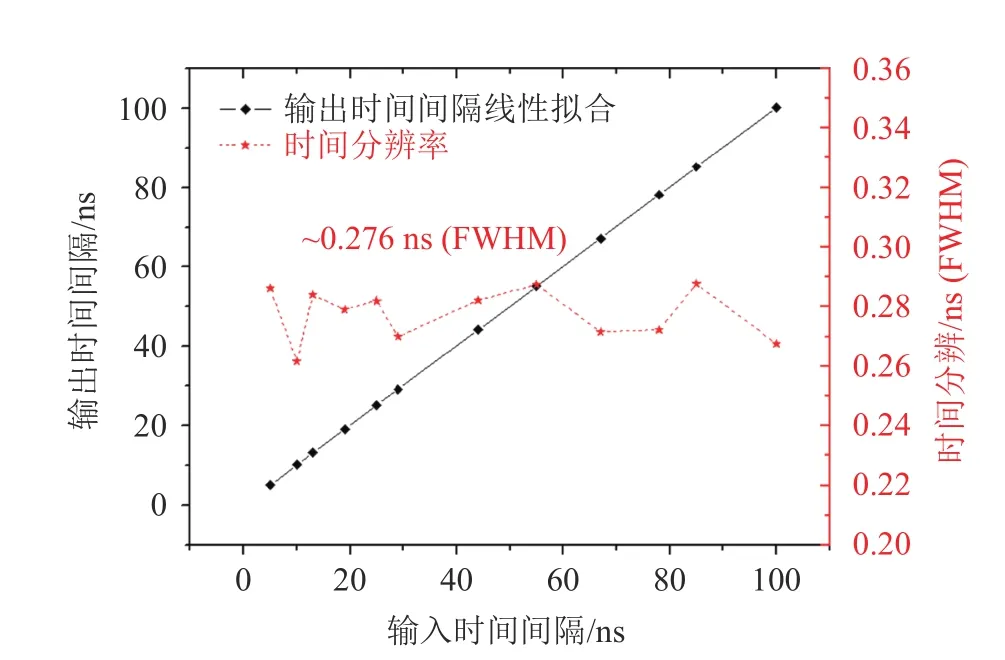

通过基于电缆延迟方法的延迟时间测量来研究定时测量的精度[15]。电缆延迟方法旨在消除信号发生器本身的时间抖动:输入大量延迟时间固定的成对快脉冲信号作为触发信号,测量其时间间隔,将测试得到的数据进行统计分析,得到固有时间分辨。利用Tektronix AFG3252 双通道信号发生器模拟探测器输出信号,在同样的输出脉冲频率和恒定的室温下,采用不同长度的同轴电缆,选择固定延迟时间为10 ns 进行时间间隔的测量,经过统计分析使用高斯拟合[16]方法得到FPGA-TDC 的时间分辨。固定的线缆延迟时间下测得时间分布,分辨为255 ps(FWHM),如图7 所示。输入不同延迟时间测得FPGA-TDC 的线性及分辨好于276 ps (FWHM),如图8 所示。

图7 固定延迟时间的分布图

图8 不同延迟间的线性拟合及均方根值

3.2 联合测试性能

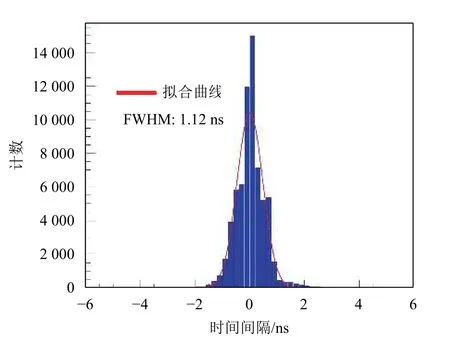

γ-γ 符合时间测量系统联合测试实验装置如图9 所示。每个探头采用H8500 耦合LYSO 晶体阵列组成,LYSO 阵列用白色的特氟龙胶带和黑色胶带避光包裹起来,并连接到H8500C 光电倍增管上。在每个光电倍增管之后,采用DPC 桥式电路通过LEMO 电缆连接到符合时间测量系统板上[17-18]。 USB 电缆将数据传送到PC 进行后期数据分析处理。其中的探测器晶体阵列采用由22×22个2 mm×2 mm×15 mm LYSO 晶体条组成,在950 V的正高压偏置下,H8500 的增益高达106。光电倍增管打拿极输出信号作为时间信号,用于符合测量。测得有效符合事件时间分布,系统时间测量精度优于1.12 ns (FWHM),如图10 所示。统计分析有效符合事件得到的LYSO 晶体阵列位置映射散点图清晰,如图11 所示。

图9 γ-γ 符合时间测量系统装置图

图10 符合时间间隔的时间谱

图11 LYSO 阵列晶体位置映射图

4 结 束 语

本文设计并实现了一种用于重离子治癌装置的γ-γ 符合时间测量系统,该系统具有结构简单、易实现、低成本的特点,可方便实现通道数的扩展,且各个通道间独立。经过试验测试,本征时间分辨好于276 ps (FWHM),具有良好线性。LYSO 晶体阵列构成的符合测量系统对511 keV γ 射线的测试,时间测量精度优于1.12 ns (FWHM),略好于文献[19]提出的多相时钟测得符合时间精度。而且晶体阵列位置映射散点图清晰,能够满足γ-γ 符合时间测量系统的研究和测试需求。