基于标准单元替换的功耗优化方法研究*

贾 勤,马驰远,彭书涛

(国防科技大学计算机学院,湖南 长沙 410073)

1 引言

近年来,集成电路行业的迅速发展和设计规模的不断增大,使芯片总功耗大幅提升,功耗的提升可能导致芯片运行时温度急剧上升,最终可能影响芯片正常工作。因此,如何有效地降低功耗成为了集成电路设计流程中一个急需解决的问题[1]。

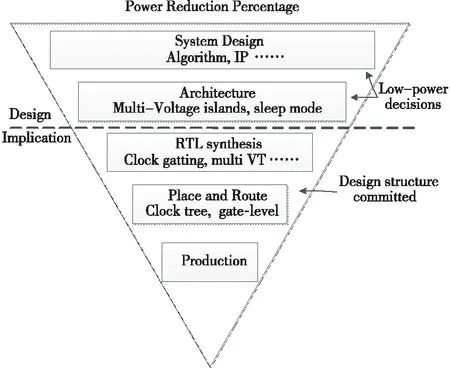

在集成电路设计的整个流程中,每个阶段都可以有针对性地进行功耗优化,然而在设计流程的不同阶段对功耗优化的收益是不同的。在相同工艺实现的前提下,在设计流程中越早介入功耗优化获得的收益越大。如图1所示,在系统设计阶段和体系结构规划阶段进行功耗优化,都可以得到比较可观的收益。反之,在设计完成后的生产阶段,功耗优化收益则极其有限。

Figure 1 Benefits of power consumption optimization at various stages

在芯片的设计阶段,针对系统设计,可以通过优化算法来达到降低功耗的目的;针对体系结构,可以使用多电压域和增加睡眠模式等具体手段来有针对性地对某部分部件进行功耗优化[3]。在芯片实现阶段,针对代码综合,可在过程中加入时钟门控和多阈值VT(Voltage Threshold)单元来降低功耗;针对布局布线,可以通过优化时钟树、控制线长和单元VT比例对设计的功耗进行优化[4]。

Figure 2 Power consumption calculation method of design tool

在现今较先进的工艺下,标准单元的功耗与时序是矛盾的[5]。因此,在优化功耗的同时如何兼顾时序,成为功耗优化过程中的关键问题[6]。本文重点关注物理设计阶段的功耗优化方法,采用先进工艺,在一个完成布局布线的高频模块上,通过2种不同的标准单元替换方法达到降低模块功耗的目的,并从多个方面比较了2种方法的优劣。

2 背景

2.1 功耗的计算

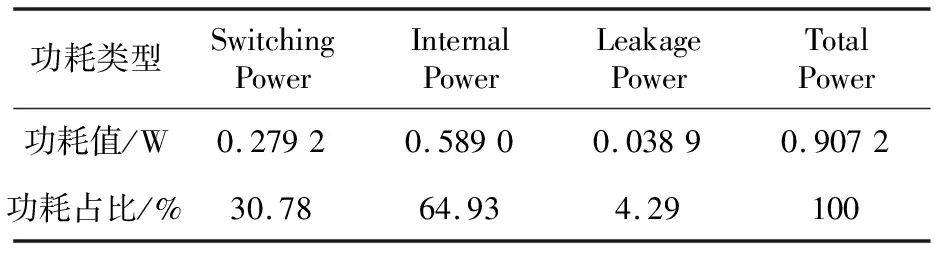

图2所示为设计工具计算功耗的方法,一个单元的总功耗(Total Power)由3部分组成:开关功耗(Switching Power)、内部功耗(Internal Power)和泄漏功耗(Leakage Power)。其中开关功耗的大小与翻转率和单元连线的寄生参数有关[7]。而内部功耗和泄漏功耗则是由工具从标准单元库中获得[8]。一般的标准单元库中,单元的内部功耗值是一个7×7的表格,同一标准单元在不同的输入跳变延时(Transition)和输出负载(Load)情况下,从标准单元库中获得的内部功耗值不同。而通常情况下,同一标准单元处于同一模式下时,从标准单元库中获取的泄漏功耗值则是相同的[9]。

通过上述单元功耗组成可以看出,在模块布局布线完成之后,如需要优化功耗,则只能通过替换单元来实现,由于决定开关功耗的线的寄生参数和翻转率能改变的可能性极小,因此此阶段只能改变单元的内部功耗和泄漏功耗。不同的单元类型在标准单元库中的内部功耗和泄漏功耗的值是不一样的,可以选择功耗较小的单元替换设计中同等逻辑功能功耗较大的单元,从而达到优化功耗的目的[10]。

2.2 时序与功耗

时序与功耗关系的普遍规律是,在驱动足够的情况下,一个单元的功耗越小,其在同等情况下的单元延时越大,反之,则单元延时越小。在高性能集成电路的实现过程中,时序是最关键的因素之一,但是在性能提升的同时,功耗也随之增大[11]。

单元的功耗、延时和驱动力大小与VT类型有关,不同类型的VT单元对应着不同的阈值电压。在先进工艺下,提供了3种不同阈值的单元,分别是标准阈值SVT(Standard VT)、低阈值LVT(Low VT)和超低阈值ULVT(Ultra Low VT)。同时还提供了不同驱动力的单元。相同的逻辑功能的单元可以被替换成不同驱动力和不同VT类型的单元。

图3~图5所示为先进工艺下普通缓冲器(Buffer)的单元延时、内部功耗和泄漏功耗的柱状图。图中的数据采用了同类型单元并给定任意输入Transition,多次一驱四后单元的延时会达到一个恒定的值,此时单元的内部功耗和泄漏功耗也变成了一个固定值,图中的这3类值都是取的该情况下的数值。从图3中可以看出,在这种计算方式下,驱动在D0~D4时,单元延时是逐渐减小的,但从D5开始单元延时没有明显的下降趋势。

Figure 3 Cell delay of ordinary Buffer

Figure 4 Internal power of ordinary Buffer

Figure 5 Leakage power of ordinary Buffer

从图4中可以看出,单元内部功耗的变化规律遵循如下特点:相同驱动情况下,不同VT单元之间内部功耗的变化不明显,但当驱动力变化时,内部功耗的变化较为明显。

从图5中可以看出,单元的泄漏功耗在驱动变化和VT变化时都很明显,但VT变化时,泄漏功耗的变化比例比驱动变化的比例更大,且呈现出阶跃式变化。

在高性能集成电路的实现中,多工作模式多工艺角下的时序是重点,在进行功耗优化时,也需要兼顾单元替换后在每个工作模式(Mode)和工艺角(Corner)下的时序,以最大限度地减少时序闭合的工作量。图6是普通Buffer的单元延时在典型Corner和慢速Corner下的比例。从图6中可以看出,若将一个Buffer单元从ULVT换成SVT,其单元延时的Corner之间比例从1.23左右变成了1.55左右。而不同驱动大小Buffer的单元延时在 Corner之间的比例波动不明显。因此,在替换单元时,只改变驱动能力能更好地保持原有Corner之间的一致性。

Figure 6 Ratio of ordinary Buffer cell delay under SS Corner and TT Corner

3 标准单元替换策略

在完成布局布线后,模块级通常需少量手工设计修改工作,以修复时序、电压降(IR drop)和设计规则检查DRC(Design Rule Check)过程中发现的违反设计要求的情况。在这个阶段,会通过替换单元的方式进行1~2轮功耗优化。具体做法是,将时序不关键的数据路径上的单元替换成功耗较低的单元,从而达到降低模块整体功耗的效果。

本文研究基于先进工艺下的一个高频互连模块,典型Corner下主频2.5 GHz,模块内不包含硬宏,全部由标准单元组成。面积为3 505.408 um× 300.0 um,总的逻辑单元数量为773 325。

由于该模块在功能模式下有多个时序Corner需要检查,其中1/3为Setup Corner,2/3为Hold Corner。为方便统计和比较分析,在功耗优化前后,取时序较为关键的2个Corner:典型的一个Setup Corner和慢速的一个Setup Corner的最大违反量和违反条数为表征来衡量功耗优化对时序的影响程度。下文中的各类功耗数据都是基于上述Corner,并使用同一版本时序检查工具得出的结果。

基础数据的功耗信息如表1所示,模块的初始总功耗为0.907 2 W,其中开关功耗为0.297 2 W,内部功耗为0.589 0W,泄漏功耗为0.038 9 W,可以看出,内部功耗占比较大为64.93%。SVT、LVT和ULVT单元数量分别为439 509,84 934和248 882,SVT、LVT和ULVT单元数量和占比情况如表2所示,分别占56.83%,10.98%和32.18%。时序结果如表3所示,典型Corner下有49条违反路径,最大违反为-0.009 ns;而慢速Corner下时序是干净的状态。

Table 1 Power data of based data block

Table 2 Number and ratio of standard cell class of based data block

Table 3 Timing violations of based data block in 2 Corners

以下基于上述模块进行2组功耗优化实验,实验具体过程如下所示:

实验1在基础数据的基础上,以替换单元VT的方式对不满足Setup 检查的数据路径上的单元进行替换。

在工程实践中,设计工具对替换单元的VT情况下的时序预估比较准确,因此,在这个实验中,工具设置Setup 余量为0.005 ns,能确保工具预估的时序与实际替换单元之后的实际时序相差较小。

从表4中可以看出,模块的总功耗下降了21.1 mW,其中,开关功耗下降了0.5 mW,内部功耗下降了6.2 mW,泄漏功耗下降最多,达到14.3 mW,占基础数据泄漏功耗的36.8%。表5所示为模块完成功耗优化后,SVT、LVT和ULVT单元的占比情况分别为69.75%,15.96%和14.29%,可以看出,ULVT单元数量比例下降较为明显。实验1中,共有182 990个标准单元被替换,占模块中总单元数的23.66%。而其对时序的破坏程度如表6所示,典型Corner下,功耗优化后模块的时序违反情况是55条,且最差-0.008 ns,慢速Corner下时序违反情况是373条,且最差-0.023 ns,该结果在工程上是可以接受的。

Table 4 Power data of block in experiment 1

Table 5 Number and ratio of standard cell class of block in experiment 1

Table 6 Timing violations of block in 2 Corners in experiment 1

为分析其功耗的具体来源,本文研究了实验1中替换的182 990个单元中每个单元的功耗变化情况,按照总功耗下降量从大到小排序后,将排在1001~1500的500个单元作为样本分析每个单元的总功耗下降量的具体来源。如图7所示,500个单元的总功耗下降量差不多处于同一水平,从总功耗下降量的组成可以看出,绝大部分下降量来自单元泄漏功耗的下降,只有少数单元的内部功耗占比明显,而大部分单元的开关功耗下降量几乎为零。

Figure 7 Distribution of power consumption decreasement of 500 cells in experiment 1

由于对功耗优化的需求比较大,在完成布局布线后的设计修改阶段需要回收更多的功耗,因此进行了如下实验:

实验2不限定设计工具替换单元的方式,使其在保证时序的情况下,尽可能多地降低功耗,但是由于在单元驱动大小变化的情况下,工具对时序的预估准确度会大大降低,因此,经过反复实验后,给工具设置的Setup余量增大到0.015 ns,使其在功耗优化的同时减少对时序的影响。

从表7中可以看出,总功耗下降了24.6 mW,其中开关功耗下降3.1 mW,内部功耗下降12.2 mW,泄漏功耗下降9.1 mW,可以看到内部功耗的下降幅度比实验1的内部功耗下降幅度大,而泄漏功耗的下降幅度比实验1的泄漏功耗下降幅度小,总功耗下降幅度比实验1的总功耗下降幅度略大。如表8所示,模块中SVT、LVT和ULVT单元的占比变成了58.48%,12.78%和27.78%,其UVLT比例也有所下降,但没有实验1中的ULVT比例下降大,且实验2中一共替换了286 707个单元,占到单元总数的37.07%。如表9所示,实验2的功耗优化对时序的影响也在可接受的范围内,典型Corner下违反21条,且最大违反为-0.031 ns;慢速Corner下违反109条,且最大违反为-0.094 ns,违反条数比实验1的违反条数少,但最大违反量比实验1的最大违反值大。

Table 7 Power data of block in experiment 2

Table 8 Number and ratio of standard cell class of block in experiment 2

Table 9 Timing violations of block in 2 Corners in experiment 2

和实验1相同,取总功耗下降量排在1001~1500的500个单元为样本,分析其总功耗的下降量的具体来源。从图8中可以看出,这500个单元大部分的总功耗下降量来自内部功耗。由此可见,减小单元驱动的功耗优化方式能获得更多的内部功耗下降收益。

Figure 8 Distribution of power decreasement of 500 cells in in experiment 2

图9为单元总功耗下降量的每个数量级中的单元数量分布。实验1中单元总功耗的下降量分布相对集中在1.0E-8~1.0E-6。而实验2中单元总功耗的下降量分布没有实验1中分布那么集中,1.0E-9及以下数量级的下降量也有不少。

Figure 9 Distribution of power consumption decreasement magnitude in 2 experiments

这种现象的出现是因为实验1中,单元只替换了VT,从对不同VT的Buffer泄漏功耗的变化图(如图5所示)中可以看出,改变单元VT时,泄漏功耗呈阶跃式变化,而内部功耗变化不明显,呈现出来的总功耗变化量会集中分布在某一区间内。实验2中的单元大部分替换了驱动,而改变单元驱动时,泄漏功耗和内部功耗的变化都是比较连续的,因此总功耗的变化量就会分散在各个数量级。

2个实验替换的单元个数相差非常大,但总功耗下降的量差不多,对时序造成的影响也不相同。实验1由于只替换单元的VT,因此功耗下降大部分来自泄漏功耗,而内部功耗的下降量占比较小。由于不同VT单元Corner间的单元延时比例差异较大,导致功耗优化后Corner间时序差异较大。实验2主要进行单元驱动的替换,只要时序满足,且逻辑等价,工具就会对其进行最大限度的优化,因此其总功耗的下降量主要来源于内部功耗。且由于不同驱动单元Corner间的单元延时比例差不多,因此在保持Corner间时序一致性方面,实验2的方式比实验1的略好。

2种实验方法在工程实践中都是可取的,在完成布局布线后的设计修改阶段,功耗优化时如果侧重优化单元的泄漏功耗,则可以采取替换VT的方式;如果侧重优化单元的内部功耗,则可以采用替换驱动的方式。

4 结束语

本文将2种不同的标准单元替换策略运用到先进工艺下的高频互连模块,研究比较了2种策略的功耗优化效果。研究结果表明,只替换VT的优化方法对泄漏功耗的优化效果较好,而替换驱动的优化方法对内部功耗的优化效果较好,二者对时序的影响差别不大。该研究结论对物理设计中的设计修改具有指导意义,能够在保证性能的前提下最大限度地降低模块功耗,为先进工艺节点下高频模块的功耗优化工作提供指导。