改进型自偏置带隙基准源电路设计

谭传武,傅宗纯

(湖南铁道职业技术学院电务学院,湖南株洲 412001)

商用5G 技术促进了各行各业走向智能化,全国已开通5G 基站共12.6 万个[1-2],5G 基站要求低时延、大连接、高速率等特点去匹配各行各业智能化的应用需求[3],然而5G 基站的耗电量高居不下,各行各业在智能化推进的同时,也要考虑耗电量等硬件和服务成本[4-5]。因此,降低5G 基站的能源消耗是目前推进智能化最为紧迫的课题。基站的电源管理芯片是能源的核心元件[6-7],其带隙基准源的稳定性和功耗直接影响芯片的综合性能,进而直接影响基站的能源消耗[8],因而5G 低功耗技术成为了目前的研究热点。

5G 技术商用以来,研究者在降低基站功耗上面都做了很多相关研究。中国电信股份有限公司广东研究院何峣发表了"业务流量特征对5G 基带芯片功耗的影响分析"的研究成果[9],通过研究典型移动业务的流量特征,能够准确地分析其对5G 基带芯片功耗的影响,并且能够为终端的功耗优化提供依据,但不能直接降低终端功耗;北京邮电大学邹林琳提出了一种新型的自适应传输策略[10],通过引入传输与空闲双模式,让收发机选择更好的信道条件来完成数据传送,该方案基于信道条件自适应地选择传输或空闲模式,以实现节约能量的目的,但自适应的传输策略实现过程较复杂。因此,该文在基站的电源管理芯片上进一步研究,改进带隙基准源电路结构,进而降低芯片本身的功耗,来达到降低基站功耗的目的,在传统的带隙基准源结构上进行改进,设计一种结构简单、功耗低的带隙基准结构,旨在为降低5G 基站的能耗提供改进思路。

1 带隙基准的基本原理

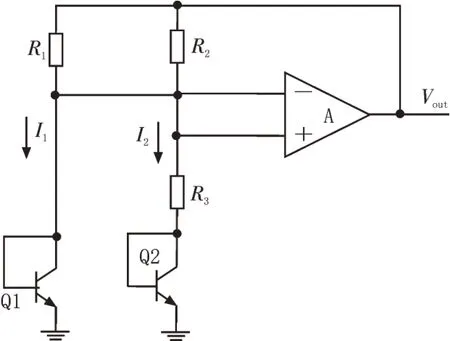

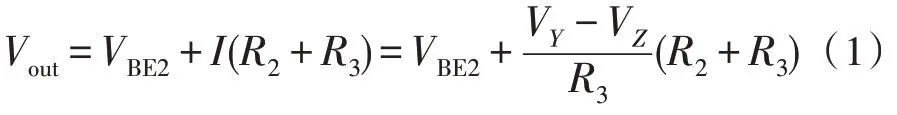

带隙基准电压产生是依据硅锗等材料的PN 结电压与工艺和温度无关的特性[11-12],利用ΔVBE的正温度系数(电阻)与晶体管VBE的负温度系数相互匹配,实现零温度系数的基准电压[13-14]。传统的带隙基准电路结构如图1 所示。

图1 传统带隙基准的基本结构

结合运放的虚短和虚断理论[15-16],从图1 可知,应用运放输入端“虚断”理论可得:

假设运放的开环增益足够大,可得:

选择适当的n与R2、R3的值,可以使式(6)为0,可近似认为基准输出与温度无关。

2 带隙基准电路设计

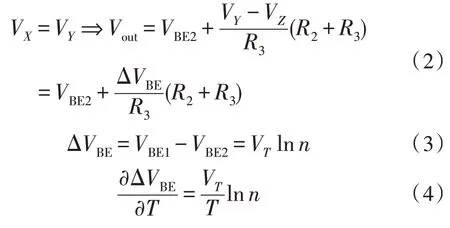

运放结构设计如图2 所示,运放使得两个输入点的电平相等[17-18]。第一级采用共源共栅结构保证电路的高增益,同时把双端信号单端化[19-20]。第二级采用共源放大器,两级之间接一个2 pF 的MOS 电容,迫使主极点向原点靠近[21];电路设计时将运放输出级的电阻值减小,目的是让次极点与主极点远离,达到提升运放稳定性的效果。

图2 运算放大器

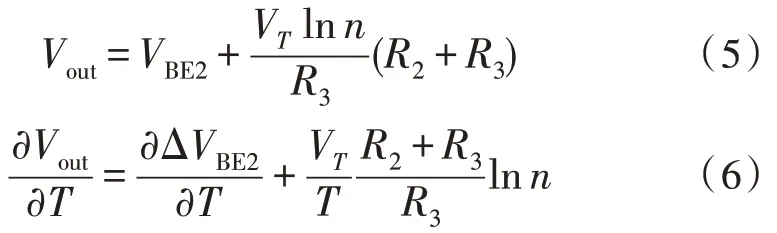

该文改进了传统的带隙基准电路,如图3 所示,由运放的虚短理论可得[22],DPNP15B 与DPNP14B 的电压被强制相等,由电阻大小可得,流过PNP 管I5 和PNP 管I4 的电流之比为10∶13,而I5 和I4 的个数比为8∶2,可得ΔVBE电压如式(7)所示。

图3 带隙基准源电图

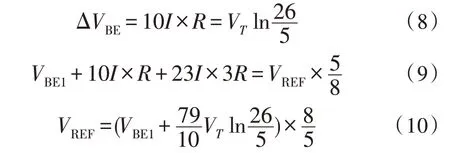

假设流过I5 的电流为10I,则流过I4 的电流为13I,设PNP 管I5 上方电阻为R,则I4 处电阻为3R,可得VREF(BP17D)的计算如式(8)、(9)、(10)所示。

基站的电源管理芯片要求带隙基准低功耗,以达到省电、高效的目的。改进的带隙基准电路是自偏置结构,DPNP1B 为偏置电压(由带隙产生),BP17D为带隙输出,包含带隙核心、运放和偏置电路三部分。

改进的带隙核心电路中,对I5 和I4 上的电阻进行了改进,并联了同阻值的若干个电阻,用于调整带隙电路基准的稳定性。

改进的偏置电路中,用同样尺寸的27 kΩ电阻进行串并联组合,用于调整偏置电流,使得输出电流恒定,偏置电路与基准输出构成负反馈,保证了偏置输出的稳定性,同时保证了带隙电压的稳定性。

3 带隙基准仿真

对带隙基准电路进行Hspice 仿真,在常温下将电源电压从2 V 变换到5 V,结果如图4 所示。电压稳定在1.18 V 左右。

图4 带隙输出对电源电压变化的仿真

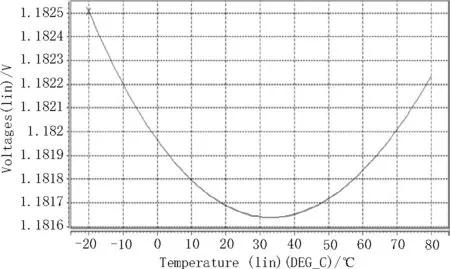

设定温度从-40~+125 ℃变化,扫描仿真结果如图5 所示,在温度变化下,带隙输出为1.181 6~1.182 5 V,温度系数仅5.45 ppm/℃,基准随温度变化影响极小。

图5 带隙输出对温度变化的仿真

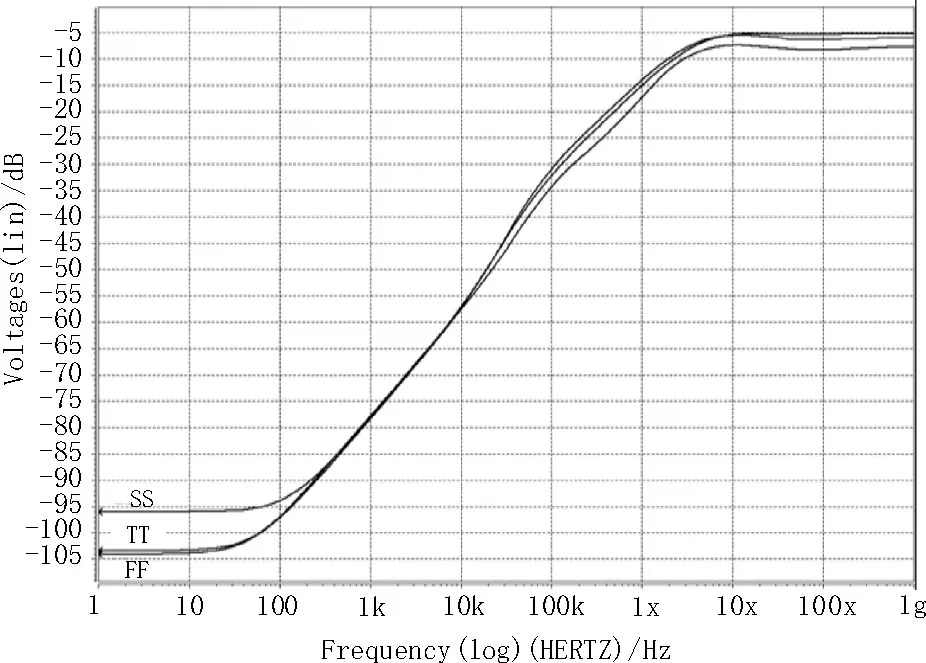

对基准源电路进行电源抑制比仿真,结果如图6所示。

图6 基准源电路的PSRR仿真

由图6 可以看出,在TT、FF、SS 3 种工艺角下,电源抑制比达到95 dB 以上,电路具有很强的低频电源纹波抑制能力。

4 结束语

针对目前5G 基站高功耗的问题,该文提出改进电源管理芯片中带隙基准的结构方案,依据方案改进了传统的带隙基准源的结构,设计了一种结构简单、功耗低的自偏置带隙基准电路。该电路无启动电路既节省了芯片面积,又达到了降低功耗的目的,能广泛应用于电源管理芯片中,为降低5G 基站高功耗问题,提供了解决思路。