全高清视频实时压缩编码与存储系统设计与实现∗

王红亮,马 军,曲 皎

(中北大学电子测试技术国家重点实验室,山西 太原 030051)

通信技术、移动终端的升级换代,大数据处理技术的快速发展带来社会生产生活方式的巨大变革。视频影像娱乐方面人们更追求高清、全高清、超高清分辨率的细腻画面[1];军工产业方面,高质量的影像资料能更好地促进工程的顺利开展,而此领域面临着上一代视频设备采集存储设备的更新换代问题。为了解决视频采集分辨率低,视频压缩算法压缩比低,存储设备速率低和容量不够等问题[2],设计了一种全高清视频压缩编码与存储系统,整个系统外接HDMI 接口的全高清视频(分辨率为1 920∗1 080P@60 frame/s),采用H.264 高压缩比编码算法,并实现压缩码流的本地固态存储。

1 方案设计

综合考虑开发周期、开发难度及实际需求等因素,本设计选用硬件压缩方案,根据通用性及易购买性,选用华为海思的Hi3516A 芯片,此芯片可以实现全高清视频H.264 三个档次的编码,内嵌了ARM处理器,运行Linux 操作系统[3],芯片支持多种分辨率及帧频的视频输入。

本系统大容量视频存储模块采用FPGA +FLASH 阵列实现Hi3516A 芯片压缩编码图像数据的存储。FPGA+FLASH 阵列存储方案是目前大容量视频存储的主流方案[4],利用并行总线技术和流水线设计组成的FLASH 阵列容量大,速度高,后期可根据实际应用需求进行FLASH 阵列的扩展,继续提高存储速度和容量[5-6]。

系统总设计框图如图1 所示,整个系统包含视频接口转换模块、视频实时压缩编码模块和视频存储模块三个部分,全高清数字视频为输入源,视频经压缩后存储在FLASH 中,最后由外部USB 读数设备将压缩码流文件上传至PC 端解码播放。

图1 系统总体设计框图

视频接口转换模块将HDMI 接口的音视频混合差分信号转换成为BT1120 接口的YCbCr4:2:2 格式的视频以便于Hi3516A 的接收。本着功能模块化设计和仪器通用性设计的考虑,视频接口转换电路由FPGA 控制,将Hi3516A 平台自带的视频接口预留出来,在今后系统移植、不同模块组合时方便二次开发。视频压缩模块将BT1120 接口的视频经H.264 编码压缩后通过USB2.0 接口将H.264 裸流发送至视频存储模块,此模块通过Hi3516A 的MPP(软件开发平台)提供的API 接口以及libusb 库提供API 接口开发应用程序实现。视频存储模块由USB 2.0 接口电路模块和FLASH 存储电路模块两部分组成,用于读取USB 2.0 接口的压缩码流并存储在FLASH 阵列中。

2 Hi3516A 视频压缩编码设计

视频压缩编码模块主要以海思的Hi3516A 开发板为设计平台,完成软件流程的设计。图2 为Hi3516A 软件设计框图。

图2 Hi3516A 软件设计框图

本系统通过调用MPP 提供的相关API 接口完成BT1120 接口视频的输入、处理及编码,H.264 码流的实时传输通过Hi3516A 平台的USB 2.0 接口实现。

Hi3516A 软件中的系统控制主要完成硬件复位及初始化、公共视频缓存池的初始化、MPP 初始化及各功能模块的绑定功能。在视频输入之前,需要先进行系统初始化任务,具体流程如下。

2.1 视频输入

Hi3516A 内部经集成视频捕获单元VICAP(Video capture),它包含一个视频输入设备:Dev0,和一个物理通道:Chn0,Dev0 获取的图像经Chn0 到达VPSS 模块。

视频输入程序段流程图以及相应的API 接口如图4 所示。输入设备和输入通道需要配置的属性有输入视频分辨率,扫描方式,像素格式,目标图像大小等,成功时配置函数返回值为0。需注意输入通道Ch0 配置的目标图像大小不得小于输入设备Dev0 配置的图像大小。至此,启动视频输入模块,开始采集BT1120 接口的视频数据。

图3 系统初始化程序流程图

图4 视频输入程序段流程图及API

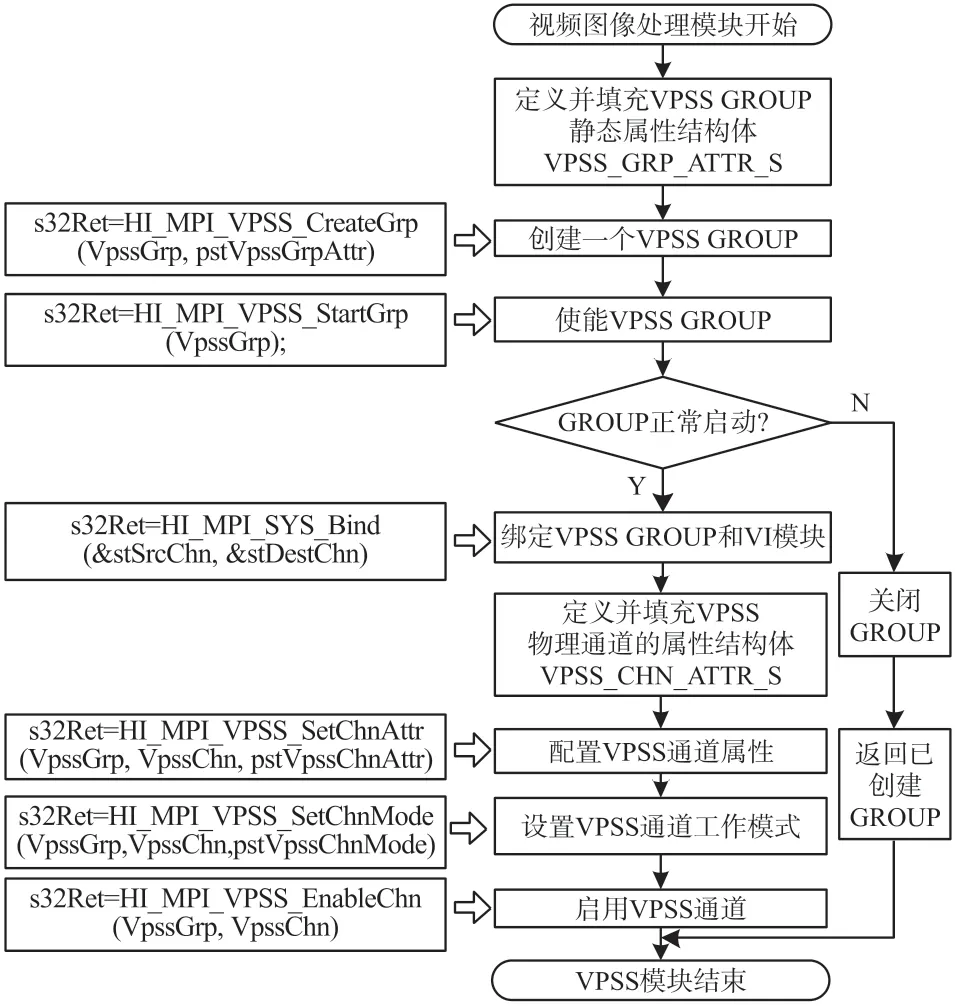

2.2 视频处理

VI 模块获取的视频需经过VPSS(视频处理子系统)模块,此模块完成视频数据的预处理,包括去隔行、去噪、遮挡、裁剪、缩放等。

VPSS 模块流程图以及相应的API 如图5 所示。此模块主要完成VPSS 组和通道的创建以及VPSS和VI 的绑定。Hi3516A 平台支持VPSS 模块创建一个组,组接收VI 模块采集的1 080P 视频,然后送到VPSS 通道,VPSS 通道可与视频编码模块通道对接。

图5 视频处理程序段流程图及API

2.3 视频编码

Hi3516A 集成视频硬件编码器,支持H.264、H.265、MPEG 等多种编码算法。本系统编码模块创建一个编码通道对接VPSS 通道,完成输入视频的H.264 编码。

VENC 编码模块包含码率控制器(RC)和编码器(Encoder)。RC 支持三种码率控制模式,VBR(可变比特率)、FIXQP(固定QP 值)和CBR(固定比特率),本系统选用CBR 模式来实现平均码流速率编码。兼顾输入视频的分辨率、帧率和输出视频的质量要求,本系统设置为4 096 kbit/s 的码流速率,输出帧率设置为25 frame/s。编码模块流程图以及相应的API 接口如图6 所示。

图6 视频编码程序段流程图及API

编码模块产生的H.264 码流需通过开辟线程发送出去。图7 所示为码流获取发送流程图及相应的API 接口。Hi3516A 多媒体处理器支持多种外部通信接口,本系统选用USB 2.0 接口进行通信,它将编码完成后的码流发送至视频存储模块。USB 2.0 的批量传输利用libusb 提供的API 接口完成。

图7 码流获取发送流程图及API

3 FPGA 逻辑程序设计

Hi3516A 平台生成的H.264 码流通过对接FPGA 平台的USB 接口来完成存储。总体逻辑如图8 所示,由Sil9135 接口控制模块、FLASH 阵列控制模块、USB2.0 接口控制模块组成。

图8 FPGA 总体逻辑框图

视频接口转换电路以SiL9135A 芯片为核心,将通过HDMI 传输的高清数字视频转换为BT1120 接口信号输入到Hi3516A 平台,此芯片的配置通过IIC 总线由SiL9135 控制模块来完成,相关寄存器如表1 所示。

表1 Sil9135 寄存器配置

USB2.0 接口芯片选用 Cypress 公司的CY7C68013A,此芯片配置为Slave fifo 模式,作为从设备与FPGA 进行通信[7],本系统采用官方提供的从FIFO 模式固件程序。只用到一个数据读FIFO,将地址线设置为00,选择端口2。FPGA 通过异步读CY7C68013 A 端口2 FIFO 中的数据来实现与接口电路的通信。

USB 读数状态转换图如图9 所示,复位进入IDLE 空闲状态,当检测到端口2 状态指示信号FLAGA 为1(端口2 FIFO 非空)时,发送读FIFO 指令,流程为顺序USB_SLOE 和USB_SLRD 信号置0,在RD_CMD 状态停留8 个时钟周期后USB_SLRD 置1,此时数据异步读出到缓存FIFO,而后由FLASH控制模块获取。

图9 USB 读数状态转换图

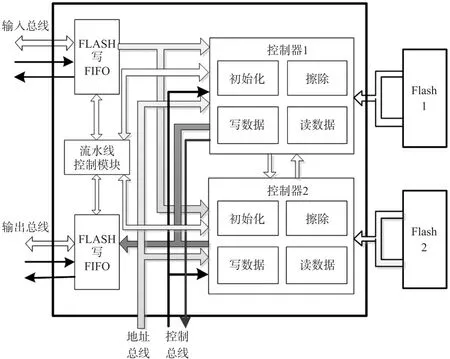

本系统选用2 片MT29F256G08AUAAA FLASH作为存储介质。FLASH 控制模块逻辑如图10 所示。该模块设计了标准的FIFO 数据和控制接口信号来完成与外部FIFO 的通信,模块内部利用并行总线技术将两片FLASH 扩展到16bit,并简化控制逻辑,使用单总线控制技术,在流水线操作方式下完成两片芯片的读写、擦除操作,大大提高读写速率和操作效率。

图10 FLASH 控制模块结构图

4 系统测试

4.1 系统功能测试

利用USB 读数设备将存储与FLASH 中的码流数据读出,在PC 端用多媒体软件VLC 解码播放,测试结果如图11 所示。

图11 VLC 播放H.264 文件界面

通过VLC 软件播放接收到H.264 文件,可以看到视频播放流畅,无卡顿,且无明显丢帧或乱码导致的花屏绿屏。和摄像头原始图像相比,如图12,视频效果无肉眼可辨差别,说明从视频获取到编码、存储、回读,整个流程工作顺利,系统功能良好。

图12 摄像头原始图像

4.2 系统性能测试

本课题性能测试包含码率、压缩比和视频质量测试三部分。码流速率可用迅雷影音查看,在播放H.264 文件过程时,右击鼠标,点击媒体信息可看到基本媒体信息如图13 所示。

图13 视频流基本媒体信息

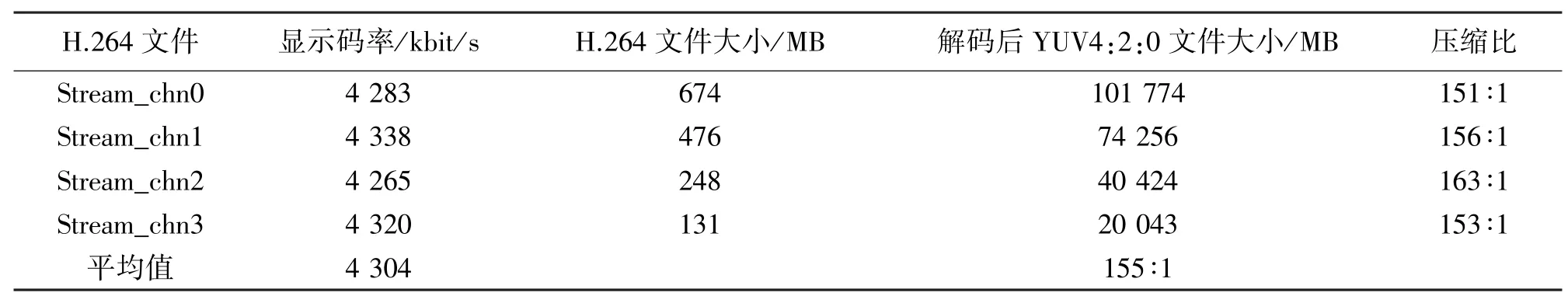

本课题设置的H.264 编码输出码率为4 096 kbit/s,从迅雷影音软件可看到文件类型为H.264 文件,分辨率为1 920∗1 080,码率信息为4 283 kbit/s。测试多组视频流,观测其码率,测试结果如表2 所示。平均值为4 304 kbit/s,有(4 304-4 096)/4 096≈5%的误差。

表2 码率及压缩比测试

将上述码流文件用有“瑞士军刀”之称的FFmpeg 软件解码成YUV4:2:0 格式的文件[8-10],对比解码后YUV 格式文件和压缩后的H.264 文件大小,计算其压缩比,利用如下公式计算压缩比:

压缩比=YUV 格式文件:H.264 文件大小

测试结果如表2 所示,压缩比平均值在155 ∶1左右,表明压缩性能良好。

主要从主观评定和客观评定两个方面来评定压缩视频的质量。国际电联ITU BT-500 建议在视频主观评价定义的标准中,将图像质量分为优、良、中、差、劣[11],但因主观测试评定主观性强,本课题采用客观质量测试方法对图像质量进行测试,通过计算PSNR 值来进行评估,其含义是峰值信号与噪声信号之比[12],计算方法为式(1)、式(2):

式中:2n-1 与量化精度相关,n为像素量化精度。MSE(Mean Squared Error)为原始图像和处理图像之间的均方误差,其中1 920 和1 080 分别是图像宽度值和高度值,X和Y分别是原始图像和解压后图像像素值。

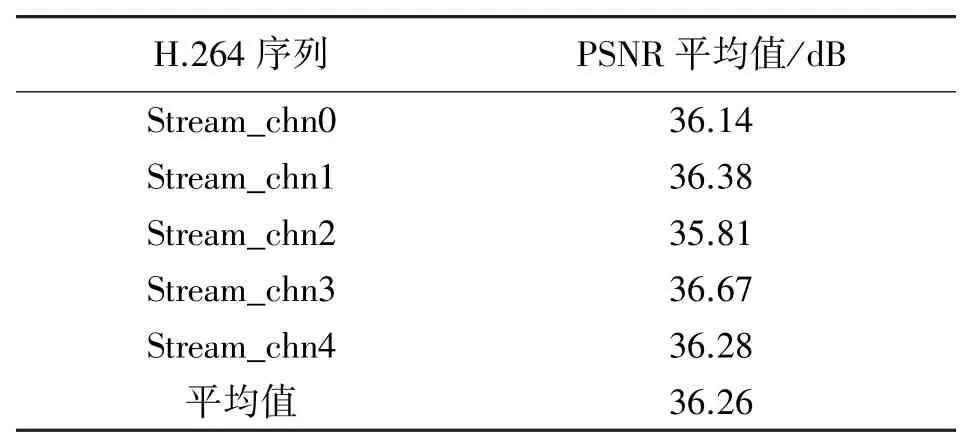

通过MATLAB 计算压缩后H.264 文件相对于解码后原始YUV 文件的PSNR 值,五个不同情景下计算的PSNR 值及其平均值如表3 所示。

表3 不同视频RSNR 测试

PSNR 平均值为36.26 dB。通常来说,PSNR 值超过28 dB 时,图像质量的差异不明显,在35 dB~40 dB 时,肉眼已无法分辨图像之间的差异,表明本系统压缩质量良好。

5 总结

本文针对传统军工领域视频采集存储设备分辨率低,存储时长等缺陷设计了全高清视频实时压缩编码与存储系统,从功能和性能的两方面对系统测试的结果表明,此系统能将1 920∗1 080 的全高清视频实现150 ∶1 的编码压缩比,且压缩码流可进行达36 h 时长存储,很好地实现了视频压缩与存储的设计任务。另外,此系统可进行编码算法的进一步优化达到更好的压缩质量和更小的数据量。系统也可从接口等方面扩展其应用场景及实用性。