基于ATE的高速RapidIO交换芯片测试方法

李军求,刘天照,刘鹏

(工业和信息化部电子第五研究所,广东 广州 511307)

0 引言

RapidIO交换芯片是一种点对点的包交换技术[1],可以高速地传输一个系统内各种设备间的数据,本文通过对RapidIO交换芯片的功能特性进行分析,给出了在基于ATE测试平台下针对高速RapidIO交换芯片的测试项目及测试方法,并进行了实际的测试验证。

1 总体测试内容

交换芯片在功能和参数上有着一般数字集成电路的特性,如:需开展常规的配置模块功能测试、扫描链测试和存储器mbist测试,以及以普通I/O端口输入/输出高低电平、传输延迟等。但交换芯片作为一个在特定协议下的交换枢纽器件,又有其特有的功能模块测试。对于高速RapidIO交换芯片,其高速串行接口众多,特性测试即是重点也是难点。在基于ATE的平台上,对RapidIO交换芯片的主要测试项目如图1所示。

图1 基于ATE的高速RapidIO交换芯片测试

2 功能测试

高速RapidIO交换芯片一般都为大规模数字集成电路,芯片在设计时一般都考虑到了后续测试的覆盖率问题而引入了可测性设计(DEF)[2],因此,针对芯片的扫描链(Scan)、芯片片上存储器的内建自测试(mbist)是检测芯片逻辑故障的有效手段[3],交换芯片一般都具有I2C及JTAG配置接口,其相应的读写功能测试也是功能测试中必不可少的项目,除此之外,针对交换芯片特有的交换模式功能,还应该进行端口绑定模式、中断和包交换功能测试。

对于上述功能测试,在ATE上一般是通过运行相应功能对应的测试仿真向量进行的,即ATE将仿真向量中要求的所有激励信号按规定时序要求灌入芯片,同时对芯片的输出信号进行实时比较,当符合期望值时,功能测试通过。

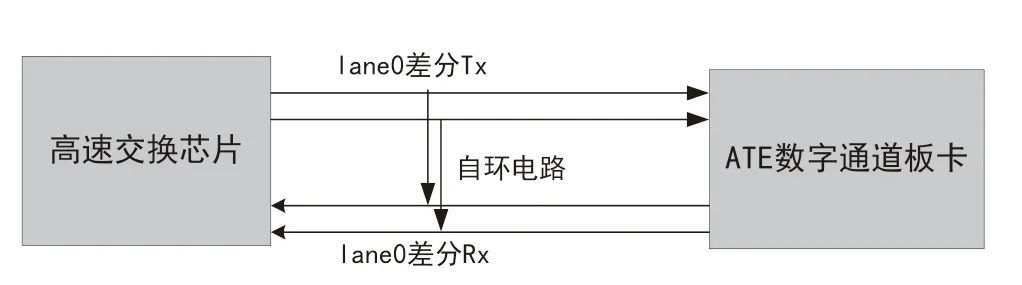

RapidIO交换芯片高速串行接口众多,一般情况下多达30余条链路,因此,如何快速、全面地对这些接口进行测试是一个必须解决的问题。高速串行接口的一条链路(lane)包含一对Tx差分输出信号和一对Rx差分输入信号,利用Tx的数据发送和Rx的数据接收能力,可以通过测试板上自环走线(LoopBack)进行收发测试,从而达到用较低的成本实现高覆盖率的测试目的,如图2所示。

图2 高速串行接口自环测试示意图

在实际的测试中,Tx和Rx之间一般不是直接相连,而是通过电容进行AC耦合,滤除直流分量以避免直流共模电平不一致导致工作不稳定现象。在自环测试中,Tx持续地发送PRBS7或者更长的PRBS31码流给Rx端,Rx端接收数据后进行判断,并通过一个GPIO引脚输出高/低电平来表征自环测试通过与否。自环测试在占用ATE较少的高速测试资源情况下,对所有的高速串行接口进行物理特性测试验证,是一种经济、高效的测试手段[4]。

3 通用I/O参数测试

对于交换芯片的通用数字I/O引脚,其相应的直流参数如输入高低电平、输出高低电平、输入漏电流和输出漏电流;交流参数如数据建立/保持时间、输出传输延时等都可参考GB/T 17574—1998 《半导体器件集成电路第2部分:数字集成电路》部分进行测试。

4 工作电流测试

高速RapidIO交换芯片的工作电流在当其所有的高速串行接口都进行满速工作时达到最大值,在ATE测试中,可以利用芯片自环功能测试以获得最大的工作电流,具体的做法为:配置交换芯片的高速串行输出接口为全速自环模式,包括外部自环及内部自环,ATE在执行芯片自环测试的同时,监控电源通道的输出电流。

5 高速串行接口测试

5.1 差分输出共模电压及差分电阻测试

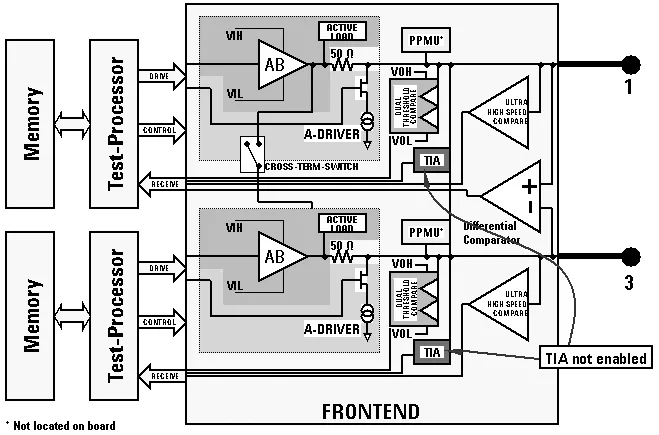

对于高速RapidIO交换芯片的差分输出共模电压及电阻的测试,可以通过ATE机台通道的PPMU测量单元(如图3所示)来完成。在共模电平测试中,先对芯片进行上电,然后控制ATE的数字通道PPMU对芯片的差分输出端直接进行电平测量即可得到共模电压;在测试差分电阻时,需利用ATE通道PPMU的并行测试能力,同时对差分引脚进行拉灌电流操作,并读出两端的电压值,最终计算得出差分电阻。

图3 ATE数字通道硬件资源示意图

5.2 差分输出上升/下降时间测试

高速RapidIO交换芯片的差分输出上升/下降时间的测试,ATE机台主要利用高速通道对信号的上升下降沿进行步进扫描得出。需要注意的是,高速RapidIO交换芯片的差分串行输出信号的速率已达GHz级别,上升/下降时间都是百ps级,由于ATE测试板的整板尺寸较大,信号从芯片的串行差分引脚输出到ATE机台数字通道的接收比较单元的传输距离可达25.4 cm(10 inch)左右,整条通路的阻抗匹配及串扰等问题将会对测试结果有很大的影响,因此需要在测试板设计制作过程中对高速信号的完整性做出足够的考虑[5-6]。

5.3 差分输出摆幅、抖动及眼图测试

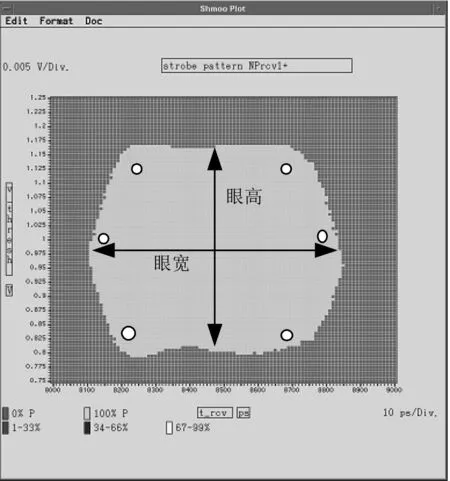

对于高速RapidIO交换芯片的差分输出摆幅、抖动及眼图测试,都可以归结为眼图测试。眼图是把信号各个周期的波形叠加到一个周期中,形成了类似眼睛的形状。一个由示波器抓取的实际眼图如图4所示。

图4 示波器抓取的信号眼图

在ATE测试中,主要是通过Shmoo进行二维扫描测试得出信号的眼图,如图5所示。眼图测试中,首先,需建立并调试好(功能测试通过)用于眼图测试的功能向量;然后,对待测输出引脚的的每个数据位(以最大速率对应的1UI时间为范围)进行时间轴和电压轴的二维扫描。

图5中的横轴代表时间,纵轴代表比较电压门限值,图中眼高即为差分输出摆幅,信号总抖动等于信号单位位宽(1UI)减去眼宽值。

图5 ATE抓取的眼图

6 高速RapidIO交换芯片的测试验证

被测芯片为支持RapidIO2.0协议的高速RapidIO交换芯片,其串行接口速率可达5 Gbps,本次测试的平台为V93000测试系统,整个测试涵盖了功能测试、动态功耗测试、通用I/O端口的交直流参数测试 和高速串行接口参数测试,各个部分的测试结果如下所述。

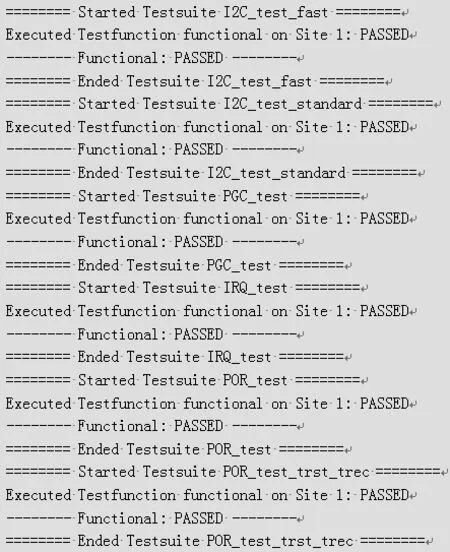

a)功能测试结果

功能测试结果如图6-7所示。

图6 部分模块的功能测试结果

图7 自环测试结果

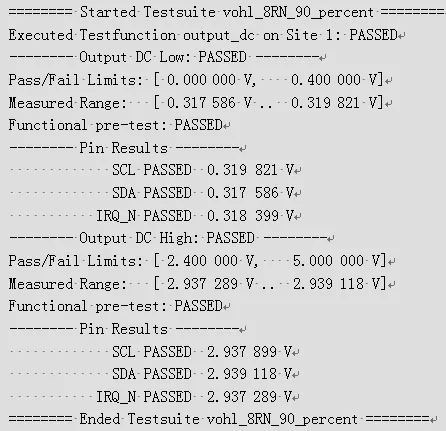

b)部分通用I/O参数测试结果

部分通用I/0参数测试结果如图8-9所示。

图8 输出高低电平的测试结果

图9 输入漏电流的测试结果

c)功耗测试结果

功耗测试结果如图10所示。

图10 各个速率的自环功耗测试结果

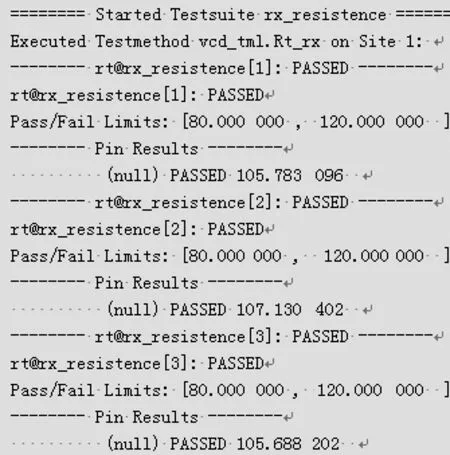

d)串行接口差分输出阻抗测试数据及实现代码

差分输出阻抗部分的测试结果如图11所示。

图11 差分输出阻抗测试结果

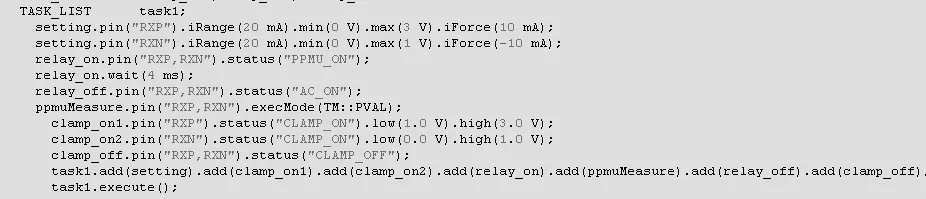

差分输出阻抗部分的测试代码如图12所示。

图12 差分输出阻抗的测试代码

e)高速串行接口差分输出上升/下降时间的测试数据

输出信号上升/下降时间的扫描结果如图13-14所示。

图13 输出信号上升时间扫描结果

图14 输出信号下降时间扫描结果

由上升/下降测试数据可知,当取信号摆幅的20%~80%来测试上升/下降时间时,信号上升时间为34.9 ps,下降时间为43.6 ps。

f)高速串行接口输出眼图测试

本次眼图测试是在高速串行接口输出5 Gbps码流速率下进行的,测试结果如图15所示。

图15 输出信号眼图测试结果

由图15的眼图测试数据可知,该差分信号的输出总抖动为1-0.85 UI=0.15 UI,输出摆幅达600 mV。

7 结束语

本文给出了RapidIO交换芯片在基于ATE的测试平台上的测试项目及高速接口相关参数的测试方法,并对一款高速RapidIO芯片进行了测试验证,在工程实践上有一定的参考意义。