基于HDLC帧的零开销带内管控设计与实现*

刘 远,谭 觅,王纲领

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

高级数据链路控制(High Level Data Link Control,HDLC)协议,由于其封装简单,且具有良好的流量控制能力和差错检测能力,被广泛应用于各类数字通信领域中[1]。

为满足信道两端对数据通信的有效管控,需构建管控数据通道,由于HDLC帧通信的同步传输特性[2],带内管控是较为有效和简单的管理方式,既可以简化用户的网络拓扑,又具备较好的可靠性。由于HDLC帧数据承载着用户的关键通信信息,因此带内管控数据通道的构建不应对用户数据造成损坏。

现有的HDLC帧带内管控数据通道构建技术[3]无法满足在HDLC帧满带宽传输条件下,管控数据即时传递且对HDLC帧零损坏的要求。本文提出的零开销带内管控技术,可以有效解决此设计难点,提高HDLC帧数据的传输效率。此外,管理帧采用伪随机序列,可实现管控信道误码纠错。使用现场可编辑逻辑门阵列(Field Programmable Gate Array,FPGA)方案实现设计,可提高功能实现的可靠性,降低引入的信道时延。

1 HDLC帧结构

HDLC协议以帧作为单位传输数据,基本的帧结构如图1所示[4]。

图1 HDLC帧结构

标志F为开始或结束标志字。固定为16进制码“7E”,当信道处于空闲状态时,标志F也作为帧与帧之间的空闲填充。如果开始和结束标志位之间的帧数据含有“7E”,需对数据进行转译[5]。地址域为接收端的地址。控制域用于构成各种命令和响应,以便对业务链路进行监视和控制。信息域为帧的净荷数据部分,根据不同的行业标准,长度限制也有所不同。帧校验域为两个标志位之间数据的CRC校验结果[6]。

本文所设计的HDLC帧的零开销带内管控技术,不需要解析HDLC帧的内容。本文中的“HDLC数据”是指HDLC帧去掉开始和结束标志“7E”后的数据内容。

2 管控帧示例

端到端通信设备之间传递的控制数据,以自定义帧的方式传递。本文提供一个管控帧结构的示例,如图2所示。

图2 管控帧示例

帧头设定为伪随机m序列[7],用于指示管控帧的起始位置。本文使用的m序列生成多项式为:

初值设置为0,截取使用其前8字节数,即16进制数“83CA90BB7DCF897A”。长度字段L代表整个管控帧的字节数,自定义位为1字节长度;净荷数据为管控帧内承载的管控信息数据,用户自定义其最大长度;校验和字段用于验证管控帧数据传输的正确性,本文使用1个字节的累加和进行校验。

3 实现原理

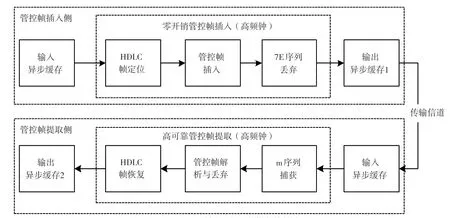

根据HDLC帧的特点,帧头帧尾的标志位都是“7E”,结合自定义管控帧的数据结构,设计基于HDLC帧的零开销带内管控方案如图3所示。

图3 基于HDLC帧的零开销带内管控实现原理

3.1 输入输出缓存

采用对HDLC帧进行随路钟缓存、高频钟处理的方式[8],构建管控数据通道。输入输出缓存用于随路钟与高频钟的隔离,同时保证管控帧插入和提取处理时,不影响数据通信的连续性。

输出异步缓存1中需缓存2个字节数据,用于预留判断HDLC帧标志位时产生的延时。输出异步缓存2中需缓存管控帧最大长度字节数,确保在管控帧解析与丢弃的时候,输出数据不被间断。异步缓存的设计,将会引入信道传输延时,延时的计算公式为Lmax×8/R,其中,Lmax表示用户自定义的管控帧最大长度字节数,R表示随路钟的波特率。

3.2 零开销管控帧插入

零开销管控帧插入工作在高频时钟域,由3个模块组成,其中,HDLC帧定位模块根据HDLC帧结构特点检测HDLC帧的标志位。管控帧插入模块,使用高频时钟实现管控帧数据的一次性插入,插入管控帧的位置在HDLC帧定位模块检测到2个标志位后的位置,保证在管控帧插入位置的HDLC帧间隔内至少有2个标志位,从而满足HDLC帧恢复模块的实现要求。

“7E”序列丢弃模块使用高频时钟,在插入管控帧之后的“7E”位置,根据管控帧插入的总长度,完成对“7E”数据的丢弃,以保证管控帧的插入不会对链路引入新的开销。根据HDLC数据间标志位“7E”的个数,分两种情况完成“7E”序列的丢弃。

情况1:当管控帧插入位置的HDLC数据间的“7E”字节数大于或等于L+2时,如图4所示,在一次性插入管控帧数据后,可以连续完成管控帧长L的“7E”数据丢弃。

情况2:当管控帧插入位置的HDLC数据间“7E”字节数小于L+2时,如图5所示,在一次性插入管控帧数据后,不能连续完成管控帧长度L的“7E”数据丢弃,需要在后续HDLC帧间继续丢弃“7E”,并且保证HDLC数据间至少留有1个“7E”,用于指示HDLC帧间隔。

图5 管控插入的帧间空闲L<+2(含满带宽情况)

3.3 高可靠管控帧提取

高可靠管控帧提取,工作在高频时钟域,由3个模块组成。其中,m序列捕获模块通过自相关计算实现m序列定位[9],设置相关判决门限为60,8字节m序列可以实现3比特纠错[10];管控帧解析和丢弃模块基于管控帧格式完成帧解析,并根据解析出的长度完成管控帧数据的丢弃,删除对HDLC帧空闲的占用;HDLC帧恢复模块,根据HDLC数据间标志位“7E”的数量和进入方向“7E”序列丢弃模块的原理,分以下几种情况完成HDLC帧的恢复。

情况1:当管控帧丢弃后,数据仍为“7E”,则可以一次性回填管控帧长度L的“7E”,此过程为图4的逆向。

图4 管控插入的帧间空闲≥L+2

情况2:当管控帧丢弃后,数据为非“7E”,说明在下一帧HDLC数据后仍需回填“7E”,图6表示在管控帧丢弃后,下一个HDLC数据间隔中,“7E”个数大于1的情况,可以直接在这个帧间隔中回填L长度的“7E”。

图6 能在管控帧下一帧HDLC间隔完成一次性“7E”回填

情况3:当管控帧丢弃后,数据为非“7E”,并且下一个HDLC数据间隔中,“7E”个数等于1时,则需在这个帧间隔中回填1个字节的“7E”,然后继续寻找下一个HDLC数据间隔,继续回填,直至回填完L长度的“7E”,恢复原始HDLC帧数据,如图7所示。

图7 不能在管控帧下一帧HDLC间隔完成一次性“7E”回填

在HDLC满带宽情况下,原始HDLC帧头和帧尾至少组成2个标志位,结合零开销管控帧插入中情况2的“7E”序列丢弃原理和高可靠管控帧提取中情况3的HDLC帧恢复原理,可以实现HDLC帧满带宽通信情况下的零开销管控数据传输。

4 FPGA实现

FPGA实现和仿真都基于第3节中自定义的管控帧结构开展设计。

4.1 零开销管控帧插入FPGA实现方案

实现方案如图8所示,通过异步缓存、管控帧高频插入、标志字“7E”的判决、丢弃等方式,实现零开销管控帧插入。

图8 零开销管控帧插入FPGA实现方案

4.2 高可靠管控帧提取FPGA实现方案

如图9所示,通过异步缓存、管控帧高频插入、m序列捕获、标志字“7E”的判决、回填等方式,实现高可靠管控帧提取。

图9 高可靠管控帧提取FPGA实现方案

5 FPGA仿真

使用FPGA仿真软件modelsim对第5节方案进行仿真。

5.1 零开销管控帧插入仿真

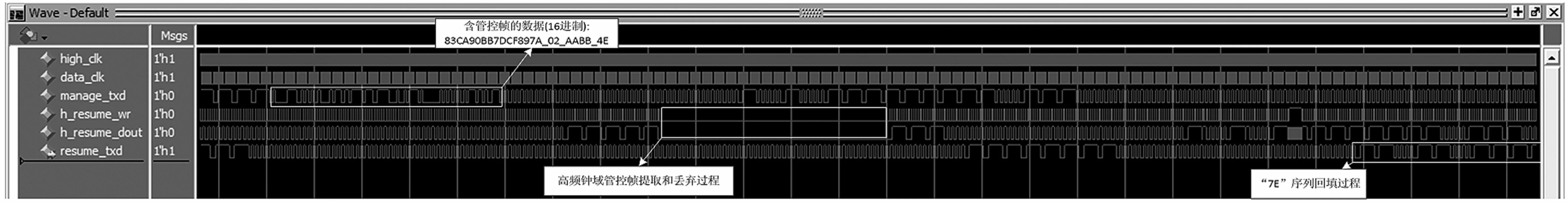

图10为进入方向的仿真结果,信号data_clk和high_clk分别为随路钟和高频钟,信号manage_in_flag为管控帧插入指令,信号org_rxd为输入的HDLC帧数据,信号h_manage_dout和h_manage_wr分别为进行管控帧插入和“7E”序列丢弃的高频钟域数据和有效信号,信号manage_txd为完成管控帧插入和“7E”序列丢弃后的随路钟域输出数据。仿真结果显示,在收到管控帧插入指令后,通过高频钟完成管控帧数据的插入和“7E”序列的丢弃,并将含有管控帧数据(83CA90BB7DCF897A_02_AABB_4E)的HDLC通信帧通过随路钟输出。

5.2 高可靠管控帧提取仿真

图11为外出方向仿真结果,信号manage_txd为含管控帧数据的随路钟域HDLC帧数据(图10的输出结果),信号h_resume_dout和h_resume_wr分别为进行管控帧提取、丢弃和“7E”序列回填的高频钟域数据和有效信号,信号resume_txd为完成管控帧丢弃和“7E”序列回填的随路钟域输出数据。仿真结果显示,通过m序列捕获,定位到管控帧位置,并通过高频钟完成管控帧数据的提取、丢弃和“7E”序列的回填,并将最终恢复的HDLC帧原始数据通过随路钟输出,实现了HDLC帧的零开销带内管控功能。

图10 零开销管控帧插入modelsim仿真结果

图11 高可靠管控帧提取modelsim仿真结果

6 结语

本文提出了基于HDLC帧的零开销带内管控技术,有效解决了端到端HDLC通信零开销带内管控通信构建的难点问题,在保证不损坏原有HDLC帧的条件下,提高了带内管控通道的性能,可以满足在HDLC帧满带宽传输条件下的零开销带内管控需求。该技术可以有效应用于信号资源有限、传输带宽紧张的环境中,如卫星无线通信等环境。本文给出的FPGA详细设计方案,实现简单、资源占用少,可灵活应用于各种规模的FPGA设计项目中。FPGA仿真验证结果证明了本方案的可实现性。此外,本文所提方案已经在多个项目中得到应用。