28 nm Polarfire FPGA单粒子瞬态脉冲宽度检测技术研究

杨华锦,陈 伟,郭晓强,汤晓斌†,陈飞达,张凤祁,王 坦

(1. 南京航空航天大学 材料科学与技术学院,南京211106;2. 强脉冲辐射环境模拟与效应全国重点实验室,西安710024)

当空间环境中的高能辐射粒子(质子、α粒子、重离子等)入射集成电路后,可能诱发单粒子效应(single event effect,SEE)导致电路功能发生错误[1],影响集成电路系统的工作稳定性。

早期SEE关注最多的是单粒子翻转(single event upset,SEU)效应,近年来随着芯片工艺制程和集成电路工作频率的大幅提升,单粒子瞬态(single event transient,SET)效应导致的软错误在引发错误总数的占比逐渐上升[2-3]。有研究表明,当芯片的特征工艺处于28 nm时,SET导致的软错误将有可能占据主导地位[4]。因此有效捕获SET效应并明确其特征参数对分析SET传播规律等有着重要意义。

最初检测SET效应是通过在片外搭建测试系统,利用高精度示波器直接测量SET脉冲[5-6]。用这种方法可以得到SET脉冲波形等基本参数,但是SET脉冲在路径传输中易发生失真[7];为此提出在片内设计检测系统对SET效应进行分析研究,而SET脉冲宽度作为SET的重要参数[8-9],与SET在电路中向下传播被时序电路捕获造成电路故障密切相关[10-12]。故可利用时间-数字转换电路(time to digital converter,TDC)进行SET脉冲宽度的分析,包含可变延时脉冲宽度检测电路[13-17]和抽头延时脉冲宽度检测电路[18-19]。TDC电路可利用FPGA的可重复编程特性,在FPGA内部进行生成、调试及功能验证。

伴随着FPGA在空间中的广泛应用,获取FPGA中的SET脉冲宽度及其分布变得越来越重要。28 nm Polarfire FPGA是Microsemi第五代非易失性FPGA[20]。相比 SRAM型FPGA,Polarfire FPGA对SEU具有一定的免疫能力[21]。不同FPGA内部的布局设计存在很大的差异,同时FPGA内部的布线资源调用也有所不同。若忽略TDC电路布局设计而额外引入的布线资源延时,会对TDC电路的检测精度、检测阈值和分辨率等指标产生很大的影响。

本文依据Polarfire FPGA内部资源布局特点对上述两种SET脉冲宽度检测电路进行结构设计。以故障注入的方式,从时间分辨率、检测精度、宽度测量阈值、死时间[22]以及资源占用这5个TDC电路功能指标出发,研究两种SET脉冲宽度检测电路的差异,并分析影响SET脉冲宽度检测电路的因素,最终明确两种SET脉冲宽度检测电路在Polarfire FPGA中的适用条件。

1 电路设计

1.1 可变延时脉冲宽度检测电路设计

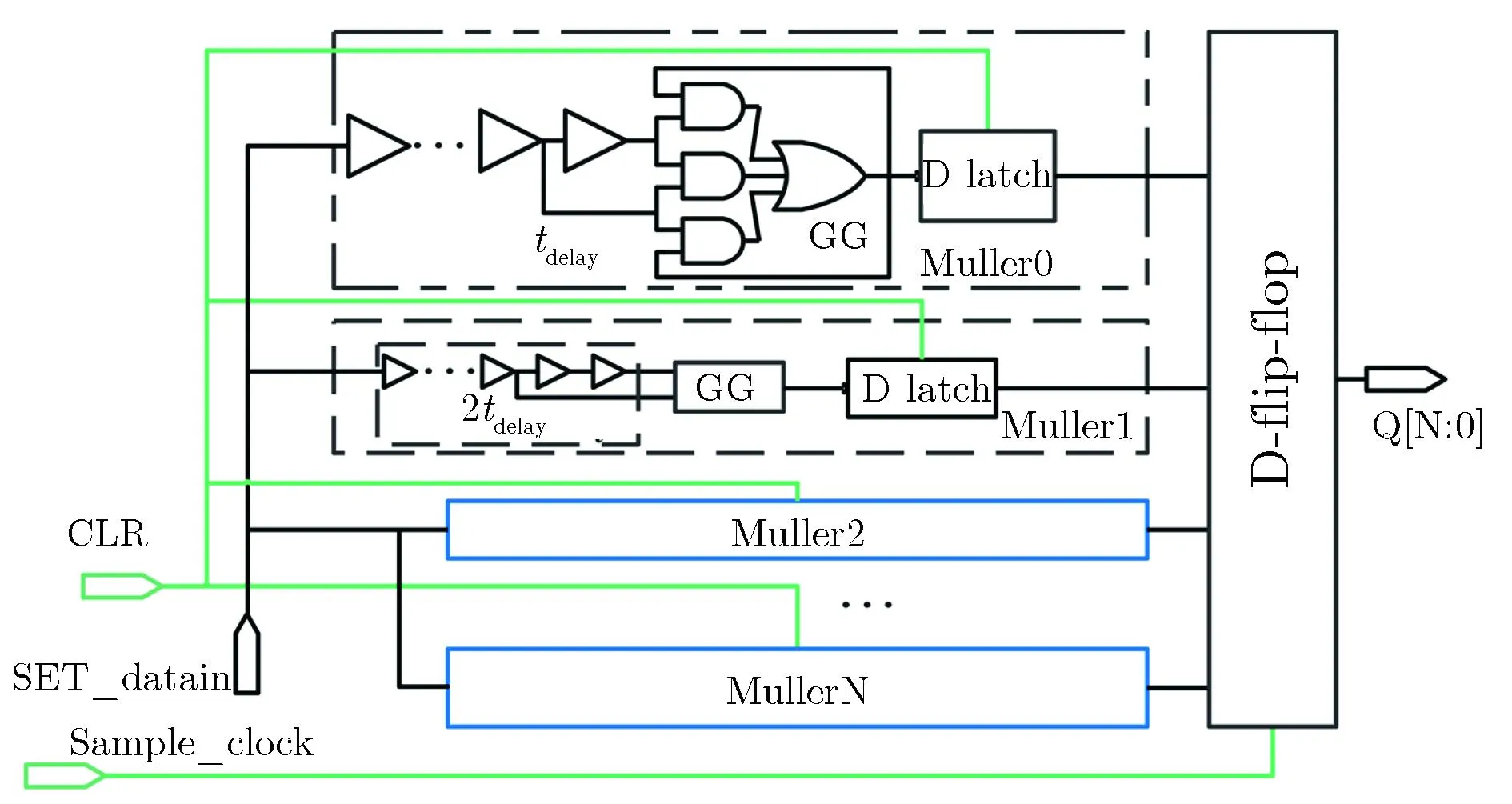

可变延时脉冲宽度检测电路如图1所示,包括3个基本组件:(1)延时模块tdelay,用来控制保护门两个输入端口之间的延时差;(2)保护门(guard gate,GG)[14],有两个输入、一个输出,当两个输入值同时为1(0)时,输出为1(0),两个输入不同时,输出保持上一时刻的状态不变;(3)异步锁存器,捕获并输出保护门状态,利用异步复位信号对锁存器进行清零。

图1 可变延时脉冲宽度检测电路

当某一个SET脉冲输入电路时,SET信号遍历所有的检测模块。在可变延时脉冲宽度检测电路输出时:若SET脉冲宽度小于(N+1)·tdelay(N为触发器状态改变个数,tdelay为单元延时),脉冲信号不能通过保护门,锁存器输出为低电平;当SET脉冲宽度大于N·tdelay,锁存器输出状态发生改变,判定该SET脉冲宽度Wpulse大于N·tdelay,则有

tdelay·N≤Wpulse≤tdelay·(N+1)

(1)

可变延时脉冲宽度检测电路的检测精度即为tdelay。在实际的电路布局设计中,因SET脉冲输入的两条路径上都同时包含有布线延时,FPGA内部布局特点对可变延时脉冲宽度检测电路的影响不大。

为实现可变延时脉冲宽度检测电路的连续检测,采用CLR时钟信号进行控制,同时为避免检测电路出现大的误差,对可变延时脉冲宽度检测电路的复位时钟信号和采样时钟信号的频率以及占空比进行设计:(1)采样时钟fs,保证采样时对锁存器捕获输出的输出信号完成至少一次采样;(2)复位时钟fCLR,包含工作时间T0和复位时间T1。

因可变延时脉冲宽度检测电路的工作状态受复位时钟调节,设复位时钟为自变量,采样时钟和复位时钟在设计时存在关联。

SET最大脉冲宽度Wmax与电路对SET的容忍阈值相关,在设计可变延时脉冲宽度检测电路复位时钟信号时需保证电路能检测到Wmax。同时基于对SET脉冲宽度的连续检测,设电路在1 s内完成M次检测任务,此时复位时钟周期应满足:

(2)

M与实际的采样时钟fs相关。

电路仅需要一个很短的时间即可完成复位,故在复位时钟之内还需要调节时钟占空比λ。根据Polarfire FPGA数据手册可知,时钟的建立保持时间最大为500 ps,故T1应大于500 ps。

图2为可变延时脉冲宽度检测电路复位时钟设计时序图。由图2可见,pulse1,pulse2正处于复位电路高低电平转折位置,pulse4处于复位时间内。此时的SET脉冲因为清零信号的出现,而不被检测电路所捕获分析。为避免SET因电路设计出现统计偏差,此时对该时间段内可能出现的SET脉冲数η进行统计,表示为

(3)

而理想采样时钟fs为匹配复位时钟,其占空比与复位时钟相同。但是其相位要相对于复位时钟滞后。

图2 可变延时脉冲宽度检测电路复位时钟设计时序图

1.2 抽头延时脉冲宽度检测电路设计

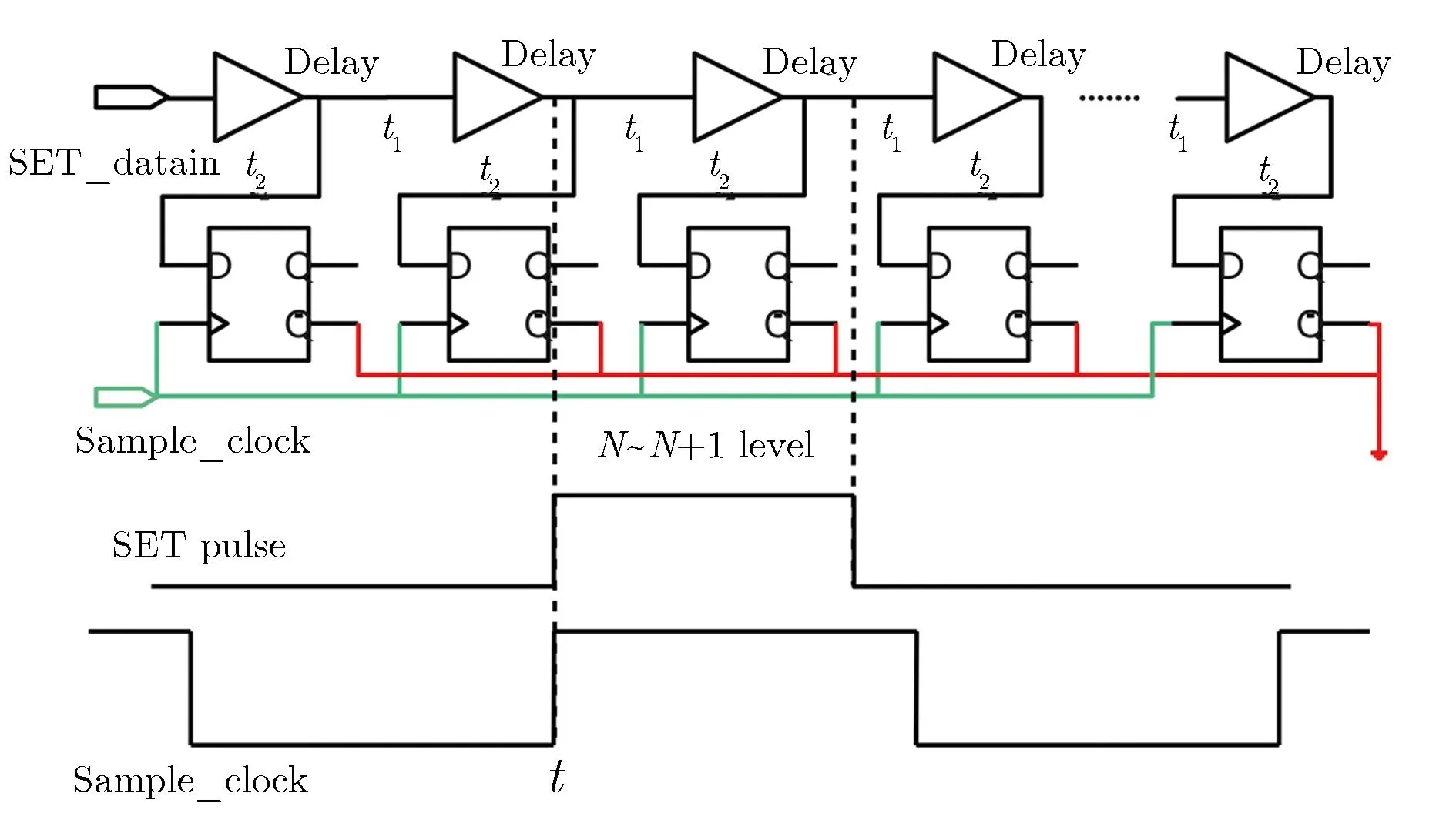

抽头延时脉冲宽度检测电路[23]内部结构为由级联的延时单元和触发器。电路将每一个延时单元的状态通过抽头的方式引出,利用延时单元来量化SET脉冲宽度,其结构与时序如图3所示。

图3 抽头延时脉冲宽度检测电路的结构与时序

电路原理以检测正脉冲为例,所有触发器初始输出状态为低电平,SET信号由datain进入抽头电路,在延时单元链内进行传输,当采样时钟Sample_clock的上升沿到来时刻t,每个D触发器都会捕获与之相连的延时单元状态,通过计算SET在t时刻经过的延时单元个数,即可确定此时SET在电路中的位置及其脉冲宽度。

单个SET脉冲宽度Wpulse可表示为

Wpulse=N·tdelay(±0.5tdelay)

(4)

在抽头延时脉冲宽度检测电路中,实际的分辨率为t1+t2+tdelay(t1)为相邻延时单元延时;t2为延时单元与触发器之间的布线延时。

因在电路中抽头延时脉冲宽度检测电路中每一级延时单元与延时单元、延时单元与触发器相互之间的布线延时保持一致,近似认为一个延时单元的延时就是三个延时的总和tdelay。抽头延时脉冲宽度检测电路的检测精度由电路所选用的单级延时单元延时所决定,为±50%tdelay。延时单元的单级延时的大小和采样时钟的频率共同决定了抽头延时脉冲宽度检测电路的级数。

在进行连续SET脉冲宽度检测时,为避免SET脉冲发生遗漏或误测,在确定电路级数n时要满足式(3),保证SET脉冲在电路中的总延时大于系统采样频率,n可表示为

(5)

组成TDC电路时,需保证相邻延时单元的逻辑状态能进行有效传输。但在Polarfire FPGA中,可编程逻辑资源并不总是满足抽头延时脉冲宽度检测电路中相邻延时单元的布线延时一致的条件,图4为Polarfire FPGA中LC布局特点。Polarfire FPGA内部布局设计中,由12个可编程逻辑资源组成的logic_cluster(LC),其布线延时可保持一致,在相邻的两个LC之间存在两个额外的短布线延时。

图4 Polarfire FPGA中LC布局特点

TDC电路在Polarfire FPGA中进行布局设计时,会因为short_route_delay的存在导致Δdelay出现不均匀的情况。以图3中抽头延时脉冲宽度检测电路为例,其单级延时基本组成t1,t2,tdelay一般保持一致,但是在横向相邻LC交界处进行布局布线时,抽头延时脉冲宽度检测电路中的t1会因布线延时的加入出现变大的情况,影响TDC电路整体的分辨率与检测精度。因而需要对实际的测试电路进行结构上的调整,以满足TDC电路对SET脉冲宽度的检测需求。

设计了一种抽头延时脉冲宽度检测电路的新型电路结构,如图5所示。利用FPGA内部丰富的逻辑资源,以一条SET信号传输链和多组SET脉冲信号检测组合的方式,实现对PolarfireFPGA布局设计的适应调整。将图4中一个LC作为一个子电路(12级)容器。子电路内部延时单元与触发器相互之间可以忽略布局布线带来的延时差异。构建N组串行抽头延时子电路作为整个检测电路的检测模块,子电路内部级数可以根据电路需求进行调整。同时为避免芯片自身因素导致延时单元出现延时不均的情况,将每个子电路的延时模块配置为环形电路在实际使用前进行校准。此时,一个子电路容器中包含有11级检测模块和一个2输入数据选择器,多组子电路通过SET脉冲光信号传输模块抽头消除了LC之间的布线延时。

图5 抽头延时脉冲宽度检测电路设计

SET脉冲信号传输设计:用一条长逻辑链进行SET脉冲信号传输,此逻辑链中的信号传输单元须保证其不会对SET脉冲宽度产生较大的影响,且不会屏蔽SET脉冲信号。利用identify工具对结构调整后的TDC电路进行分析,在特定SET检测位置进行抽头,将SET脉冲信号注入到每一个子电路中,且每一个子电路中的前后时间衔接完整。

2 检测电路功能影响因素分析

2.1 SET脉冲宽度检测电路单级延时

在Polarfire FPGA中的逻辑资源有两种结构logic_element(LE)和interface_logic(IL):LE内部查找表为4LUT with carry chain,其可以实现任意四输入逻辑运算或算法功能;IL内部为常规4LUT,用以链接特殊IP核与用户逻辑。因二者功能上的差异性,对同一逻辑功能会表达出不同的延时状态,进而影响TDC电路的功能。

为研究Polarfire FPGA中逻辑单元基本延时对TDC电路精度和分辨率的影响,利用周期性脉冲输入数据量大的特点,验证不同查找表结构、不同逻辑状态下的逻辑延时。SET脉冲宽度检测电路选用易于集成的抽头延时脉冲宽度检测电路对查找表基本延迟进行分析。

基于FPGA内部内置晶振提供时钟,利用组合逻辑模块实现信号延时,获得两个在路径上具有延时差异的脉冲信号输出,并进行逻辑运算,得到预期的周期性脉冲,脉冲生成原理与检测结果。图6为周期性脉冲信号生成电路及电路时序图。

(a)Circuit

(b)Timing

通过在抽头延时脉冲宽度检测电路中换用不同的逻辑门(与门和或门等)来分析逻辑基本延时。结果表明,不同查找表单级延时并不会随着逻辑门的变化发生改变。其最终结果如表1所列,4LUT with carry chain的基本延时要小于4LUT。

表1 不同查找表结构之间的延时信息

综合表1结果,选取单级延时较小的4LUT with carry chain作为检测电路的延时模块。通过表1中的延时信息:为保证两种SET脉冲宽度检测电路技术指标对比的有效性,定义两个SET脉冲宽度检测电路的理论SET脉冲宽度检测范围为86~1 032 ps。

若采样时钟选择125 MHz,则抽头延时脉冲宽度检测电路的延时级数设置在115级,可变延时检测电路检测级数设置为12级,依据电路复位信号设计,复位时钟采用100 MHz。

2.2 组合逻辑SET展宽因子

SET脉冲产生并向下传播时,会出现脉冲展宽效应(propagation induced pulse broadening,PIPB),这会直接影响到抽头延时脉冲宽度检测电路的检测结果。不同的LUT结构,其SET脉冲展宽效应[24]的表现也有所不同。为降低SET脉冲宽度测试的不确定度,开展组合逻辑的单元脉冲宽度展宽因子测试工作[25-26],验证LE和IL各自的SET展宽因子。

SET脉冲产生是连续随机离散事件,周期性脉冲无法代表SET脉冲事件进行分析,在验证SET展宽因子时需用单脉冲故障注入的方式来进行,其脉冲生成电路可参考图6(a)。

在SET脉冲宽度检测电路中选用抽头延时脉冲宽度检测电路进行SET展宽因子分析。28 nm的芯片在辐射环境下产生的SET脉冲宽度约为百皮秒量级[27-29],故在注入脉冲时,每百皮秒选取一个脉冲值进行故障注入,Polarfire FPGA中SET脉冲传播极限如图7所示。为避免测量偏差,利用纳秒级脉冲进行补充修正。通过统计分析SET脉冲在逻辑长链中的传播极限[24],得出:4LUT的SET脉冲展宽因子σ1约为1.45 ps每级;4LUT with carry chainSET脉冲展宽因子σ2约为3.35 ps每级(±0.1 ps每级)。

图7 Polarfire FPGA中SET脉冲传播极限

基于二者延时情况(如表1所列)及脉冲展宽压缩因子的差异,抽头延时脉冲宽度检测电路中的SET信号传输模块选取4LUT。并且基于SET展宽因子,可对延时抽头脉冲宽度检测电路得到的每一个SET脉冲宽度检测值进行初步的补偿,得到偏差相对较小的Wture,表示为

(6)

其中,Mi为SET脉冲信号的在长逻辑链中的传播级数,与SET在子电路中所处的位置有关。当SET脉冲宽度足够宽时,会横跨n个逻辑长链,此时n>1。

2.3 扇出负载特性

电路的扇出负载特性[30-31]会影响FPGA逻辑门的驱动能力,直接影响到可变延时检测电路对SET脉冲的检测。为此需调节可变延时脉冲宽度检测电路的输出级数,通过可变延时脉冲宽度检测电路对SET脉冲宽度的检测阈值,分析扇出负载特性与可变延时检测电路的关系,如表2所列。

表2 扇出负载特性与可变延时检测电路的关系

由表2可知,随着扇出数目的增加,可变延时脉冲宽度检测电路的检测阈值不断升高;当可变延时检测电路满足对1 ns宽度的SET脉冲检测能力时(此时的输出级数为12),对于344 ps以下的SET脉冲并无很好的检测能力;且随着扇出数目的变化,电路的检测阈值呈正相关变化趋势;当设置3或4级扇出时,可变延时脉冲宽度检测电路可实现对窄脉冲(<344 ps)的测量,但此时的可变延时脉冲宽度检测电路的上限会非常小,约为344 ps;在实际的电路布局时,可变延时脉冲宽度检测电路资源占用会很小,优势非常明显。

3 脉冲注入结果分析

在实际的SET检测电路功能指标的验证上,同样以单脉冲注入的方式,来分析检测电路对SET脉冲宽度的检测结果与功能指标。

两种脉冲宽度检测电路脉冲注入结果如图8所示。

(a)Tap delay circuit test results

(b)Variable temporal pulse-width detection circuit test results

由图8可见,可变延时脉冲宽度检测电路与抽头延时脉冲宽度检测电路的分辨率基本保持一致,为86 ps。但可变延时脉冲宽度检测电路无法很好地兼顾宽脉冲(>344 ps)与窄脉冲的测量。对窄脉冲而言,理论检测范围在86~1 000 ps的可变延时脉冲宽度检测电路对脉冲宽度小于344 ps的脉冲检测能力并不强,伴随有明显的偏差。

当两个SET脉冲宽度检测电路的检测范围处于86~1 000 ps时,可变延时脉冲宽度检测电路的测量阈值要比抽头延时脉冲宽度检测电路更大,即对于小于344 ps的SET脉冲而言,可变延时脉冲宽度检测电路并没有很好的检测能力。综和扇出负载对可变延时脉冲宽度检测电路的影响,因电路每一级检测模块均处于并行状态,一个SET脉冲信号遍历每一级检测模块,多个电路模块同时作为一个脉冲信号的输入负载,导致整个可变延时脉冲宽度检测电路无法兼顾窄脉冲与宽脉冲的检测。

对宽脉冲(>344 ps)检测而言, SET脉冲展宽因子会影响到抽头延时脉冲宽度检测电路中捕获的SET脉冲宽度Wpulse,导致实际输出的SET脉冲宽度与在辐射环境条件下产生的SET脉冲宽度存在差异,且σi也会在一定程度上限制抽头延时脉冲宽度检测电路的长度以及采样频率。基于SET展宽因子,可对检测电路得到的每一个SET脉冲宽度检测值进行补偿,得到误差值相对小的Wture。

表3为两种脉冲宽度检测电路功能指标对比。在进行资源占用情况对比时,为便于直观,资源占用以1个logic_cluster为单位进行对比分析。由表3可知,可变延时脉冲宽度检测电路检测精度比抽头延时脉冲宽度检测电路低约43 ps,检测阈值高约200 ps,且存在有1.4 ns的死时间。

表3 两种脉冲宽度检测电路功能指标对比

当两个检测电路的理论脉冲宽度检测范围为86~1 000 ps时,抽头延时脉冲宽度检测电路的逻辑资源占用约20个逻辑长链,而可变延时脉冲宽度检测电路资源占用13个逻辑长链(不包括复位时钟模块)。但当两种检测电路扩大电路检测范围时,可变延时脉冲宽度检测电路的资源占用增幅要比抽头延时脉冲宽度检测电路大。当可变延时脉冲宽度检测电路的检测上限上升至1 376 ps时,占用的LC数目将上升至32个,而抽头延时脉冲宽度检测电路的资源占用为22个。

4 结论

基于Polarfire FPGA布局特点对两种SET脉冲宽度检测电路进行设计,通过对比二者的技术指标得出,它们对SET脉冲检测的适用范围各有不同:对于脉冲宽度大于344 ps的SET脉冲,可选用抽头延时脉冲宽度检测电路进行检测,此时的抽头延时脉冲宽度检测电路在检测精度和测量阈值的优势非常明显,并且抽头延时脉冲宽度检测电路的输出结果可利用SET展宽因子对SET脉冲宽度进行补偿;但对于脉冲宽度小于344 ps的SET脉冲,可变延时脉冲宽度检测电路对SET脉冲的检测能力优于抽头延时脉冲宽度检测电路,此时可变延时脉冲宽度检测电路的资源占用以及检测阈值优势都非常明显。本文明确了在FPGA中集成SET脉冲宽度检测电路所需要考虑的FPGA自身的设计特点,需基于不同的FPGA设计结构对不同的SET脉冲宽度检测电路进行适应性结构调整。Polarfire FPGA中的SET脉冲宽度检测电路设计思路,可为SET脉冲宽度检测电路在其他系列FPGA中的实现提供参考。