基于三维线性反馈移位寄存器的三维堆叠集成电路可重构测试方案

陈田,鲁建勇,刘军,梁华国,鲁迎春

(1.合肥工业大学 计算机与信息学院,合肥 230601;2.情感计算与先进智能机器安徽省重点实验室(合肥工业大学),合肥 230601;3.合肥工业大学 微电子学院,合肥 230601)

0 引言

传统二维集成电路(Two-Dimensional Integrated Circuit,2D IC)的发展速度已经变慢,而高密度垂直互连的三维集成架构是目前作为延续摩尔定律的替代方案之一。三维集成技术包括在三个维度上互连的集成电路[1],这种从水平互连到垂直互连的转换在信号传输速度和提升集成电路的(Integrated Circuit,IC)整体性能上非常有前景。利用过硅通孔(Through Silicon Vias,TSV)作为中间介质的三维堆叠技术也是三维集成技术的一种,该技术的特点是能够减少裸片间的互连长度,降低功耗以及增加带宽等,相较于2D IC,提高了集成电路性能[2-4]。但更高的性能也对集成电路测试技术提出更高的要求,而在三维芯片生产成本中,测试成本占据了48%[5],本文的主要目标是降低测试成本。

相较于2D IC,三维堆叠集成电路(Three-Dimensional Stacked Integrated Circuit,3D SIC)的测试流程更复杂,在每次堆叠后都要进行一次测试,一共经历绑定前、绑定中和绑定后测试三个阶段[6-7],以确保良率。复杂的测试流程容易出现冗余的测试资源与较大的测试时间开销。测试时间会影响芯片的生产周期,而测试结构的硅面积开销是重要的测试资源,一颗芯片上的可用测试面积有限。如何利用各个阶段的测试资源并降低测试时间,是降低测试成本的重要方向。

在集成电路测试技术中,内建自测试(Built-In Self-Test,BIST)是在电路中植入相关的功能电路以实现待测电路自我测试功能的技术,一般由测试模式生成器、响应分析器和BIST 控制器组成[8]。线性反馈移位寄存器(Linear Feedback Shift Register,LFSR)作为测试模式生成器,结构简单,能够以较小的测试数据存储量生成所需的测试模式,同样适用于3D SIC;但LFSR 生成的测试模式具有伪随机特性,测试功耗较高,如何降低测试功耗,是降低测试成本的重要方向。

测试结构的硅面积开销、测试功耗以及测试时间开销都是测试成本的重要组成部分,本文基于LFSR 构建了一种可重构的三维LFSR(Three-Dimensional LFSR,3D-LFSR)测试结构,适用于3D SIC 的不同测试阶段,以降低测试成本。

本文的主要工作如下:1)设计了一种3D SIC 测试中的低功耗测试结构,以降低测试功耗;2)设计了一种适用于不同测试阶段的可重构3D-LFSR 测试结构,能够充分复用不同阶段的测试资源,以降低测试结构的硅面积开销;3)对测试数据进行了测试前处理,采用串并行混合测试模式降低测试时间。

1 相关工作

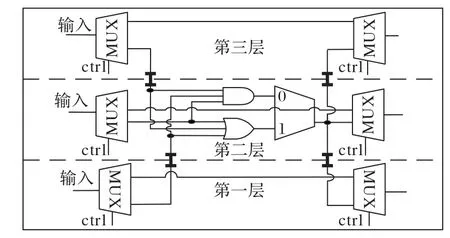

BIST 对伪随机生成器LFSR 生成测试模式的故障覆盖率要求较高,因此使用重新设定种子的技术[9-10]以提升故障覆盖率。如图1 为BIST 下多重多项式LFSR 的结构,通过与门和解码逻辑电路能够更改反馈系数,即更改多项式,达到提升故障覆盖率的目的。本文基于多重多项式的LFSR,利用了可变多项式的特性,连接多层LFSR 以形成级数更大的LFSR 结构,能够满足绑定后形成更大的测试电路的需求。

图1 多重多项式LFSR结构Fig.1 Structure of multiple-polynomial LFSR

2D IC 测试通常只需经历晶圆测试和最终测试。晶圆测试在组装和封装前筛选出有缺陷的集成电路,防止不必要的封装成本;而最终测试则保证封装芯片的质量,以减少测试逃逸。但对于3D SIC,需要定义其他测试,例如部分堆叠后的测试。3D SIC 测试需要经历绑定前、绑定中和绑定后测试[6-7]:绑定前是为了可以测试芯片的传统功能,也可以应用于初步的TSV 测试;绑定中和绑定后则是在堆叠后,确认堆叠过程中芯片的完好性。复杂的测试流程对控制测试成本的要求更高。如何在各个测试阶段充分利用测试资源,是降低测试成本的关键因素。

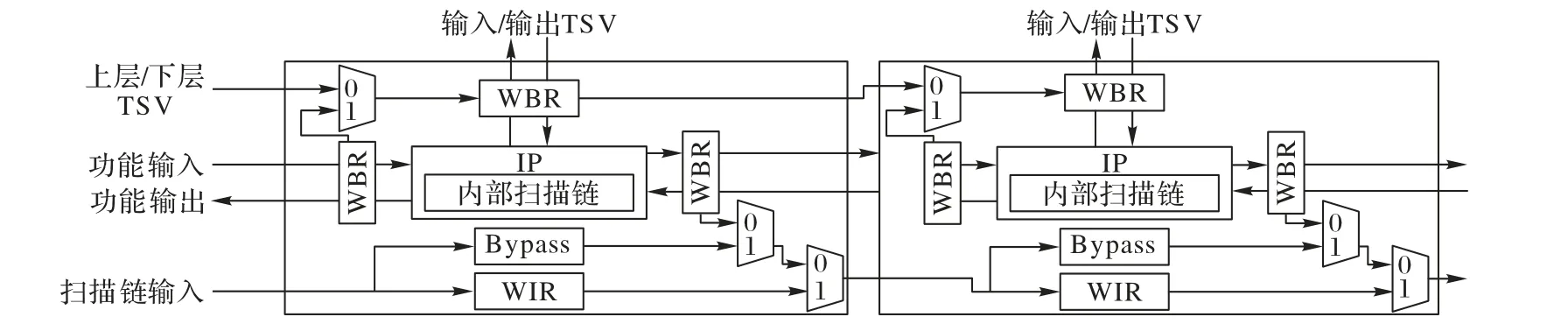

文献[11]中指出,三维集成电路的测试技术和可测试性设计(Design For Testability,DFT)仍是3D 技术成功的关键。目前嵌入式内核的测试wrapper 已经由电气与电子工程师协会(Institute of Electrical and Electronics Engineers,IEEE)进行了标准化,该标准称为IEEE Std1500[11-12],在此基础上,IEEE制定的Std P1838标准[13-14]广泛用于3D 堆叠芯片。图2 为IEEE Std P1838 标准结构图[15],一层内 有两个 知识产 权(Intellectual Property,IP)核,测试外壳指令寄存器(Wrapper Instruction Register,WIR)用于封装测试指令的译码器和控制器,控制各个IP 核的状态转换,进行测试模式的选择和切换。WIR 除了在IP 核的输入输出处添加,也在TSV 的两端添加,以保证层间的IP 核状态的可控性和可观性。测试外壳旁路寄存器(Wrapper Bypass Register,WBR)由多个可扫描的触发单元组成,每个单元由一个D 触发器和两个数据选择器组成,多个触发单元连接起来就类似于扫描链。内部测试模式连接WBR 与内部扫描链进行使用。外部测试模式则单独使用WBR。为了解决层间和层内内核之间穿行和并行测试之间的转换,在该结构的基础上,本文设计了不同层的核间并行和串行测试,增加少量电路以构建低功耗路由模块,同时减少了测试时间和功耗。

图2 IEEE std P1838标准结构Fig.2 IEEE std P1838 standard structure

2 本文方案

2.1 整体结构

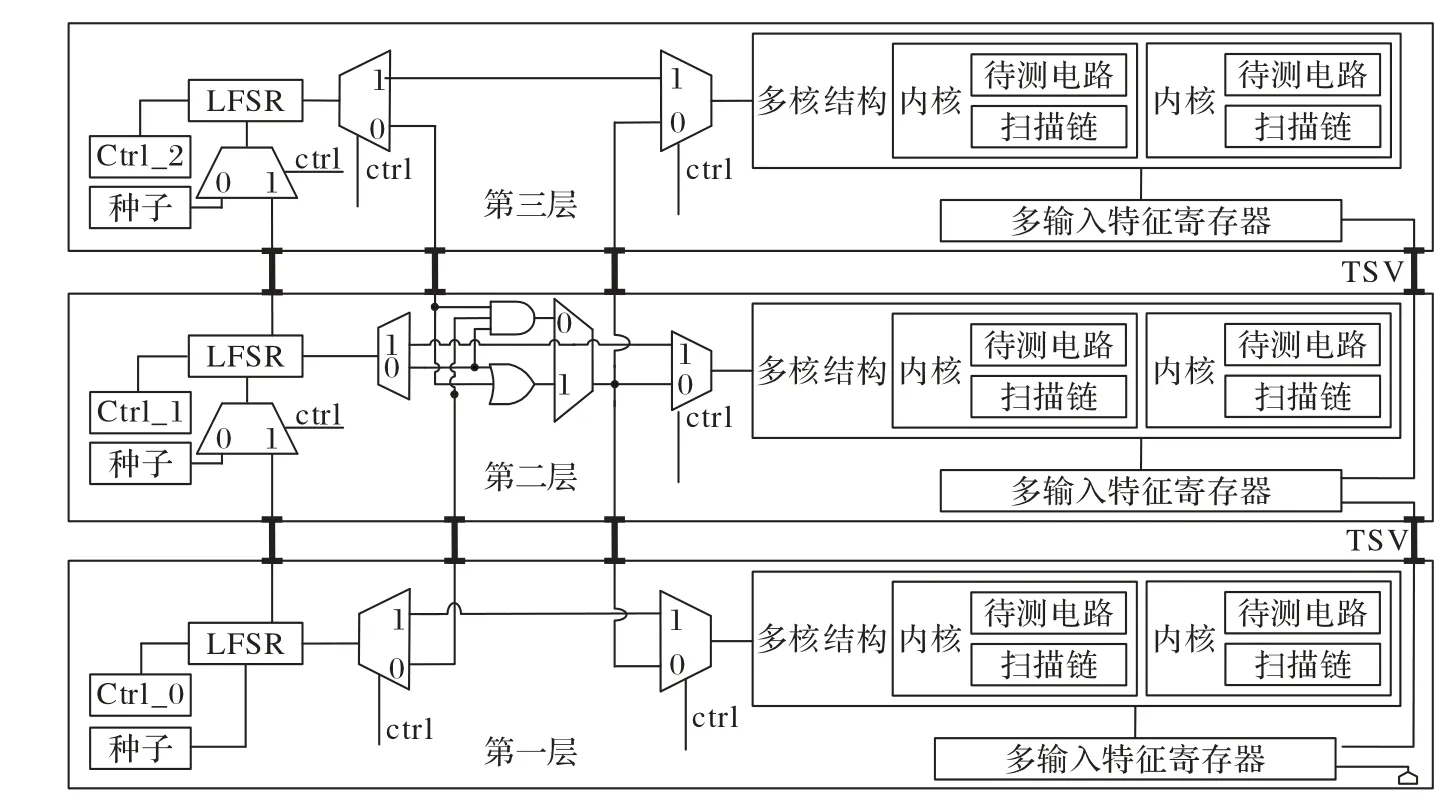

本文方案的总体片上测试结构如图3 所示,主要由3DLFSR、低功耗路由结构、核间互连结构组成。3D-LFSR 复用了绑定前的LFSR,能够在较低测试面积和存储开销的情况下生成测试模式;低功耗路由结构负责将测试模式转换为低功耗的测试模式;核间互连结构则能很好地完成各个内核的并行或串行测试。

图3 本文方案的总体测试结构Fig.3 Overall test structure of proposed scheme

2.2 3D-LFSR结构

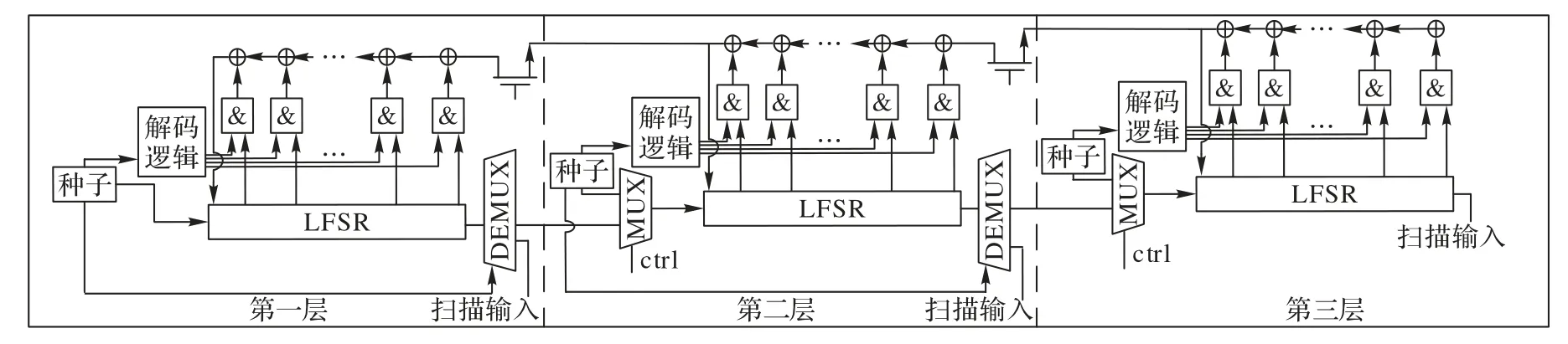

重构后的3D-LFSR 如图4 所示,每层的测试模式生成器包括可更换多项式的LFSR、解码逻辑、控制重构的多路复用器和多路分配器。多项式的更换是通过与门更改LFSR 的抽头位置(tap locations),与门的选择需综合考虑测试面积。多重多项式的LFSR 能够提高测试集编码的成功率。但在三维堆叠集成电路中,若绑定后的LFSR 形成了更大的待测试电路,此时单层的测试模式生成器无法满足测试需求;若在单层设计更大的测试模式生成器,在非绑定后测试阶段,测试资源会被闲置。本文提出绑定后重构LFSR 以解决该问题。

图4 3D-LFSR结构Fig.4 3D-LFSR structure

各层独立的LFSR 通过层间TSV 连接,然后通过附加的多路选择器和多路分配器选择性地决定是否连接LFSR,以组成一个更大的LFSR。本文构建的是三层的3D SIC。当对整体测试时,各层的LFSR 会连接起来。第二层的LFSR 通过使用多路复用器对连接后的LFSR 进行拆分,最终形成两个LFSR:主LFSR 用于生成待测电路所需的测试模式,次LFSR则用于辅助最终生成低功耗测试模式。LFSR 的拆分点根据测试集能够求得的种子的最小级数来拆分。

绑定前测试:测试模式被编码成由一个多项式标识符、1-2 多路分配器的控制信号以及各自多项式的种子组成的输入模式。本文将编码后的数据仍然统称为种子。在测试模式下,建立与多项式标识符、控制信号的反馈链路,将种子加载到LFSR 中,经过移位转换后,生成与原有种子相容的测试模式,最后通过低功耗路由模块加载到扫描链中。

绑定后测试:绑定后形成了一个更大的功能电路,如果进行总体结构测试,所需的LFSR 的级数更大,此时通过控制1-2 多路分配器和2-1 多路选择器的输出端,连接相邻层的LFSR,以形成一个更大的LFSR。通过更换多项式,进行重新编码。

2.3 低功耗路由结构

LFSR 作为测试模式生成器,能够很好地对测试模式进行编码压缩,但生成的二进制测试序列具有伪随机性,在测试模式下会产生高跳变活动,从而增加功耗。由于三维堆叠集成电路结构的复杂性,这个问题变得更为突出。如图5 所示,本文设计了低功耗路由模块来降低测试功耗。

图5 低功耗路由结构Fig.5 Low-power routing structure

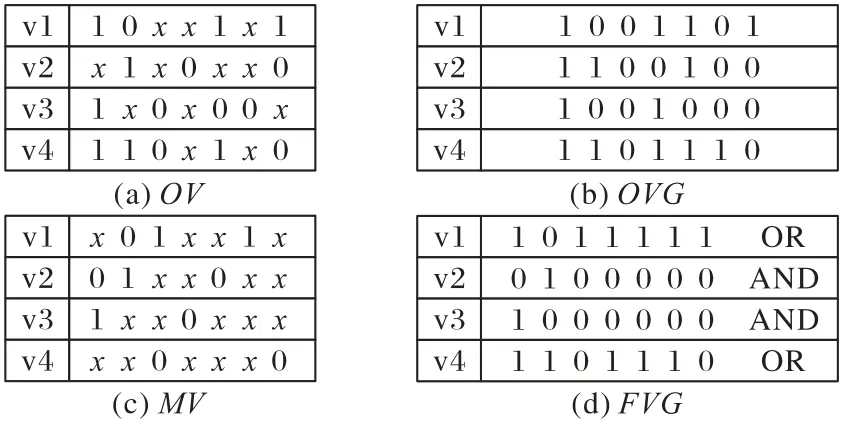

将主LFSR 和次LFSR 生成的测试模式经过与门和或门电路,生成低功耗的测试模式后再路由到待测内核的扫描链中。具体原理如下:如图6(a)所示,原始测试集(OV)是带有无关位的测试集,测试集中0 和1 表示确定位,x为无关位。对于测试模式中的无关位,如果能够全部为0 或1,移位功耗会达到最低。OV在不经过任何处理的情况下由主LFSR 生成不带无关位的测试集(OVG),对应图6(b)。OV转换后的测试集(MV)由次LFSR 生成,对应图6(c)。将OV和MV经由主LFSR 产生的不带x位的测试集(OVG,MVG)中对应的测试模式进行与/或运算,生成最终送入扫描链中的低功耗测试集(FVG),对应图6(d)。

图6 低功耗处理过程中产生的测试集Fig.6 Test sets generated during low-power processing

式(1)中k为测试模式的确定位中数目更大的一方;OVi是OV中的第i条测试模式;count0(OVi)是OV中第i条测试模式中确定位0 的数目;count1(OVi)是OV中第i条测试模式中确定位1 的数目。

式(2)中MVij是测试集MV的第i条测试模式中第j位的值;OVij是原始测试集OV的第i条测试模式中第j位的值;x是无关位为对k取非。OV根据式(2)后得到MV':

式(3)对MV'进行无关位填充得到MV。对于LFSR 重播种,LFSR 级数的设定不小于Smax+4 时(Smax为测试集中最大确定位数目),LFSR 不能成功编码的几率小于10-6[16]。进行无关位填充后,若确定位的数目大于测试集中最大确定位数目,会导致LFSR 级数增加以及种子的长度增加,即增加一定的面积开销和测试数据存储量。因此需要权衡存储量和移位功耗,本文提出填充无关位后确定位的数目不大于原始测试集中的测试模式的最大确定位数目,在不增加面积开销的前提下,仍可通过编程来调控存储量和移位功耗,保证了方案的灵活性。

式(4)中OVG、ijMVGij是OV和MV的i条测试模式中第j位的值,为了使最终送入扫描链的测试模式的跳变数更低,将它们与测试集MV中第i条测试模式按位进行与运算,反之进行或运算,通过式(4)生成所需的低功耗测试集FVG。

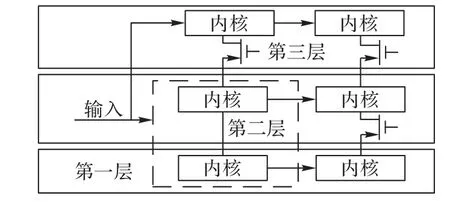

2.4 核间互连结构

在多核的3D SIC 中,除了考虑同一层中内核之间的连接,还要考虑不同层的内核之间的连接。如何使用一组接口访问多层芯片并且能有效地输入和输出测试数据,针对这个问题,提出了IEEE P1838 标准[15]。结合该标准,本文的内核间的互连结构如图7 所示,虚线框中是绑定后形成的更大的待测试电路。IEEE P1838 的标准结构支持串行和并行两种传输方式。串行测试为了节省测试带宽,串联所有IP 核,将测试数据依次输入各个内核,它的缺点是一次只能测一个内核,其他的内核则处于旁路状态。并行测试能够同时测试所有内核以节省测试时间,但缺点是测试带宽较大。

图7 内核间的互连结构Fig.7 Interconnection structure between cores

如果在层内采用并行测试,根据IEEE Std P1838 的控制逻辑,通过旁路寄存器将测试模式并行送入扫描链中;如果层与层之间的内核间符合并行的测试模式,通过IEEE Std P1838 标准提供的层间扫描端口,将测试模式并行送到其他层。并行测试需要满足测试带宽和测试功耗的约束。对于内核间的串行测试,IEEE Std P1838 标准提供了层间和层内的串行接口,使两内核间的扫描链合并为一条以实现串行测试。在整个测试过程中,只采用串行测试会大幅度增加测试时间;只采用并行测试,内核所用的测试模式也无法满足带宽和功耗的需求,采用多通道则会增加带宽。串行和并行混合的测试方法将层间的MOS 管作为开关电路用于控制数据传输,能很好地均衡以上问题。在本文方案中,串行和并行的选择根据测试数据压缩算法来定,能够合并的测试模式采用并行测试方法,否则采用串行的测试方法。

2.5 整体的信号控制

结合图3 来看,每层用2 位的控制信号控制数据的输入输出选择,第二层还需附加1 位对低功耗模块的控制。对于1-2 多路分配器,控制信号为0 表示数据需要经过低功耗模块,即此时的数据满足了低功耗测试生成所需的基本条件,可通过低功耗模块降低移位功耗;控制信号为1 表示数据不经过低功耗模块直接到达后面的2-1 多路选择器。对于靠近扫描链的2-1 多路选择器,控制信号为0 表示将经过低功耗模块的数据输入扫描链;控制信号为1 表示将未经过低功耗模块的数据输入扫描链,也可以表示为不输入数据到当前层的扫描链中,这取决于当前层的LFSR 是否输出了测试数据。

总体的控制信号主要分为00、01、10 和11。控制信号00表示测试数据需要经过低功耗模块后传输到所属层的扫描链;控制信号01 表示测试数据经过低功耗模块但不传输到所属层的扫描链。控制信号01 和10 发生的情况为:当前测试数据所覆盖的为多层逻辑待测电路时,不属于当前待测电路层的LFSR 模块作为次LFSR,控制信号设置为01;当三层待测电路的测试模式相容且满足测试模式生成的条件时,若仅需两层的测试模式便能达到所设的阈值,则无需使用另一层的LFSR 模块,测试控制信号设置为10。

该结构适用于三种测试模式的测试成本优化:绑定前、绑定中和绑定后测试。在绑定前测试只需把控制信号设置为11,此时的测试逻辑电路与常规的基于LFSR 测试电路相同,由LFSR 输出的测试模式直接输入扫描链。对于当前层有多个内核的情况,扫描链中相容的测试数据可以并行测试,以减少测试时间。

绑定中和绑定后测试模式的实现过程基本一致。每层逻辑电路在堆叠后存在两种情况:1)若当前层的测试数据不与其他层的测试数据相容且不满足低功耗测试模式的生成条件,当前层进行单独测试,在不超过测试功率阈值的前提下,多层可以并发测试,减少了测试时间;2)当前层的测试模式与其他层的测试模式相容且满足低功耗测试模式的生成条件,多层LFSR 并行输出测试模式到低功耗模块中,然后并行输出到对应的测试扫描链中。

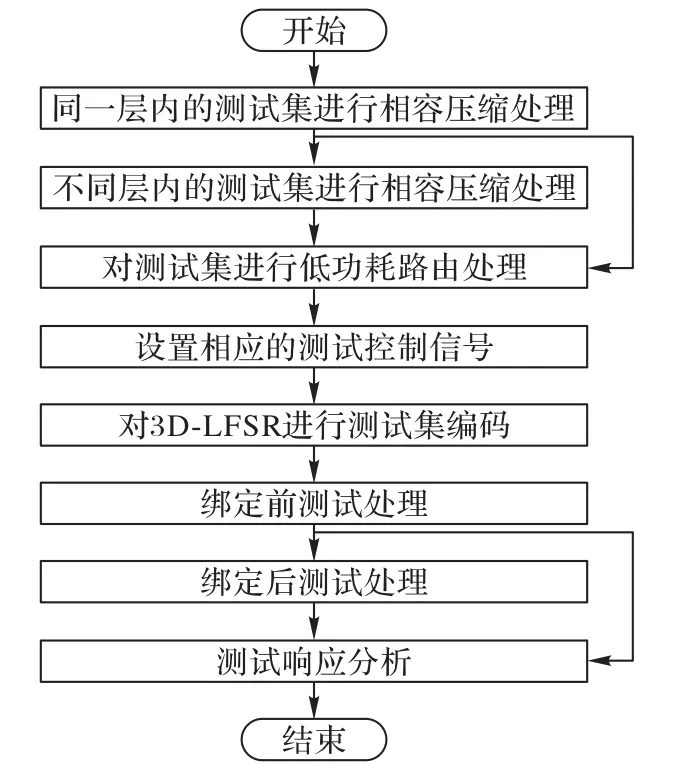

3 测试流程

三维芯片测试包含三种测试模式[8]:绑定前、绑定中和绑定后测试。三维芯片的输入输出引脚在最上层或最底层。本文中三维芯片的所有输入输出口均位于芯片底层,绑定后的测试模式均从底层向上传输,测试流程如图8 所示。

图8 本文方案的测试流程Fig.8 Testing process of proposed scheme

测试相容定义:如果两个测试模式对应位置的确定位相同或者其中一方为无关位,则这两条测试模式相容。例如两条测试模式V0=(a0,a1,…,am-1),V1=(b0,b1,…,bm-1),如果测试模式V0中的任何位置i(0 ≤i≤m-1)的值ai是0 或1,在测试模式V1的对应位置bi是相同值或无关位,则称测试模式V0和V1相容。

绑定前测试阶段:根据测试数据相容压缩原理,对同一层的所有内核进行测试集相容压缩,设置相应的路由控制信号,实现对同一层内的多个内核同时测试,以降低测试时间。对相容压缩后形成的更大的测试集进行低功耗处理,再进行LFSR 编码,填充种子,进行绑定前测试。

绑定后测试阶段:将绑定前各层经过处理后的测试集进行相容测试压缩,设置相应的路由控制信号,实现对多层的多个内核同时测试,以降低测试时间。对相容压缩后形成的更大的测试集进行低功耗处理,再进行3D-LFSR 编码,填充种子,进行绑定后测试。

无论是绑定前还是绑定后测试,LFSR 的级数不仅需要满足绑定前的测试,也需要满足绑定后的测试。具体的级数在测试前根据测试集编码种子后再设置。

4 实验与结果分析

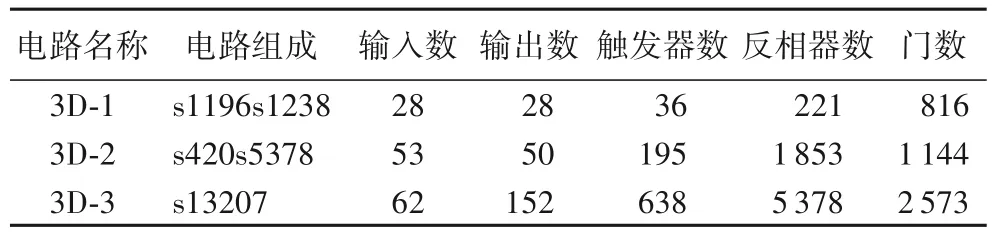

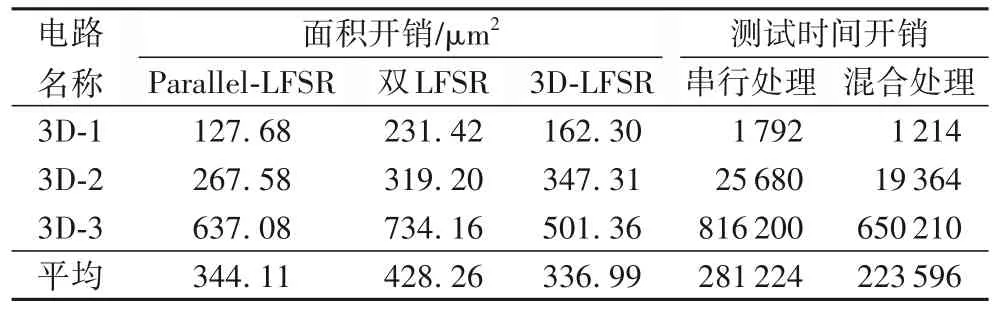

为了验证本文方案的有效性,采用ISCAS’89 基准电路作为实验电路。采用的数据集为ATPG(Automatic Test Pattern Generation)工具生成的测试集。与3D-LFSR 结构进行对比的测试结构来自文献[17-18]。文献[17]对双LFSR测试结构进行优化,以降低测试功耗。文献[18]提出一种多模块连接的LFSR 测试结构Parallel-LFSR 以降低种子存储量和硬件开销。本文将文献[17-18]中的LFSR 测试结构在本文方案中的三维堆叠IC 结构上进行实验,与3D-LFSR 结构进行对比。三维堆叠集成电路设置为三层,具体设置如表1所示。测试成本的组成主要有:测试数据压缩、测试功耗、测试时间以及测试结构面积开销。

表1 实验电路参数Tab.1 Experimental circuit parameters

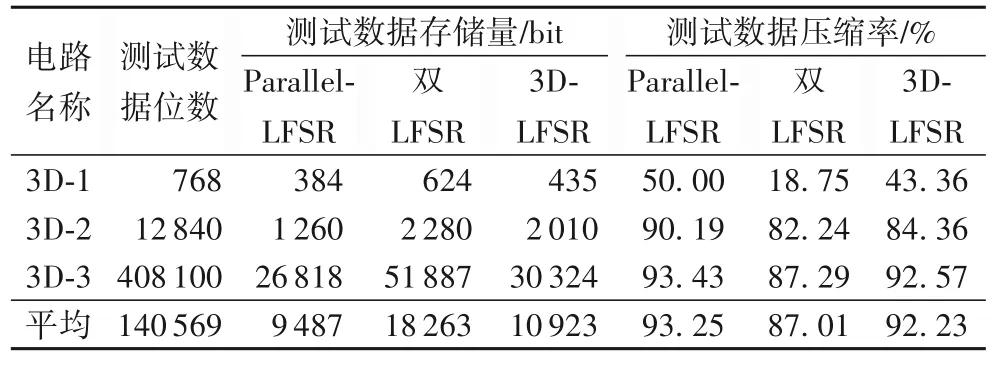

测试数据压缩结果如表2 所示,主要由测试数据二进制位数、测试数据存储量以及测试数据压缩率组成。相较于Parallel-LFSR,3D-LFSR 的平均测试数据存储量增加了15.14%,平均测试数据压缩率降低了1.09%。造成测试数据量增加以及测试数据压缩率降低的主要原因是3D-LFSR中加入了低功耗路由模块,增加了较多的控制信号。相较于双LFSR,3D-LFSR 的平均测试数据存储量降低40.19%,平均测试数据压缩率提升了6.00%。可以看出,相较于双LFSR,3D-LFSR 的测试数据压缩效果明显。

表2 测试数据压缩实验结果Tab.2 Experiment results of test data compression

对于测试功耗,本文主要针对测试过程中的移位功耗。文献[19]提出用测试模式在扫描单元中的翻转次数度量移位功耗,称为加权跳变度量(Weighted Transition Metric,WTM)。设Vi=(bi1,bi2,…,bil)是移入扫描链的第i条测试模式,WTM 定义如下:

有N条测试模式的测试集的峰值功耗如下:

平均移入功耗如式(7)所示:

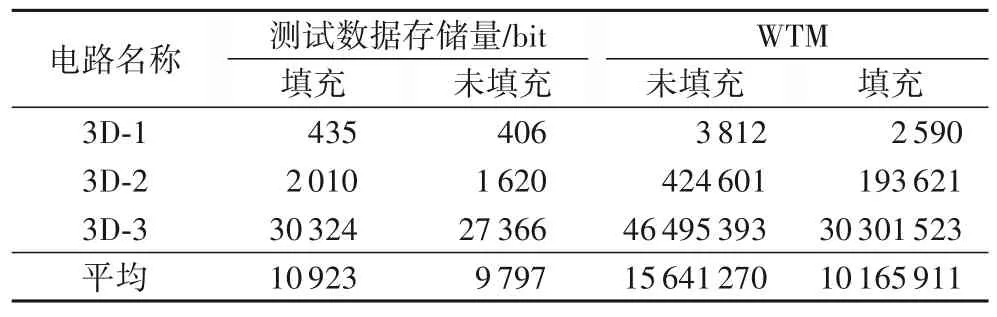

在测试集处理阶段,在不增加面积开销的前提下,无关位的填充能够影响测试数据存储量和测试功耗。表3 是测试集处理中是否进行无关位填充的测试数据结果。本文的无关位填充指在不增加LFSR 级数的情况下进行最大限度的填充。可以看到,填充后的平均测试数据存储量相较于未填充的平均测试数据存储量增加了11.49%。填充后的平均WTM 相较于未填充降低了35.00%。实验结果表明,在增加少量测试数据存储量的情况下,相较于不填充无关位,无关位填充对测试功耗的改善更明显,本文在与其他结构的实验对比中,采用了填充无关位后的测试数据。

表3 无关位填充与未填充的对比结果Tab.3 Comparison results of filled and unfilled irrelevant bits

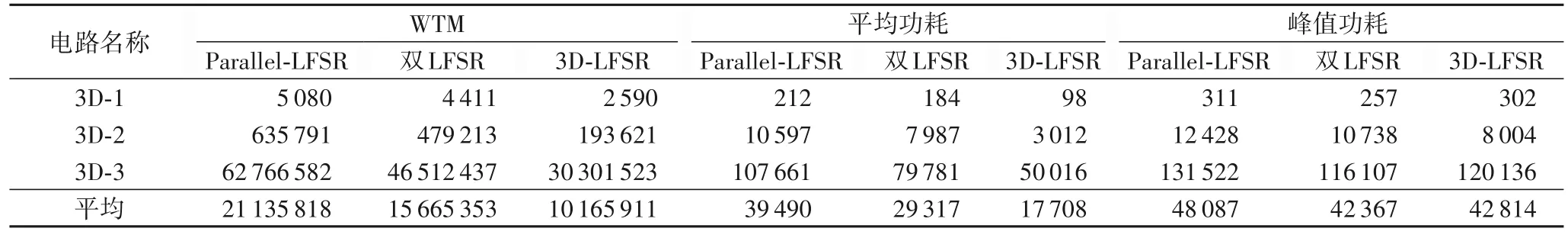

测试功耗结果如表4 所示。3D-LFSR 的WTM 和平均功耗均低于对比的测试结构。相较于Parallel-LFSR 和双LFSR,3D-LFSR 的平均WTM 分别降低了51.90%和35.11%;平均功耗分别降低了55.16%和39.60%。3D-LFSR 的峰值功耗略高于双LFSR,而峰值功耗只要满足低于电路可接受阈值即可。实验结果表明,3D-LFSR 结构在降低测试功耗上效果明显。

表4 测试功耗实验结果Tab.4 Experimental results of test power consumption

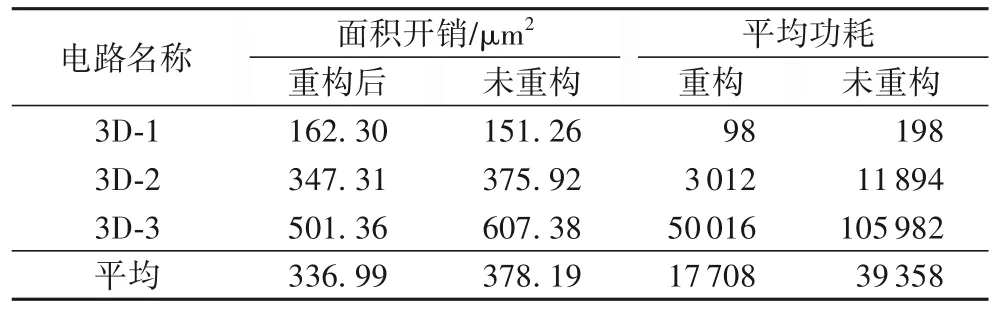

本文使用45 nm 标准库计算面积开销,通过计算测试模式在扫描链中的周期数以得到测试时间。本文中的面积开销只考虑测试结构的开销,不考虑待测试电路以及核间标准结构的面积开销。如表5 所示,相较于Parallel-LFSR 和双LFSR,3D-LFSR 的平均测试面积分别下降了2.07% 和21.31%。实验结果表明,重构后的3D-LFSR 结构在降低测试面积开销上效果明显。测试时间的对比主要针对混合测试和串行测试,为了不增加额外的测试带宽,并不涉及完全并行测试的对比,在不增加的带宽的前提下采用串行和并行的混合测试模式。实验结果表明,相较于串行测试,混合测试下的测试时间更短,平均测试时间减小了20.49%。

表5 测试面积与测试时间开销Tab.5 Test area and test time overhead

表6 是测试结构是否复用重构的对比结果。实验结果表明,相较于未重构,复用重构后的平均面积开销降低了10.89%。为进一步降低测试功耗,复用重构后的测试结构中包括了低功耗路由模块。复用重构后的平均功耗开销相较于未重构后降低了55.01%。

表6 重构与未重构的实验结果对比Tab.6 Comparison of experimental results of reconstructed and unreconstructed structures

5 结语

针对目前三维堆叠集成电路测试中测试成本较高的问题,本文考虑测试成本中的测试资源、测试功耗以及测试时间,提出了一种低成本三维堆叠集成电路测试方案。测试方案中基于LFSR 设计了一种能够较好地适用于三维堆叠集成电路测试的3D-LFSR 测试结构,该结构在绑定后测试阶段能够充分复用绑定前的测试资源,降低了测试资源开销。此外,在测试结构中加入低功耗模块,并结合串行和并行测试的混合测试方法,在仅增加少量测试面积开销的前提下,降低了测试功耗和测试时间。实验结果表明,本文方案能够有效地降低测试成本。未来的工作中,将结合三维堆叠集成电路中的TSV 测试开展进一步研究。