一种小体积X波段频率合成器设计

胡 蓓,王 韬

一种小体积X波段频率合成器设计

胡 蓓,王 韬

(中国电子科技集团公司第二十研究所,西安 710068)

介绍了一种小体积频率合成器的设计,该频率合成器通过直接数字频率合成器(DDS)产生线性调频信号,通过锁相环产生固定二本振信号,通过锁相环(PLL)与2倍频器产生一本振信号,通过变频部分完成二次混频产生射频激励信号。同时采用现场可编程门阵列(FPGA)完成DDS控制以及与系统通讯,电源控制部分产生各种电源。

频率合成器;锁相环;直接数字频率合成器;本振;变频

0 引言

随着微波元器件体积的不断减小,频率合成器的体积也在不断减小,在设计上更加紧凑[1]。本文介绍一种小体积X波段频率源[2]的实现。

1 主要功能

产生Ku波段跳频一本振信号(1路输出);

产生C波段二本振信,单点频连续波(1路输出);

产生X波段跳频发射激励信号(1路输出);

产生X波段跳频检测信号(1路输出);

产生S波段单点频连续波参考信号(1路输出);

产生1 GHz高时钟连续波信号(1路输出);

产生50 MHz连续波低时钟(4路输出);

故障检测设置6个故障检测点:一本振、二本振、发射激励、高时钟、低时钟、直接数字频率合成器(Direct Digital Synthesizer,DDS)中频,在检测到输出功率小于正常值,检测电路报故障。高电平正常,低电平报故障。

2 组成及工作原理

2.1 组成

小体积X波段频率合成器由6部分主要功能电路组成[3]:DDS产生、现场可编程门阵列(Field-Programmable Gate Array,FPGA)控制及电源部分、一本振产生部分、二本振产生部分、X波段上变频部分和高低时钟产生部分。

2.2 工作原理

50 MHz晶振作为时钟基准送高低时钟产生电路,高低时钟产生电路产生4路低时钟信号、1路高时钟信号和1路参考信号。4路低时钟信号其中3路送给内部FPGA、一本振产生电路和二本振产生电路,1路输出;1路参考时钟送DDS中频产生电路;1路高时钟信号输出;

一本振产生电路产生Ku波段一本振信号;二本振产生电路产生C波段二本振信号;DDS产生电路产生中频信号;X波段上变频模块完成两次上变频,产生发射激励信号和检测信号。

FPGA控制及电源部分产生DDS需要的各种控制信号与显控的通讯、故障检测。电源转换部分完成电源的转换及滤波处理。

小体积X波段频率合成器的原理框图如图1 所示。

图1 小体积X波段频率合成器原理框图

3 主要部分详细设计

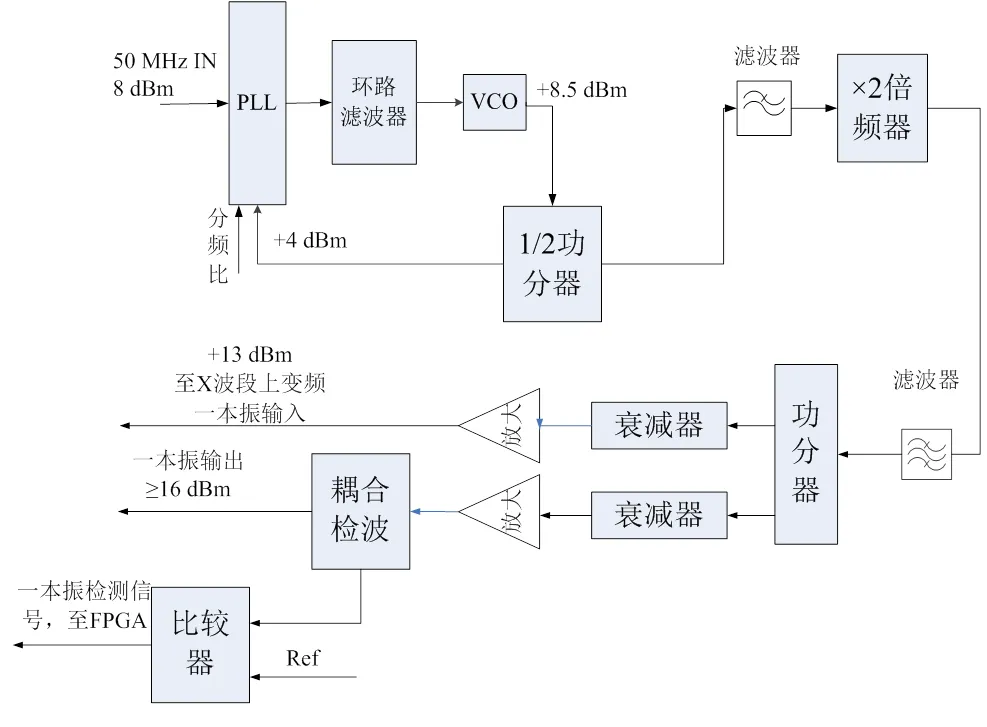

3.1 一本振产生电路

一本振频率源由低相噪锁相环[4]、2倍频器、滤波及放大等电路组成。低相噪锁相环输出的信号经过倍频后得到Ku波段的一本振频率信号,再经过滤波、放大和功分后,一路送到X波段上变频器作一本振,另一路经过耦合器,直通端作为一本振输出信号,耦合端送检波器检波,送比较器与基准进行比较,送出一本振故障报警信号。一本振产生电路原理框图如图2所示。

图2 一本振产生电路原理框图

压控振荡器(Voltage Controlled Oscillator,VCO)输出的相位噪声[5]在6.5 GHz如图3所示。6.5~7 GHz相位噪声的指标差不多都在-110 dBc/Hz@100 kHz。经倍频器相噪恶化3 dB,最终输出一本振输出相位噪声在-107 dBc/Hz@ 100 kHz左右。

图3 VCO输出的相位噪声(6.5 GHz)

3.2 二本振产生电路

二本振产生电路[6]由集成锁相环、滤波器、放大器、功分、耦合检波器、比较起等组成。输入的 50 MHz基准信号经集成锁相环LTC6946IUFD-2产生C波段固定点频,经放大送1分2功分器分成两路,一路直接放大,滤波送X波段上变频;另一路受消隐脉冲控制输出给耦合器,直通端产生输出二本振信号,耦合端送检波器,检测二本振功率值送比较器进行故障报警。二本振产生电路原理框图如图4所示。

图4 二本振产生电路原理框图

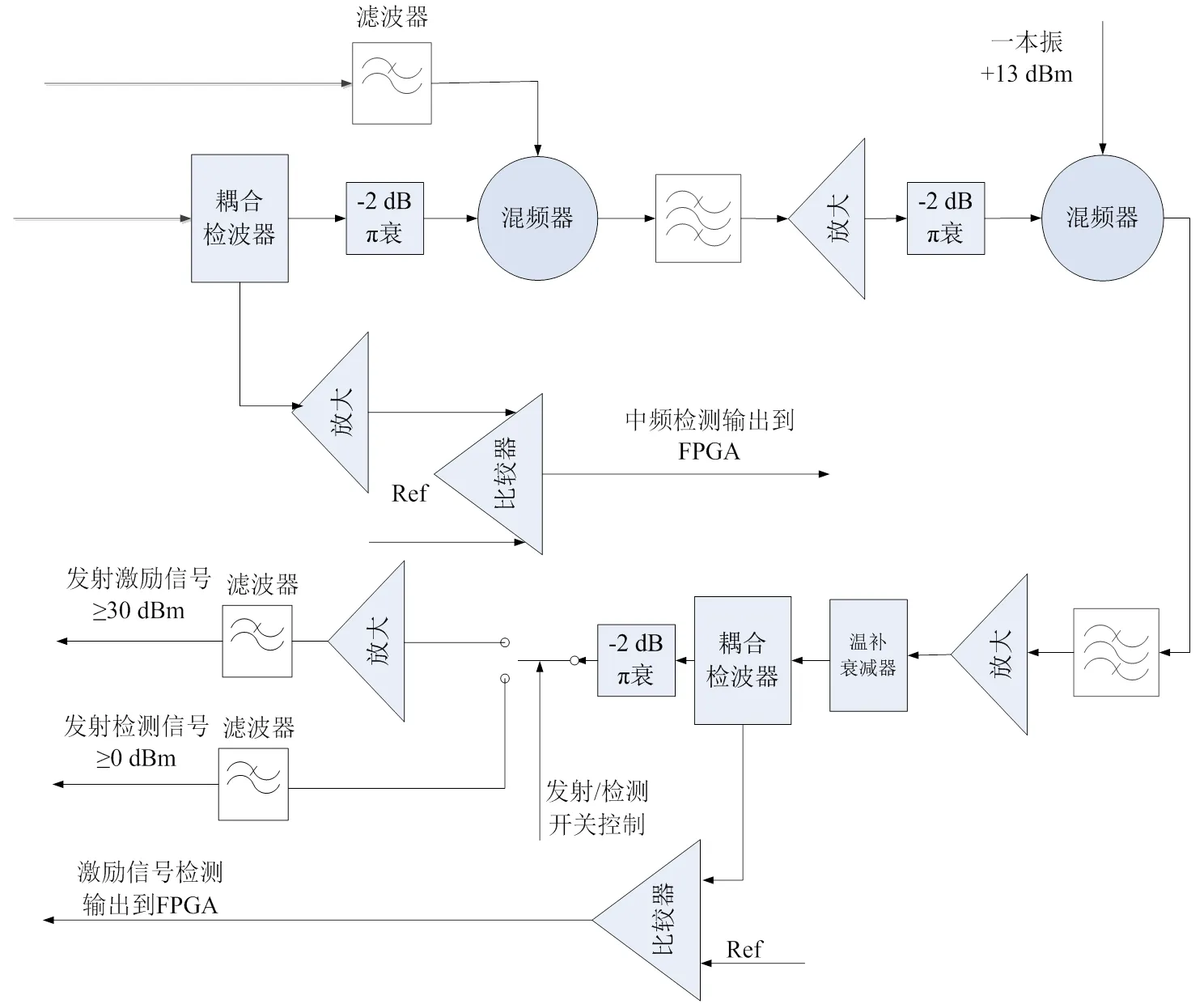

3.3 X波段上变频电路

中频信号送耦合器,耦合端经检波器和比较器,输出中频故障检测信号;直通端送混频器与二本振信号进行一次混频产生高中频信号[7]。经带通、低通滤波器、放大器送混频器与一本振信号进行二次混频[5],经滤波器产生X波段的射频信号[8]。再经耦合器,直通端输出射频信号或检测信号,耦合端经检波器检测输出功率送比较器,产生射频故障检测信号。产生射频激励信号还是检测信号由发射/检测开关控制。X波段上变频电路原理框图如图5所示。

图5 X波段上变频电路原理框图

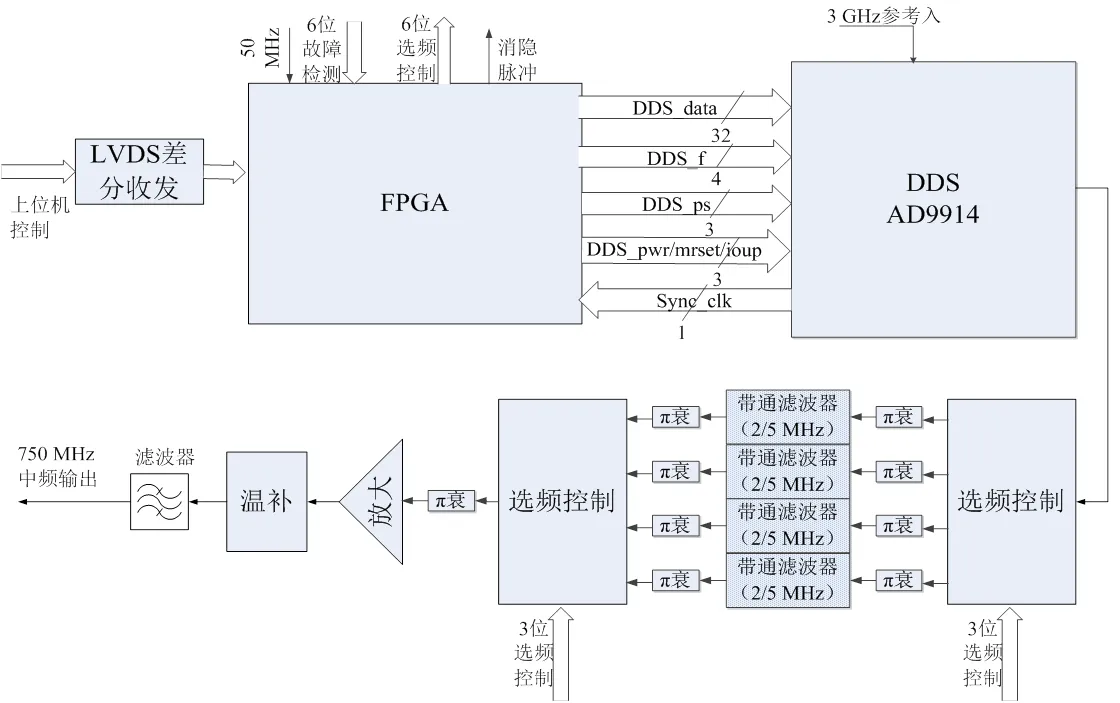

3.4 DDS产生、FPGA控制电路

上位机控制脉冲和指令通过低电压差分信号(Low Voltage Different Signaling,LVDS)差分收发器送入FPGA,FPGA通过串口通讯接收指令和回传状态信息;根据接收到的控制指令,FPGA产生DDS需要的各种控制信号[9-10],DDS产生指定带宽和脉宽的各种频率信号,通过选通开关,对不同带宽的线性调频信号分别送入不同的滤波器进行滤波,最后再经过选通开关合成一路,再经衰减、放大后输出中频线性调频信号。DDS产生、FPGA控制电路原理框图如图6所示。

图6 DDS产生、FPGA控制电路原理框图

4 测试结果

4.1 一本振信号

1)输出频率为Ku波段跳频,步进100 MHz;

2)输出功率≥16 dBm;

3)相位噪声≤-95 dBc/Hz@1 kHz;

≤-100 dBc/Hz@10 kHz;

≤-102 dBc/Hz@100 kHz;

4)带内杂散≤-60 dBc(工作频带);

5)带外杂散≤-60 dBc(9.2~18 GHz);

6)谐波抑制≤-40 dBc;

7)跳频时间≤1 ms。

4.2 二本振信号

1)输出频率为C波段连续波单点频;

2)输出功率≥16 dBm;

3)杂散抑制100 MHz频域内:≤-60 dBc;

4)二次谐波≤-60 dBc;

5)输出路数为1路;(受消隐脉冲控制);

6)相位噪声≤-98 dBc/Hz@1 kHz;

≤-103 dBc/Hz@10 kHz;

≤-105 dBc/Hz@100 kHz。

4.3 发射激励信号

1)输出频率为X波段,步进100 MHz;

2)输出功率≥30 dBm;

3)相位噪声≤-92 dBc/Hz@1 kHz;

≤-97 dBc/Hz@10 kHz;

≤-100 dBc/Hz@100 kHz;

4)带内杂散≤-60 dBc (工作频带内);

5)谐波抑制≤-40 dBc;

6)输出信号形式为线性调频。

4.4 检测信号

1)输出功率≥0 dBm;

2)其余指标同4.3发射激励信号;

3)与发射信号隔离度≥65 dBc。

4.5 参考信号

1)输出频率为S波段,单点频连续波;

2)输出功率≥10 dBm;

3)杂散抑制≥70 dBc(±200 MHz)。

4.6 高时钟

1)输出频率为1 GHz正弦波;

2)输出功率10 dBm±1 dB;

3)杂散抑制70 dBc(±100 MHz);

4)输出路数为1路。

4.7 低时钟

1)输出频率为50 MHz;

2)输出功率≥10 dBm;

3)杂散抑制≥70 dBc(±10 MHz);

4)输出路数4路。

4.8 故障检测

有6个故障检测点:一本振、二本振、发射激励、高时钟、低时钟和中频,在检测到输出功率小于正常值,检测电路报故障。高电平正常,低电平报故障。

4.9 体积

≤260 mm×87 mm×32 mm。

5 结语

通过上述设计,完成小体积X波段频率合成器生产交付,经历各项整机试验,目前使用良好。

[1] 迟忠军,徐云,常飞. 频率合成技术发展概述[J]. 现代科学仪器,2006,3:21-28.

[2] 白居宪. 低噪声频率合成器[M]. 西安:西安交通大学出版社,1995.

[3] V.Manassewitsch. 频率合成原理与设计[M]. 何松柏译,北京:电子工业出版社,2012.

[4] 远坂俊昭. 锁相环(PLL)电路设计与应用[M]. 何希才译,北京:科学出版社,2004.

[5] 王福昌,鲁昆生. 锁相技术[M]. 武汉:华中科技大学出版社,1997.

[6] U.L.Rohde. Microwave and wireless synthesizers[M]. New York:John Wiley & Sons Inc,1997.

[7] Yaping Li,Shuangna Zhang,Nengjie Yu. Advantages and Application of Beidou Dual Frequency Receiver[J]. Technology Progress,2014(7):39-42.

[8] 张玉兴. DDS高稳高纯频谱频率源技术[J]. 系统工程与电子技术,1997,12.

[9] Haigang Yang,Jia Zhang,Jiabin Sun,et al. Review of advanced FPGA architectures and technologies[J]. Journal of Electronics(China),2014,5:371-393.

[10] 潘志浪. 基于FPGA的DDS信号源的设计[D]. 武汉:武汉理工大学,2007.

Small-Volume X-band Frequency Synthesizer Design

HU Bei, WANG Tao

The design of a small volume frequency synthesizer that generates linear frequency modulation signal through Direct Digital Synthesizer (DDS) is introduced, fixed second local oscillator signal through the Phase-Locking Loop (PLL) and generates a local oscillator signal through the phase-locked loop and frequency doubler is produced. At the same time, Field-Programmable Gate Array (FPGA) is used to complete DDS control and communication with the system, and the power control part generates various power sources.

Frequency Synthesizer, Phase-Locking Loop; Direct Digital Synthesizer; Local Oscillator; Frequency Transformer

TN957

A

1674-7976-(2023)-06-451-04

2023-10-09。

胡蓓(1971.08—),浙江杭州人,研究员,主要研究方向为射频。