基于FPGA 的WIM 压电式车辆动态称重信号采集系统的设计∗

陈 建,于殿泓,张祖漪,柳禹朴,杨 芳

(西安理工大学机械与精密仪器工程学院,陕西 西安 710048)

随着我国公路交通运输业的快速发展,运输车辆超限超载现象愈加普遍,这严重影响了公路桥梁的寿命,也给交通安全带来了巨大危害[1]。车辆动态称重系统的发展不仅可有效治理车辆超限超载,并且随着动态称重技术的不断提高,将逐步取代传统的人工及静态称重收费模式[2-4]。目前,称重精度差仍是制约动态称重系统发展的主要因素。影响动态称重精度的主要因素是测得的轴重信号中混有许多干扰信号,包括车速、车辆振动、轮胎驱动力、路面激励以及系统自身产生的测量干扰等[5]。因此,为了高效和精确地获取动态称重的原始信号,信号采集则显得尤为重要。近年来,现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)芯片由于其内部逻辑电路独特的可编程性,有效降低了研发成本,被广泛用作数据采集的控制芯片[6-8]。FPGA 片上资源不受固化模块的占用,可被各个功能模块调用,灵活性高。

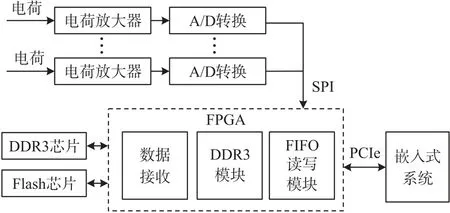

因此,本文设计了一种基于FPGA 的WIM 压电式车辆动态称重信号采集系统,其电路部分主要由16 路电荷放大器模块、16 路AD 采集模块、1 个FPGA 芯片和2 个2 G 的DDR3 存储芯片组成。研究中,通过时序设计,可以同时控制16 路AD 采集模块的信号采集,并将采集信号存储至DDR3 中,之后通过PCIe 总线将数据传输至上位机系统。该信号采集板卡采用分辨率为16 位,采样速率为1 MSPS 的AD 转换器,可实现车辆以0 到120 km/h时速通过动态称重传感器时,输出信号为0~5V 的电压信号。

1 压电式车辆动态称重检测原理

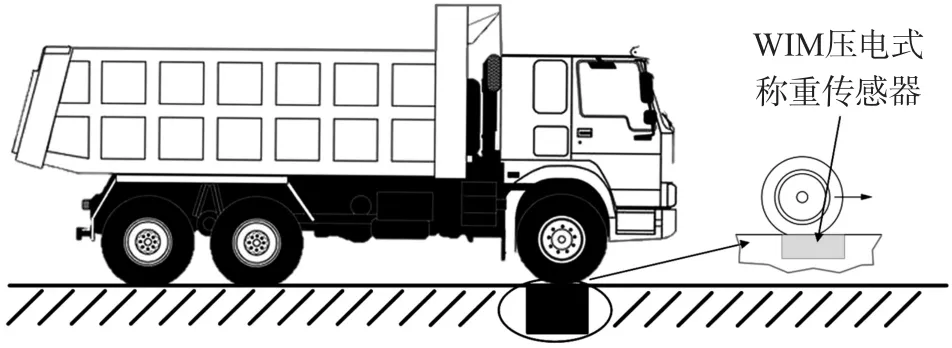

WIM 压电式车辆动态称重主要是通过将动态称重传感器嵌入安装在公路路面,使传感器的承载表面与公路路面在同一平面上,传感器安装示意图如图1 所示。

图1 压电式车辆动态称重检测原理

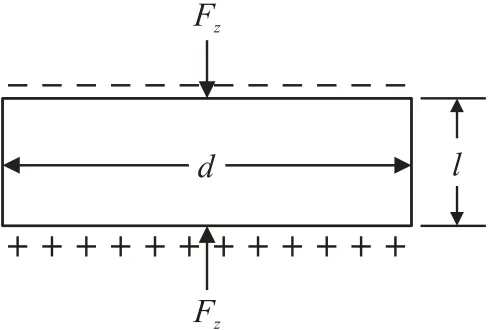

WIM 压电式车辆称重传感器主要由石英晶体组成,石英晶体具有压电效应,作用在石英晶体上的应力可使其产生电荷[9-11]。如图2 所示,当压电表面受到正压力或拉力时,传感器上下表面产生电压差。

图2 石英晶体受力图分析

当车轮在传感器上滚动时,它将在轮胎和传感器之间产生水平、垂直和横向力,由于采用了特殊的传感器设计,仅需要测量垂直力(FZ),道路和传感器之间的横向和水平侧向力(FX和FY)通过传感器周围的特殊弹性材料解耦,不会对称重系统产生影响[12]。当对传感器中的石英晶体施加垂直力时,压电石英盘将产生与施加的垂直力FZ成比例的电荷信号,电荷信号经过电荷放大器转换成精确的比例电压,根据WIM 压电式车辆称重传感器的计算方式即可得到车辆单轴经过时的重量,对所有轴重量求和即可得到车辆的实际负载重量[13]。图3 所示为车辆通过车辆碾压石英称重传感器后,经电荷放大器转换得到的电压信号。

图3 压电信号示意图

图3 为单轴输出的有效波形示意图,其中u(t)为车轮行驶通过传感器,经过转换得到的电压信号;r(t)为经验阈值;t1-Δt1、t2+Δt2为波形起始和结束时刻;t1、t2为阈值所截取的波形有效的起始和结束时刻。

通过经验阈值,得到有效波形的起始和结束时间信息,对有效波形做如式(1)的计算,得到单轴的轴重信息。

式中:W为轴重;V为车速;L为传感器宽度;S为波形的面积,由t1-Δt1时刻到t2+Δt2时刻的波形做面积积分所得;C为标定常数。

汽车的总重量等于汽车各个轴的重量之和,即:

式中:W_SUM 为车辆总重量,n为车辆的轴数,Wi为单个轴重量。

2 动态称重信号采集系统设计

2.1 采集系统总体架构

本文所研究的动态称重信号采集系统的结构如图4 所示,主要由电荷放大器、A/D 转换电路、FPGA控制模块组成。

图4 信号采集系统结构框图

电荷放大器主要由电荷放大电路和低通滤波器电路组成,将压电传感器输出的电荷信号转换为1 V~5 V 的电压信号,以满足A/D 输入端的输入范围。A/D 转换电路主要包括由16 路单端转差分电路和A/D 转换器组成,单端转差分电路主要起到增强信号的抗共模干扰能力。

FPGA 控制电路由FPGA 芯片、2 片DDR3 和Flash 芯片构成。其核心芯片选用Xilinx 的Artix-7系列,型号为xc7a35tfgg484pkg;主控板的时钟频率为100 MHz。DDR3 芯片(型号为:MT41J128M16JT-125)和Flash 芯片(型号为:W25Q128FVSSIG)作为存储芯片与FPGA 相应管脚连接。其中,单片DDR3 芯片有2 G 的存储量,用于临时存储采集的数据。Flash芯片用来存储编写的控制程序,确保FPGA 芯片启动时,能够正常加载芯片代码,完成FPGA 内部控制电路的设计。

FPGA 通过PCIe 总线实现与上位机系统的信号传输,上位机硬件系统搭载有嵌入式操作系统,负责运行系统程序,完成信号采集的控制和管理;同时,搭载了自主研发的数据处理软件,完成汽车动态称重多通道数据采集、分析和上报。

2.2 电荷放大器硬件电路

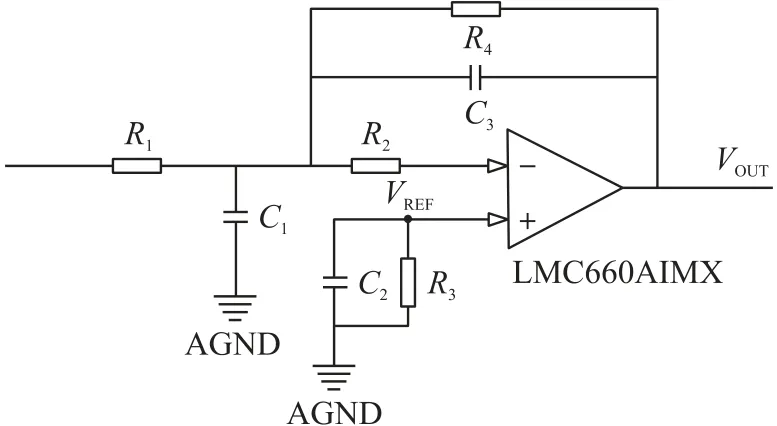

电荷放大器主要由电荷放大电路和二阶有源低通滤波电路组成。WIM 压电石英晶体具备压电效应,当车辆驶过时,传感器受到外力作用,会产生相应的电荷,需要相关的处理电路将电荷信号放大,转换为MCU可识别的模拟信号。信号采集板采用LMC660 芯片设计电荷放大电路,硬件电路如图5 所示。

图5 电荷放大电路

该放大电路的同向输入端接偏置电压VREF,反向输入端接入传感器信号输出端。经过放大电路将电荷转化为电压VOUT,VOUT通过反馈电容C3和电荷量Q得到,计算公式如式(3)所示:

电荷放大电路将与力有关的电荷输入转换并放大为与力有关的电压输出,电荷放大电路的范围通常为6 000 pC/5 V。采集板采用LMC660 芯片设计的放大电路,当压电传感器受到力作用时,该传感器会获得电荷q=d×F,其中d(单位为库仑/牛顿,C/N)为压电传感器晶体电荷对力的灵敏度。因此,压电石英晶体称重传感器的稳定状态电荷灵敏度SF=Δq/ΔF(单位为pC/N)。如果将压电称重传感器与带反馈电容C3的电荷放大器配合使用,则电容C3上因电荷Δq而形成的电压为ΔV=Δq/C3。对应的稳定状态电压灵敏度为:

则电荷放大器的输出电压为:

图中电阻R4(晶体传感器为10 GΩ 至10 TΩ)为运算放大器提供直流反馈,并提供输入偏置电流。对于测得的最小频率,该电阻必须尽量小,并决定着频率输入范围的最低限值。在低频下,转折频率fCL约为:

将一个电阻R1(1 kΩ 至10 kΩ)与运算放大器反向输入端串联,有助于提高稳定性和限制意外高输入电压导致的输入电流。进一步提高R1会导致高频响应下降。在高频下,R1可以与传感器的阻抗ZS相当(1/ωCs,其中Cs为压电传感器的电容)。高频条件下的转折频率fCH为:

根据本文使用的Kistler 型9195G 石英称重传感器的规格参数,可得到具体应用的电路参数。对于VOUT下的输出电压摆幅±5 V,可利式(3)计算得到C3:

选择R4=10 GΩ 并忽略运算放大器的输入电阻和压电传感器的绝缘电阻,低频条件下的转折频率为:

选择R1=10 kΩ 时,高频条件下的转折频率为:

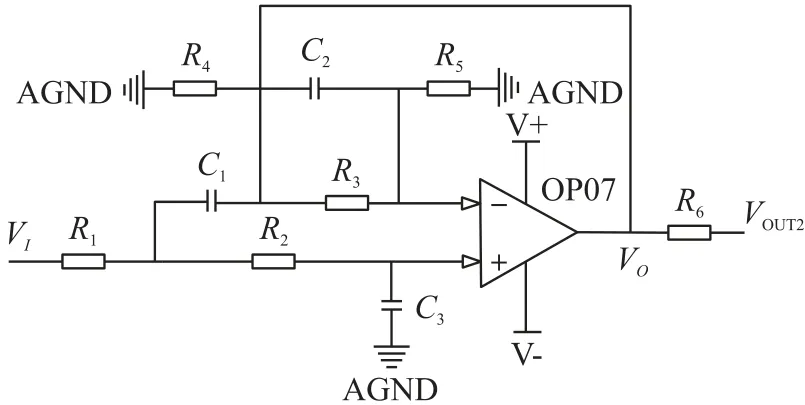

由于WIM 压电式称重传感输出的信号经过电荷放大电路的信号转换后,其输出的直流响应差,且存在一定的干扰。因此根据石英称重传感器的要求,针对输出电压为±5 V 的电荷放大电路,在对转换后的电压信号进行AD 采集之前,需要设置一个具有约500 Hz 的低通截止模拟抗混叠滤波器。同时也考虑到动态称重信号的干扰,因此本文选用OP07D 搭建一个二阶有源低通滤波器,其硬件电路如图6 所示。

图6 二阶有源低通滤波器

传递函数为:H(s)=,其中自然角频率为:ωn=,取R1=R2,则传递函数为:H(s)=则截止频率ωc=,取信号的截止频率为fc=500 Hz 时,则R1=R2=390 kΩ,C1=10 nF。

2.3 A/D 转换电路设计

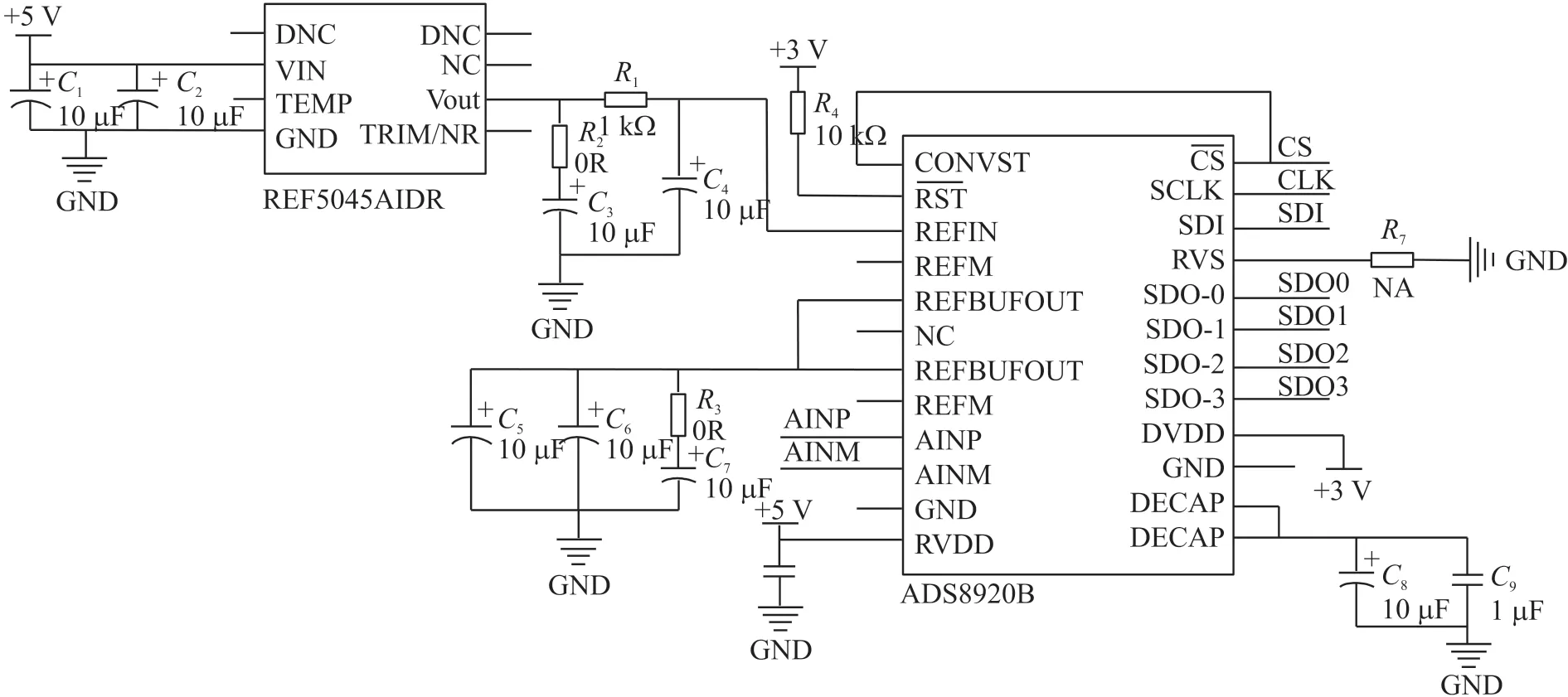

A/D 转换电路主要由电源、单端转差分电路和A/D 转换电路组成。在动态称重系统中,对WIM压电式称重传感器,最小测量点指的是每个有效信号的最小采样点数量。因此,在不丢失信息的情况下为逼近原始力信号,车辆以最高时速120 km/h 通过传感器时,针对宽度为0.04 m 的WIM 压电式称重传感器,有效波形的采样点数不低于200,AD 采样位数需大于等于12 位。故本文A/D 转换芯片采用具有集成式基准缓冲器和增强性能的ADS8920B,ADS8920B 为基于电荷再分配架构的单通道、16 位、采样率为1 MSPS 的逐次逼近型模数转换器。支持单极差分输入,采用增强型SPI 数字接口,接口SCLK 最高可达18 MHz。REF5045AIDR 是一款具有低噪声、低漂移、高精度的电压基准芯片,故采用该电源基准芯片为A/D 转换电路提供干净、精准的参考电压,ADS8920B 硬件电路设计如图7所示。

图7 ADS8920B 硬件电路

由于ADS8920B 为差分信号输入,需要对经过电荷放大器处理后的单极性信号转换差分信号。因此本文选用THS4551 低噪声精密150 MHz 全差分放大器,实现将电荷放大器转换的单极性电压信号转换为差分信号传输至AD 转换器的输入端。硬件电路设计如图8 所示。

3 数据采集系统性能测试

FPGA 数据采集性能测试主要包括DDR3 数据读写测试、PCIe 数据传输测试和ADC 数据采集。将该采集系统在宁夏某公路线上,进行实地测试,现场测试环境如图9 所示,该测试环境为双向单车道加单条辅道,在单车道和辅道前后均安装有两条交错的WIM 压电式称重传感。

图9 现场实验图

3.1 DDR3 数据读写测试

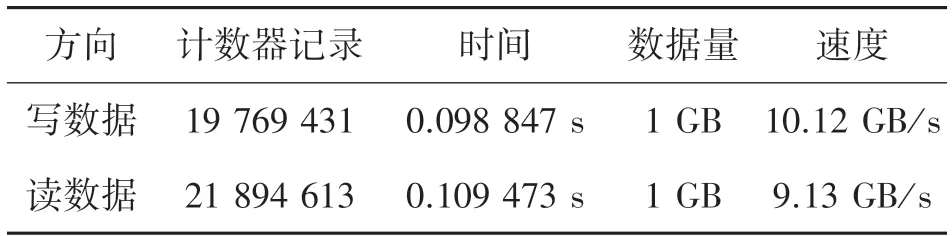

DDR3 数据读写测试主要包括DDR3 读写测试和乒乓读写测试。DDR3 读写测试主要测试数据读写的准确性和数据读写的速度,通过DDR3 读写控制器在顶层模块设置一个定时器,设定一定的时间间隔,通过循环读写,对DDR3 进行数据的读写测试,由定时器对每次读写测试进行计时,来检测DDR3 的读写速度。同时在每次对DDR3 进行数据读写测试时,将写入在DDR3 内部的数据再进行数据读出,以验证读取的数据与写入的数据是否一致,统计读写总次数和错误次数,用于验证DDR3 读写控制器的可靠性。通过实验测试,在计数周期为5 ns 时,写控制器写入1 G 的数据共使用了19 769 431 个时钟周期,读控制器读取写入的1 G 数据共使用了21 894 613 个时钟周期,得到读写速度测试结果如表1 所示。从表中数据可以看出,通过对读写DDR3 的测试,验证了控制器的读写速度均达到设计的高速存取需求。

表1 DDR3 读写测试结果

乒乓读写测试主要实现A、B 两组DDR3 的交叉读写操作,通过该策略来达到数据缓存单元的同时读写功能。缓存模块数据读写的测试方法如下,在250 MHz 时钟域产生128 bit 的顺序数写入ddc2ddr 异步FIFO 中,然后抓取A、B 两组数据读写切换点的时序,通过观察切换点的时序来确定交叉读写是否成功,另外通过模块的输出数据来验证整个缓存模块数据读写的正确性。

3.2 PCIe 数据传输测试

PCIe 接口主要实现FPGA 数据采集卡与x86主板之间的数据通讯。相对于标准编程的数据输入与输出传输,DMA 具有大数据传输时高吞吐量以及占用CPU 更低的优势。因此系统设计时为了提高系统性能选用DMA 传输。根据DMA 控制器的结构,将系统功能模块划分为2 个部分:FPGA 端和PC 端。FPGA 端基于Xilinx LogiCore-PCIe IP Core,实现对数据时序的控制以及PCIe 事务的处理;FPGA 端的主要功能模块包括PCIe IP Core、RX 接收引擎、TX 发送引擎、寄存器及存储读写、接收发送的FIFO 控制模块。PCIe IP Core 用于完成协议层的配置;TX 发送引擎用于实现TLP 数据包的发送和时序管理;RX 接收引擎用于实现TLP 数据包的接收和时序管理;寄存器及存储读写模块用于实现DMA 的操作和寄存器的管控;TX FIFO 接收外界数据并缓存,提交TX 发送引擎进而传输至PC 端;RX FIFO 缓存从PC 端接收到的数据包,等待用户调用。PC 端主要采用WinDriver 生成PCIe 驱动,并利用其自带的API 函数实现数据接收与发送的应用程序设计。

3.3 ADC 数据采集测试

AD 采集模块使用的ADS8920B 芯片,ADS8920B设备支持三种功能状态:RST、ACQ 和CNV。设备状态主要由主机控制器提供的CONVST 和RST 控制信号的状态决定。RST 为复位状态,当主机控制器将RST 引脚拉低并持续一段时间低电平,即进入RST 状态;退出RST 状态需要将RST 引脚拉高,CONVST 和SCLK 保持低电平,CS 保持高电平状态,即进入ACQ 状态;当引脚CONVST 处于上升沿时将ACQ 状态转换到CNV 状态,CNV 状态即可实现AD数据的转换,SPI 在CNV 状态下数据传输帧时序如图10 所示,设备和主机控制器之间的数据传输帧以CS 下降沿和随后CS 的上升沿为界。

图10 ADC 读取时序图

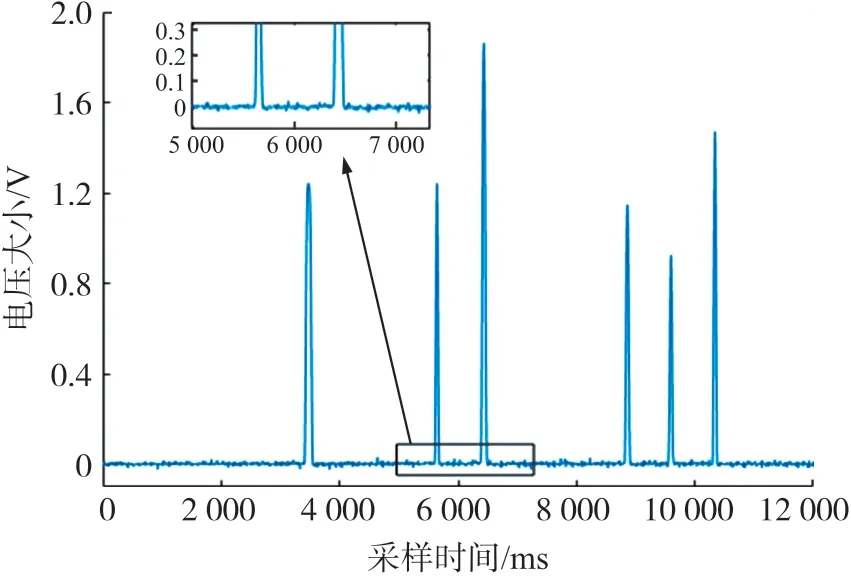

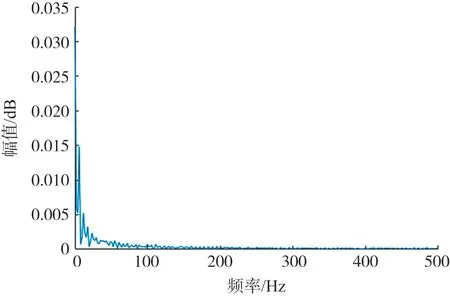

编写 Verilog程序,设置AD采样频率为800 kHz,得到汽车动态称重原始信号波形如图11所示,该信号为六轴车行驶通过WIM 压电式称重传感器得到的信号,图中6 个尖峰分别对应汽车各个轴通过传感器时采集得到的波形。该信号的频谱图如图12 所示,通过原始信号的波形和频谱图可以看出,该信号存在一定的低频噪声干扰,而高频信号的噪声干扰在经过二阶有源低通滤波器得到了改善,主要为低于500 Hz 的噪声干扰,而主要的噪声干扰频段范围在低于50 Hz。因此,后续还需要通过软件算法消除噪声信号对动态称重的精度影响。

图11 动态称重原始信号波形

图12 动态称重原始信号频谱

4 结论

本文为实现多通道汽车动态称重信号采集,设计了一款基于FPGA 的压电式车辆动态称重传感器的多通道高速数据采集系统,该系统可支持16 通道的信号采集,为更好地逼近动态称重的原始信号,采用了16 位、1 MSPS 的AD 转换器,可实现车辆以0到120 km/h 行驶速度通过称重传感器、输出信号为0~5 V 的电压信号采集。对于16 通道的同步数据,本文选用2 个2 G 的DDR3 存储芯片用于实现数据的存储,并通过双DDR3 之间的乒乓操作实现数据的同时传输和存储。上位机系统通过高速PCIe 总线实现与FPGA 的数据传输。经过试验验证,该信号采集系统能够满足所设计的指标要求。