基于深度卷积神经网络的汽车图像分类算法与加速研究

黄佳美,张伟彬,熊官送

(北京自动化控制设备研究所,北京 100074)

0 引 言

随着城市化建设不断发展,我国对交通建设的需求也不断增长,成为了世界上在交通领域基础设施建设方面最快的国家之一,但车辆管控问题、道路交通问题、车辆违章问题等层出不穷,很难做到全面、有效的管理。例如抢占公交专用车道,会造成车辆停站时间较长,市民乘车不方便等问题,更容易导致压车现象出现,进而造成新的交通拥堵。马路上的摄像头每天拍摄下许多汽车照片,如何在大量的图片中筛选出汽车的图片,并且识别出车辆种类,这时车辆识别就显得尤为重要。传统的手动分类方式需要耗费大量的时间和精力,且容易出现主观性误判的情况[1]。而深度学习作为新一代计算模式,近年来在众多领域中发挥了重要作用[2],以卷积神经网络为代表的深度学习算法在计算机视觉处理领域中发挥着巨大的作用,如图像分类、目标检测等具体应用[3-6]。随着近年来智慧交通系统的快速发展,利用深度神经网络区分公交车道上的公共汽车与非法停留的车辆是一个很好的解决途径,能够有效地减少交通堵塞并打击社会车辆在高峰时期非法占用公交车道的行为。

神经网络在PC 端训练完成后需要进行模型部署。模型部署是指把训练好的模型布置在特定环境中运行的过程,可以将神经网络部署在服务器上,通过网络调用进行预测,或者部署在嵌入式设备上,实现嵌入式端数据分析处理。模型部署要解决模型框架兼容性差和部署后模型运行速度慢这两大问题[7]。随着物联网时代的来临和边缘计算的兴起,未来社会的发展趋势是万物互联和万物感知,因此在嵌入式端部署深度学习算法具有重要的现实意义[8-10]。

而神经网络处理单元是应用人工智能的核心组件,决定着神经网络运算的性能和功耗。为了提供更好的运算能效比和满足算法在嵌入式端的应用落地,在现有研究的基础上,本文提出基于FPGA 的嵌入式深度卷积神经网络实现加速,去改进对于模型部署后运行速度慢的问题。与其他研究相比,本文主要做了以下工作:

1)针对现有占用公交专用车道的问题,在开源数据集的基础上提取训练集并加入迁移学习方法进行重新训练,使得训练后的模型参数对公交车分类的精确度更高。

2)对于训练方法,提出基于深度卷积神经网络的图像物体分类算法,采用多精度混合训练方法,根据网络结构特性在特征提取部分采用INT8,线性层分类采用FP32,在保证运算效率的同时降低精度损失。

3)对于在FPGA 部署方案,采用匹配灵活硬件加速结构的软件计算框架,通过高效的调度保证硬件加速器中各个模块能及时连续地工作,从而实现神经网络的高效任务执行。

1 模型选择与分析

残差卷积神经网络能够有效解决因网络深度增加而产生梯度消失的问题。ResNet 是一种深度残差网络,在多个图像分类基准数据集上都取得了优异的性能,实现了高精度的分类。ResNet 系列网络包括ResNet18、ResNet34、ResNet50、ResNet101 等,网络模型数字越大,代表模型越大,所需要的计算量越大。ResNet50 具有精度高、模型小、易于实现等优点[11-12],综合考虑,本文所部署的ResNet 网络采用ResNet50 网络模型。

1.1 数据集处理

在基于深度学习的图像分类方法中,图像被表示为一个张量,其中每个张量都代表一个RGB 图像,各种图像作为label,根据数据分布情况排成与张量数量相等的矩阵表示label,并将输入数据送入深度神经网络训练,学习出最优的分类器模型。

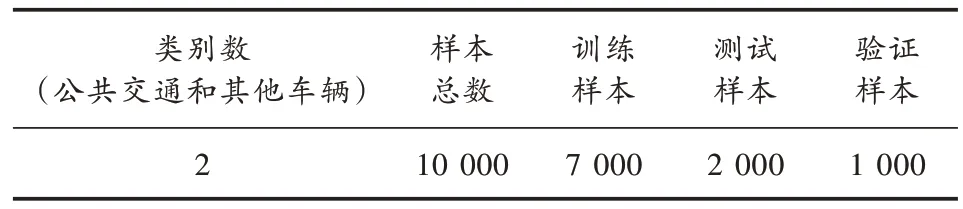

为了实现所需的应用落地,基于开源数据集从中重新抽取了相关图片作为数据集。训练前,对数据进行预处理,包括删除重复项、填补缺失值和去除异常模糊图片等。最终,本文得到了包含约1 万张图片的数据集,用于后续的分析。其中大约70%用于训练,20%用于测试,10%用于验证。本文选取进行目标分类的数据集共包含两类,分别是公交车辆和其他车辆。图片是不同大小的RGB 图像,对数据进行预处理,将像素值统一为224×224 的图片大小,并将图片放到相应分类的文件夹里。目标分类数据集如图1 和表1 所示。

表1 数据集

图1 目标分类数据集部分示例

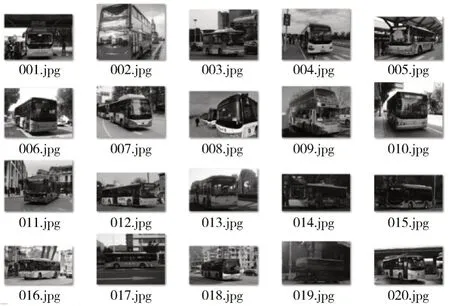

1.2 残差模型

若将输入设为X,将某一有参网络层设为H,那么以X为输入的此层输出将为H(X)。一般的CNN 网络如Alexnet、VGG 等会通过训练直接学习出参数函数H的表达。残差学习则是致力于使用多个有参网络层来学习输入、输出之间的参差,其中X这一部分作为分支直接输入,使得网络的深度更加稳定,而有参网络层要学习的输出H(X)用于计算结果并预测损失值。

残差网络模块如图2 所示。

图2 残差网络模块

ResNet50 采用残差连接的结构,整体模块由卷积层、批次归一化层、特征拼接层、池化、激活函数等组成。ResNet50 共有50 层,模型的输入为224×224 的RGB 图像,经过第一层的卷积、池化运算之后通道数增加到64,图像降维到56×56,进入残差模块之后,经过4 次残差操作图像特征图变为(2 048,7,7)。虽然ResNet50 解决了梯度消失问题,但是依旧存在大模型在嵌入式平台部署后实时性较差的问题。

1.3 样本训练方法

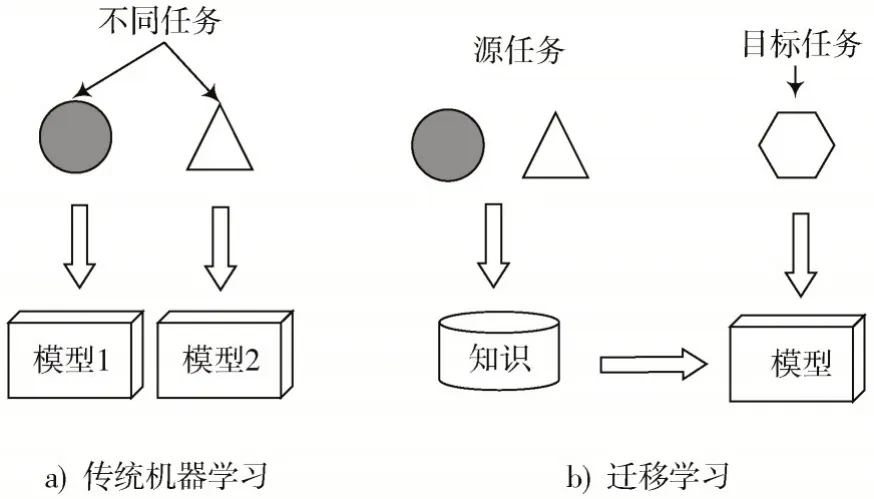

迁移学习是指将在某个领域或任务上学习到的知识和技能应用到新的领域或者任务中,可有效解决深度学习中因为数据集不足而导致网络模型出现过拟合的问题。迁移学习大致可以分为:基于特征的迁移方法、基于共享参数的迁移方法和基于关系的迁移方法[13]。其中,基于共享参数的迁移方法结合了深度学习和迁移学习,通过对包含高质量的标注数据大数据集进行训练,得到预训练模型,在此基础上,采用少量标注数据的小样本数据集进行迁移学习,完成目标分类的任务。本文采用的是基于共享参数的迁移方法。

迁移学习与传统学习对比如图3 所示。

图3 迁移学习与传统学习对比

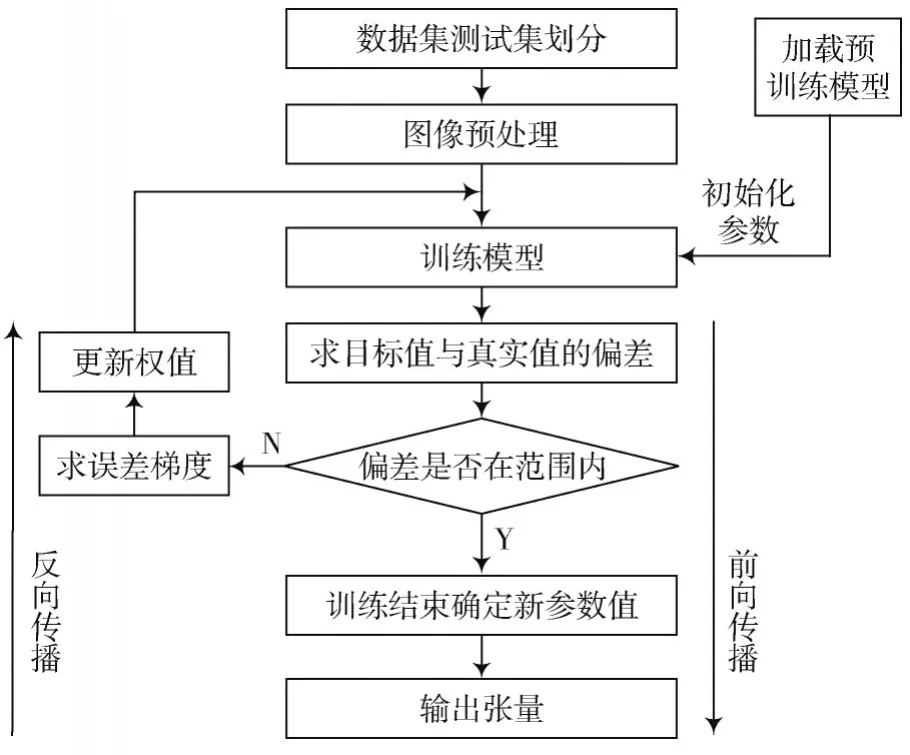

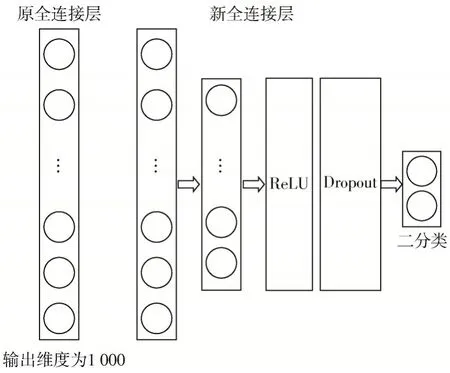

针对小样本数据集及样本数据相似度高的情况,本文方法保留了预训练模型中的卷积层、Bottle-Nect 网络结构以及预训练参数,所保留的网络结构和预训练参数用于提取图像初始特征,另外的全连接层参数则进行重置,并基于小样本数据集进行重新训练。本文对全连接层网络结构进行了改进,模型训练数据处理如图4所示。

图4 模型训练数据处理

图5 全连接层网络结构

式中:ncorrect为被正确分类的图片数量;ntotal为测试集总的图片数量。通常认为Acc 越高代表模型分类效果越好。

2 FPGA 实现方法及设计结果

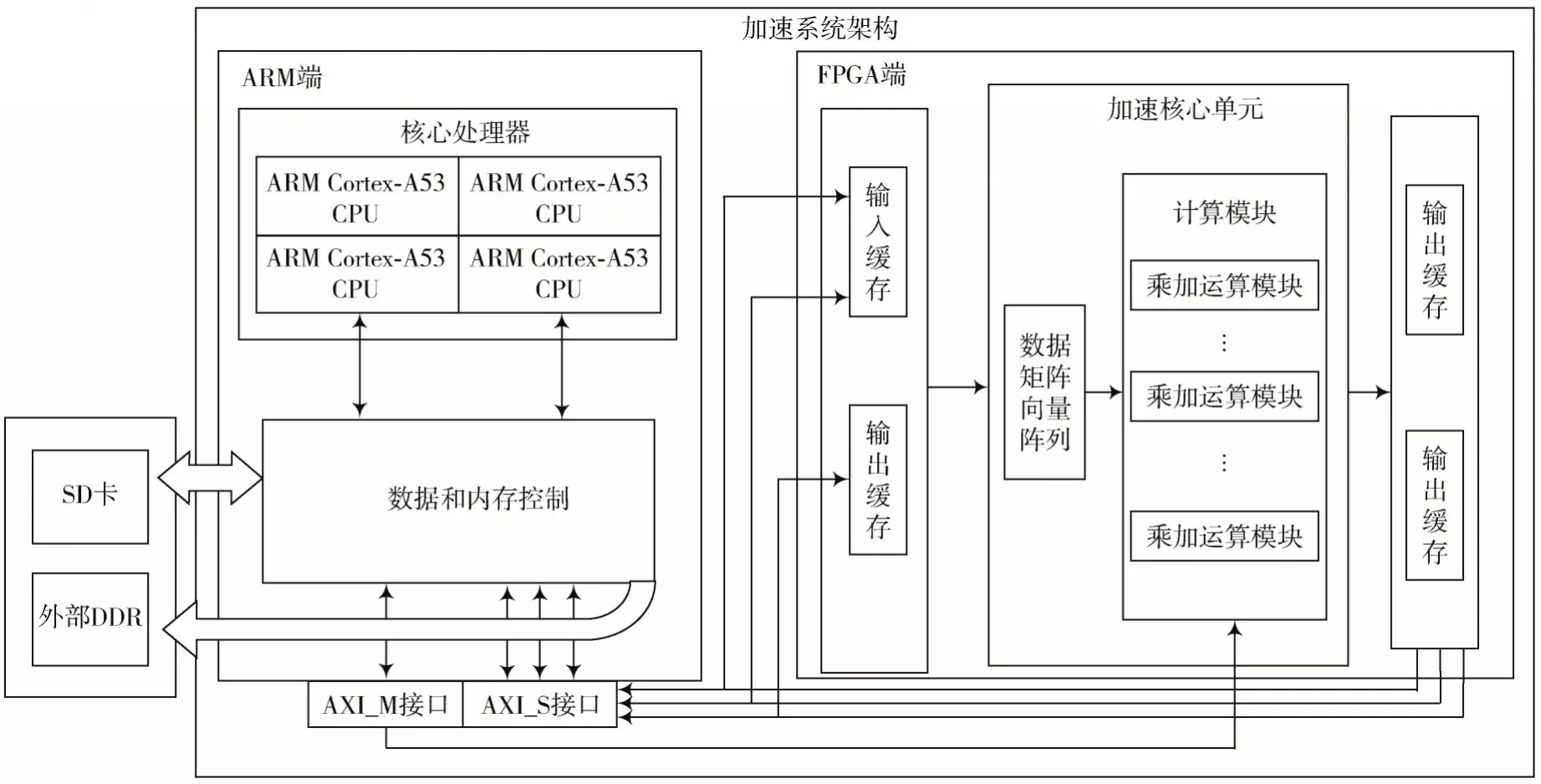

ResNet50 计算加速系统如图6 所示。

图6 加速系统架构

所述系统包括ARM 和FPGA 平台架构、片外存储区、AXI 接口,所述ARM 平台架构包括核心处理器、数据和内存控制器,所述FPGA 平台架构包括加速核心单元、输入缓存端和输出缓存端。使用软核ARM 作为片上系统的主控,控制外设、DMA、CNN 加速器来实现数据调度和操作,为FPGA 设备设计了一个IP,用于卷积加速的应用。

片外存储区包括SD 卡和外部DDR,加速核心单元包括数据矩阵向量阵列和计算模块,缓存区连接数据和内存控制器,数据和内存控制器连接片外存储区,数据和内存控制器连接AXI_M 和AXI_S 接口,输入缓存端连接数据矩阵向量阵列,计算模块连接输出缓存端,使用AXI 接口连接计算模块。根据计算描述生成计算实现的过程,总结如下:

算法: 计算描述与计算实现的映射算法

Input:算法中产生的映射表s,卷积参数描述Ip

Output:硬件算子队列Q

1:根据I,分配该层卷积中所有数据片外存储地址

本文将协同过滤算法用于学生学习结果预测,将学生看作用户,将学生的学习表现看作项目,采用以学生为主体的协同过滤算法,寻找与目标学生距离最近的K个学生,根据这K个学生的学习结果来预测目标学生的学习结果。

2:根据s中的块级映射参数和I,分配每个块级任务中的数据的片上地址

3:进行数据张量与片上内存段的标记

4:fori=0 to IC_C,j=0 to OC_C,k=0 to FM_C do

5:根据s中的细粒度映射参数,分配每个细粒度任务中的片上数据地址

6:进行细粒度任务级别的数据张量标记与片上内存段的标记

7:根据块级任务中的标记与细粒度任务级中的标记,确定依赖信息

8:forl=0 to ic_c,m=0 to oc_c,n=0 to fm_c,p=0 to k_c do

9:根据依赖信息及计算描述和细粒度映射参数,生成硬件元算子队列Q

10:endfor

11:endfor

加速器的工作过程分为数据加载、数据处理和结果输出3 个步骤。在数据加载阶段, 计算所需的所有数据都从片外的动态随机存取存储器传输到片上缓冲区,包括该层的量化后权重、偏置和特征图。CPU 在调用PL端的加速器之前,将这一层的控制信息写入PL 端的控制寄存器,加速器根据这些参数处理数据。每一层的输出结果必须在下一层数据加载前写回DRAM。

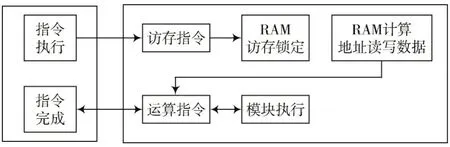

每个模块并行地按序执行指令,不同模块间使用和产生的数据之间存在依赖关系,同时每条指令都需要使用片上存储,同一个单元RAM 在同一时间段内只能被一个模块读、一个模块写,所以不同模块之间的指令执行既需要保证顺序正确,同时也要保证访存不会出现冲突。本设计中使用两种机制来保证指令流和数据流的顺序正确以及访存不会出现冲突,模块虽然并行地按序执行指令,但指令是否执行由每个模块中用于处理依赖和内存请求信息的顶部模块决定,指令的执行需要满足两个条件,依赖检查通过以及请求的内存未被占用。

缓存顺序如图7 所示。

图7 缓存顺序

3 仿真与结果分析

本文实验使用Pytorch 深度学习框架搭建卷积神经网络,采用ResNet50 模型在图像数据集上进行实验。对于所有量化实验,学习率最初设置为0.001,每10 个epoch 衰减一次,衰减系数设置为0.1。将输入图像大小统一调整为224×224 进行训练。

将在Pytorch 下训练好的模型分别部署至CPU 与加速器上进行运算,模型部署至边缘式上需要两个步骤:首先将Pytorch 的.pth 模型转换成ONNX 的.onnx 模型;然后采用人工拆解将.onnx 模型转换算子通过SDK 进行部署。硬件平台选用Xilinx ZU9 开发板(4 核ARM Cortex-A53+FPGA),加速器使用Vivado 设计工具,在Vivado v2018.2中完成综合与布局布线。

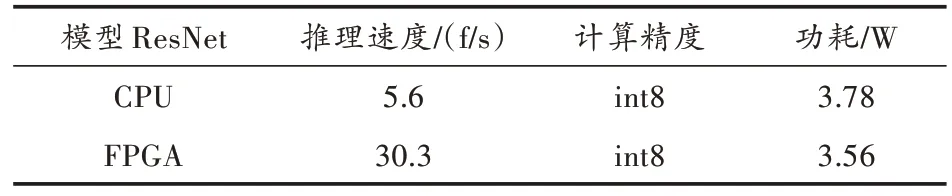

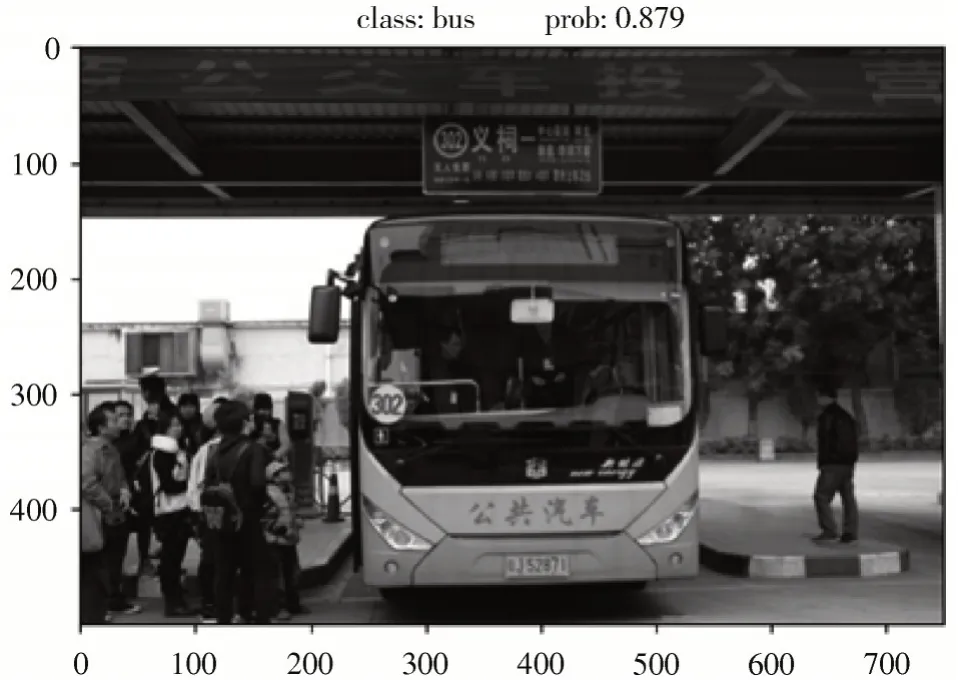

实验结果如图8 和表2 所示。

表2 使用加速器对比

图8 结果图片展示

实验结果表明,在200 MHz 工作频率下,加速器的峰值计算性能达到425.8 GOP/s,推测压缩模型速度达到30.3 f/s,模块功耗为3.56 W,是未使用FPGA 加速的推理速度的5 倍。

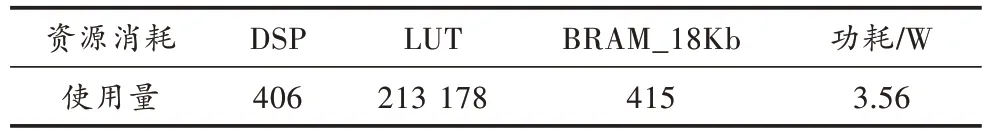

表3 是加速器中各类资源的使用情况。相比其他加速器方案,本文提出的硬件加速架构对FPGA 片上各类资源要求较少。

表3 FPGA 资源消耗与系统功耗

4 结 语

本文采用软硬件协同的方式将深度学习领域中的神经网络模型应用于识别占用公交车道任务中,设计一种基于算子的通用深度卷积神经网络加速器,并在ARM+FPGA 异构平台上成功部署,实现了神经网络推理加速,并利用ARM 核对加速器进行调度,加快了硬件推理速度的同时减少了精度损失,最终完成目标分类任务。

在软件层面,本文利用迁移学习的深度学习方法,构造ResNet50 预训练模型,克服了传统网络每次添加新的样本都需要重新进行大样本训练、训练时间长等缺点;在硬件层面,通过合理设计硬件架构和硬件算子,在保证加速器性能的同时减少了FPGA 资源消耗。该图像物体分类算法为实现神经网络在嵌入式平台的高效、高速应用提供了有效解决方案。

注:本文通讯作者为张伟彬。