一种使用Flash 阵列存储数据的方法研究

翟成瑞,林天鹏,张彦军

(中北大学省部共建动态测试技术国家重点实验室,山西太原 030051)

在航空航天领域装备的不断发展中,Flash 以其体积小,掉电数据不丢失,工作可靠等优点在航空航天设备的研制试验过程中备受欢迎。随着所需存储数据量的增加和存储数据速度的提高,单片Flash 的存储容量和速度已经不能满足要求,如果使用其他大容量存储介质会存在掉电丢失,存储介质体积大,不利于布局,以及部分存储介质存在工作不可靠等缺点[1-2]。因此,针对高速大容量数据存储的要求,对Flash阵列式存储展开了研究,针对Flash工作特性进行了流水线管理,无效块检测等高效使用存储阵列的方法研究。

1 存储阵列

由于Flash 芯片的特性,在数据写入时会有两个基本操作,先是将数据写到页寄存器中,然后再从页寄存器中将数据写入对应地址的Flash 存储页中,这个过程称为页编程[3]。页编程过程是由芯片自主完成的,在一片Flash 进行页编程的时候,此片Flash 不能进行其他操作,要等到完成页编程之后才可以,页编程的时间相对于其他操作时间较长,这对数据存储速度将会产生影响。而在Flash进行自动页编程时是可以进行其他芯片的操作。所以在一个数据记录模块中同时控制多片Flash作为存储载体不仅可以提高存储系统的存储容量,还可以提高数据的存储速度[4]。

1.1 并行排列

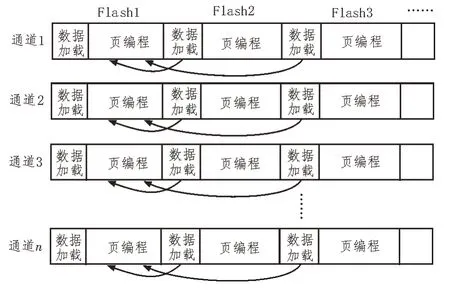

多片Flash 组合方式的不同也将对存储速度产生不同的影响,将Flash 并行排列以后,可以同时对多片Flash 进行存储操作,增加了存储容量[5],在一定程度上数据写入速度也得到了提升,但是并行排列的方式依然存在页编程时间等待,资源浪费等问题,没有充分发挥出组合的优点。并行组合示意图如图1 所示。

图1 并行组合

1.2 串行排列

将Flash 串行排列以后,可以在一片Flash 进行页编程的时候对通道内其他的Flash 操作来进行数据写入,这种排列方式充分利用了在一片Flash 页编程期间自身不能进行其他操作而需要等待的时间,提高了数据存储的速度和资源利用率[6]。但是串行排列的方式不能同时对多片Flash 同时进行数据加载,也没有充分发挥出组合的优点。串行组合示意图如图2 所示。

图2 串行组合

1.3 矩阵式排列

基于上述优缺点,提出了通道间并行排列加通道内串行排列的矩阵式组合方式,在通道间可以同时对多片Flash 进行操作,在通道内,当一片Flash 页编程操作时,可以对其他Flash进行操作。这种组合方式不仅充分利用了FPGA 的逻辑资源,也充分利用了Flash的存储特性进行存储,很大程度上提高了数据存储速度及数据存储容量。该组合示意图如图3所示。

图3 矩阵式组合

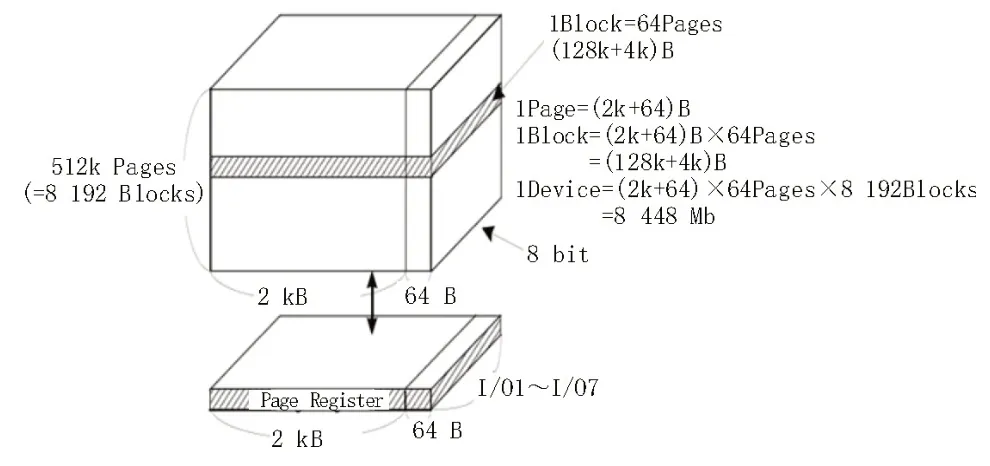

2 流水线管理

Flash 的内部写入数据和读取数据以页为单位,每一页中都包含有数据空间和缓存空间。许多个页组成一个块,数据擦除一般以块为单位[7]。许多个块组合组成一个存储单元。以单片容量为8 Gb的Flash为例将阵列式存储单元与单片存储单元的存储效率做以对比[8]。该Flash 的逻辑结构图如图4 所示。

图4 Flash逻辑结构图

选用的Flash 每页的容量为2 kB,在时钟周期50 MHz,即系统在时钟周期为20 ns 下工作。Flash写入数据的流程为首先写入一个字节的命令加五个字节将要存放数据的地址,然后将数据加载到页寄存器中,最后将页寄存器中的数据加载到Flash 对应的存储单元中,即页编程[9]。

写入指令加地址的时间为t1,一共需要六个时钟周期;查阅数据手册得知地址到数据加载时间需要t2=70 ns;将2 kB 的数据加载到页寄存器中需要的时间为t3,共2 048 个时钟周期;写使能从高状态到忙信号的拉低时间需要t4=100 ns;而自动页编程时间t5平均需要200 μs,最大需要700 μs,以平均页编程时间计算写入一页数据总共需要的时间。该时间为T=t1+t2+t3+t4+t5=241.25 μs。单片Flash 的写入速度为V=2 kB÷241.25 μs=8.1 MB/s。

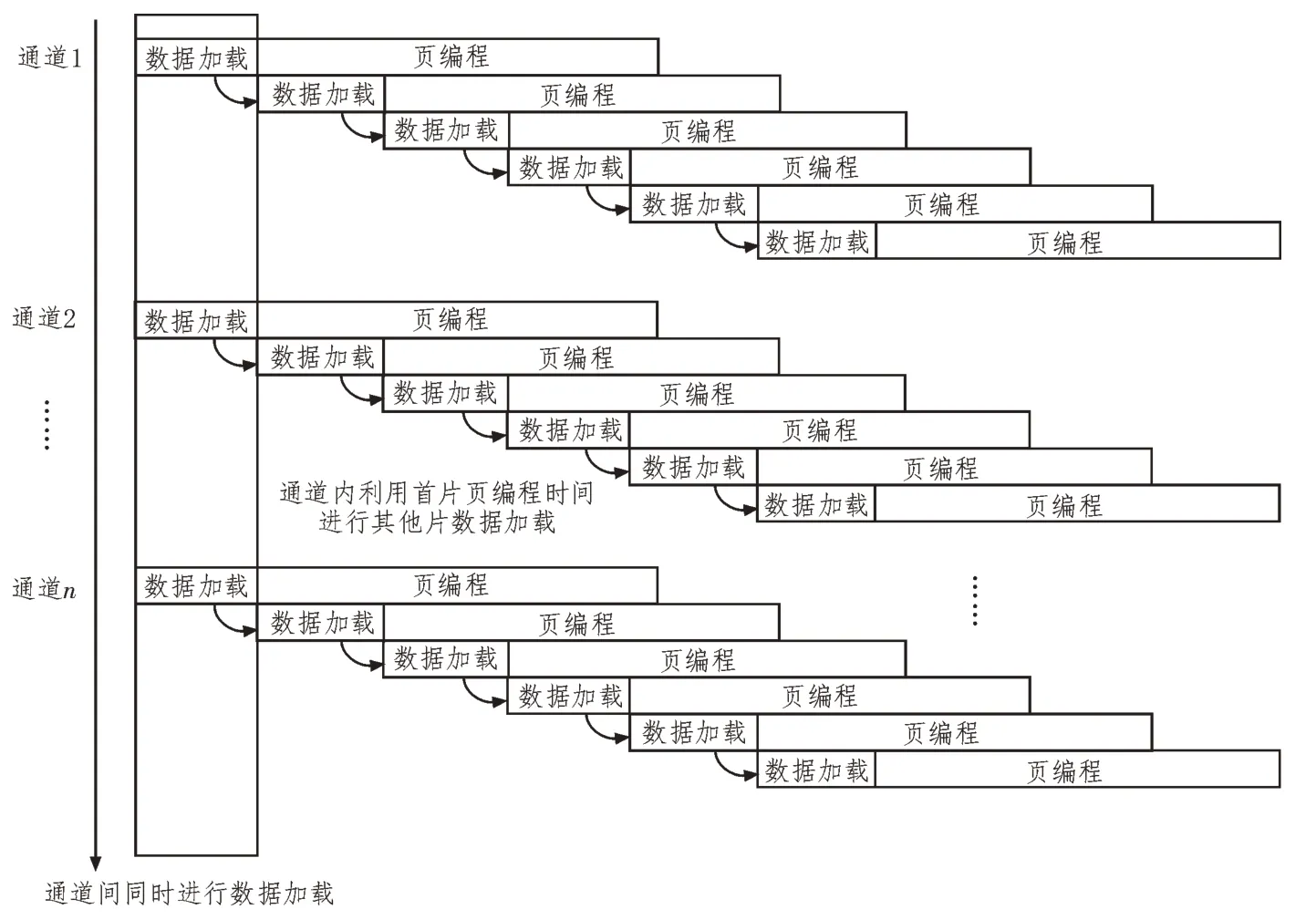

当Flash 组成阵列式存储单元后,通道间可以同时对多片Flash 进行数据加载及页编程,通道内可以在一片Flash 进行自动页编程时对通道内其他的Flash 进行数据加载操作。以此可以大幅提高数据存储速度和存储模块的存储容量[10]。

通道间Flash为独立存在,互不影响,可以同时进行页编程操作,即同时可以将数据写入多个通道的第一片Flash。通道内的Flash只能同时对一个芯片进行页编程。因此在通道内,当数据加载到第一片Flash中的页寄存器中后,利用第一片进行自动页编程的时间可以继续将需要存储的数据缓存到通道内下一片Flash的页寄存器,第一片页编程时间足够对通道内后面的好几片Flash进行数据加载至页寄存器中的操作[11]。

该芯片数据加载到页寄存器的时间为41.25 μs,页编程时间200 μs,第一片进行页编程时,其余几片页加载时间总和大于页编程时间200 μs 就可以对页编程的时间进行充分利用,因此单个通道Flash 大于六片即可。所以单个通道串行排列的数据存储速度最大可以达到V=2 kB÷41.25 μs=47.35 MB/s。单个通道内为了节省资源和便于控制,FPGA 与存储芯片的数据传输接口、命令、地址、读写接口均为公用的传输线,只有片选信号和忙闲信号为单独的传输线。单个通道内串行排列的方式,其最大数据存储速度就是单页的存储容量除以数据加载到页寄存器的时间,这个速度相对于单片Flash的存储速度已经有了很大提升,但是在某些高速数据的存储需求下,该速度还是不能满足要求,所以在通道内串行排列的基础上再进行通道间的并行排列,这可以使数据存储速度比串行排列数据存储速度成倍增加,并且依靠FPGA 强大的数据处理能力和并行运行的特点,该存储阵列也是比较容易实现的[12]。如上述单个通道串行排列时的数据传输速度最快可以达到47.35 MB/s,通道间N倍并行排列后,存储速度将会为N×47.35 MB/s。通道间并行,通道内串行的流水线控制如图5所示。

图5 流水线控制

3 坏块检测及突发块处理

3.1 单片检测

由于受nand Flash 生产工艺的影响,不能保证在整个使用周期中都是可靠的,或多或少的都会产生坏块,并且Flash 在出厂时有的就会存在坏块[13]。Flash 在全部擦除后,没有数据写入前,正常状态所有的位都为高位,而出现坏块后,将会在擦除或者写入数据时不能将某些位拉高,如果不对这些坏块加以处理,将会导致数据存储出现错误,达不到预期的存储效果[14]。

Flash 每页都会有备用区,而坏块的信息将在每块第一页的备用区做以标记。单片Flash 的检测方式为每次对Flash 进行擦除或者数据写入等操作时,都对存放坏块信息的页空闲区进行遍历性检查,如果为坏块,将会做坏块标记,后续操作对该块不再进行数据写入,如果为正常的存储块,则地址加一,继续检查下一块,直到所有的块状态信息都检查结束。这种坏块检查方法虽然实现起来较简单,但是所需时间较长,不适合高速数据的存储。

3.2 阵列检测

将Flash 阵列组合是为了满足高速数据存储的要求。如果坏块检测还是使用遍历性检查的方法,那将会对存储系统的存储速度产生很大影响,为此将使用一种提高坏块检测效率的方法进行阵列式Flash 的坏块检测。

Flash 中块的好坏只有两种状态,这两种状态可以用0、1 来表示,该设计所选的Flash 有8 192 个块,8 kB 的RAM 可以将这些Flash 的所有块信息写入,这个操作只需在上电后将块信息进行读取写入RAM中,后续操作需要进行坏块检测时只需读取RAM 中的信息即可。这种坏块检测方式相对于遍历性检测大大节省了检测时间,提升了系统的存储速度。当遇到阵列式Flash时,如果每片都映射到一个RAM中,那所需的时间也相对较长,也会造成资源的浪费。通道内的Flash 每个芯片的存储块数是相同的,地址也是相同的,因此设计了一种将一个通道内地址相同的块看成一个大块的检测方法,这个大块中如果有一个块是坏块,就判定这一整个大块为坏块,如图6所示。

图6 组合块检测

这种坏块检测方式一定程度上浪费了一些好的存储块,但是相对系统总体来说,提高了系统的数据存储速度,所浪费的存储容量相对总容量来说也是很少的一部分[15]。查阅芯片手册可知,该芯片最少有8 032个有效块,即最多每块中有160个坏块,以每个通道串行6片,且每块Flash的坏块地址都不相同,每个通道最多可达3 600个坏块,这也就导致可能会有最多3 000个有效块被浪费。经计算得知,在每个通道最多浪费3 000个有效块的情况下,该通道的Flash 存储利用率为93.9%,而实际使用下,每片的坏块不会那么多,无效组合块也就不会那么多,实际的存储容量利用率也会高于93.9%,对存储空间不会造成太多的浪费。

3.3 坏块替换

在Flash 使用过程中,也会不可避免的产生一些突发的坏块,在数据写入时如果不做相应的处理,就会使数据存储产生错误,导致数据存储失败,降低数据存储装置的可靠性[16]。

在数据存储过程中,当数据写入到块A 的第n页时,如果发现返回错误信息,不能正常写入数据,将该块和该页的地址记录下来,并将该块第n页到最后一页的数据写入到下一个能正常存储数据的块B对应页中,并对上述块A 做坏块标记。当全部数据都写入完成以后,对照之前记录的坏块和页地址,将已经写入坏块A 中的前n-1 页的数据以页为单位读出后重新写入到其下个正常块B 的对应页中完成数据的完整写入。滞后重写如图7 所示。

图7 滞后重写

4 测试与验证

将模拟信号源产生的数据存入矩阵式存储阵列中,对存储系统存储容量,存储速度以及存储阵列的利用率等进行测试。结果显示矩阵式存储阵列存储容量和数据存储速度相较单片存储有成倍的提高,单个通道的有效块使用效率达到了99%以上,远高于理论最低使用率的93.9%,且数据存储可靠,满足数据存储系统的各项要求。图8 为矩阵式存储阵列存储的数据。

图8 存储数据

5 结束语

针对单片Flash 存储容量有限,存储速度较低的现状,结合Flash 的存储特性,提出了一种使用Flash阵列存储数据的方法,通过布置存储阵列,RAM 映射进行坏块检测,滞后重写等设计大大提升了数据存储容量和数据存储速度,经过理论分析及试验验证,该方法可行性高,技术实现难度适中,为高速数据存储提供了可行性方案和技术路线。