基于FPGA和USB的数据采集系统的设计

王水鱼,陈 璐

(西安理工大学 自动化与信息工程学院,陕西 西安 710048)

随着火炮技术的高速发展,新型多高管射自动火炮的不断涌现,以前的测试系统不能满足精确测量的要求。为了适应研制和生产的需要,测试系统应当具备一定的弹性,易于根据需要灵活组建。因此,需要一种通用、便携、数据采集精度高、同步性好、易于使用的设备。

传统的数据采集系统速度慢、处理功能简单、采用分立元件、电路非常复杂,而且可靠性差、不易调试、不能良好地满足特殊要求。针对传统数据采集系统存在的不足,提出一种基于USB和FPGA技术的多通道同步数据采集系统[2]。首先,本系统既能与计算机连接进行实时数据采集,也能用NAND Flash存储采集数据进行非实时数据采集;另外,它将FPGA和USB技术应用于火炮动态参数测试系统的数据采集子系统,为提高测量精度,组建灵活测试系统提供了技术支持。同时,该数据采集电路模块还可以用在其他测试系统,对于民用及工业等方面也有实际意义[1-3]。

1 系统的组成及原理

系统设计总体框图如图1所示。

2 FPGA单元功能模块设计

FPGA选用Altera公司的Cyclone系列芯片EP1C12,系统设计模块图如图2所示。

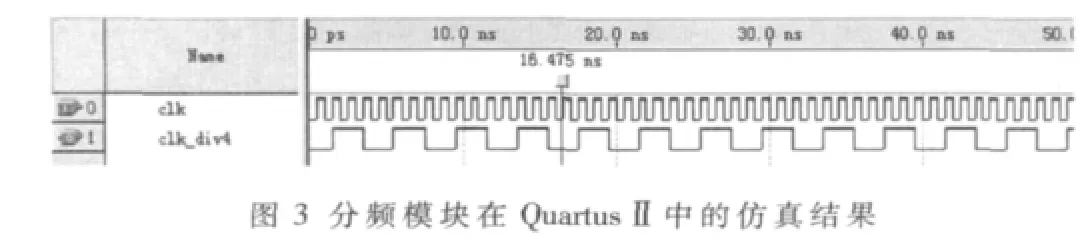

2.1 分频模块的设计

分频模块是将外部时钟进行分频设定,得到系统内部AD控制模块和存储模块所需要的时钟,并为AD芯片提供时钟信号基准。此模块采用VHDL语言编程实现,其4分频时序仿真图如图3。分频模块的外部时钟输入频率为20 MHz,产生的时钟频率为5 MHz。

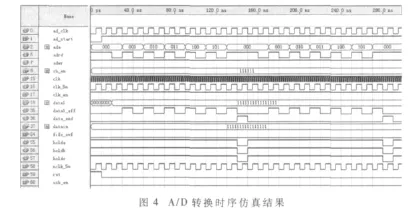

2.2 A/D转换控制模块

A/D数据接口控制模块实现对ADS8364数据的采样。ADS8364是TI公司的一款高速、低功耗、六路模拟输入、16位并行输出的模数转换器。六路模拟输入分为三组(A、B和C),每个输入端都有一个保持信号来实现所有通道的同时采样与转换功能,适合于多路采集系统的需要。本模块对ADS8364的控制引脚有:模拟采样通道控制信号/HOLDA、/HOLDB、/HOLDC;数据输出模式以及通道选择信号 A0、A1和A2;读控制信号/RD;使用5 MHz时钟驱动一个20个状态的状态机(模为20的计数器)。在计数值为 15时将 HOLDA、HOLDB、HOLDC置0启动一次数据采样。在计数值为 2-3、4-5、6-7、8-9、10-11、12-13且相应通道得到使能时,分别发出通道1到通道 6 的通道地址。 在 3、5、7、9、11、13 发出读信号读取相应通道的数据。在计数为15时发出采样完毕信号,指示六通道数据已经采集完毕。AD采样控制时序如图4所示。

2.3 SRAM乒乓缓存模块

乒乓控制模块部分,按照功能将其分为4个转换状态 S0、S1、S2、S3。其中状态 S0为初始化状态,状态 S1负责对 SRAM0写数据,状态 S2负责对 SRAM1写数据,从SRAM0读数据,状态S3负责对SRAM0写数据,从SRAM1读数据。图5和图6分别是乒乓控制模块的状态转移图和乒乓操作时序仿真结果图。

2.4 Flash控制模块

系统选用三星(SAMSUNG)公司的 NAND Flash芯片K9F2G08,Flash控制器的主要功能是响应PC机命令,根据命令产生相应的时序实现对Flash的操作。完成的操作有:(1)擦除操作:即对Flash进行格式化。(2)写操作:Flash控制器判断PC机的写命令,当PC机发出写命令时,Flash控制器执行一次写操作。(3)读操作:Flash控制器PC机的读命令,当PC机发出读命令时,Flash控制器执行一次读操作。读出的数据被送往USB。

2.5 数据控制模块

数据控制模块用于产生乒乓操作和Flash控制器的地址总线、数据总线和控制总线,是乒乓操作模块和Flash控制器的桥梁。实现乒乓操作至Flash控制器数据的正确转移。同时数据控制模块还负责从Flash控制器读取数据,并送至USB用于总线交互。

2.6 USB控制模块

USB接口芯片采用EZ-USBFX2 (CY7C68013),FX2作为USB2.0数据通道来实现与主机的高速通信。FPGA能够满足Slave FIFO要求的传输时序作为Slave FIFO主控制器。图7是FX2的状态转换图。

同步Slave FIFO写时序如下:

IDLE:写事件发生时,转到状态 1;状态 1:指向 IN FIFO,激活 FIFOADR[1:0],转向状态 2;状态 2:如果 FIFO满标志为 “假”(FIFO不满),则转向状态3,否则停留在状态 2;状态3:传送总线驱动数据,为 1个 IFCLK激活 SLWR,转向状态 4;状态 4:如果有更多的数据要写,则转向状态2,否则转向IDLE。

3 USB芯片固件程序及驱动程序

3.1 FX2的固件程序设计

CY7C68013芯片固件程序负责处理PC机发来的各种USB请求,以完成主机与外围电路间的数据传输。固件程序包括3个过程:(1)初始化,处理器和外围电路的初始化;(2)主函数,完成符合设备特定要求的代码;(3)中断处理,处理各种中断的程序代码。

Cypress公司的EZ-USB FX2开发套件提供给用户1个固件函数库(Ezusb.lib)和固件框架(Framework),两者均是基于KEIL C51开发的。固件函数库提供了一系列函数来加速USB固件程序的开发,使用时只需在程序中包含EZUSB.H和EZREGS.H两个头文件,并在项目中链接Ezusb.lib,就可以直接使用固件库中的各个函数,固件流程图如图8。

3.2 USB设备驱动程序

USB设备驱动程序的主要功能是使Win32应用程序能正确访问本数据采集卡的硬件设备。本设计中将CY7C68013的固件代码存放在上位机上,当系统上电或USB连接时,再将其下载至芯片的RAM中,由增强型8051执行。这一过程需要使用2个驱动程序:一个用于下载芯片的固件程序,另一个用于实现本数据采集卡的具体功能。也可以使用EZ-USB的通用驱动程序,很多USB芯片的厂商都为其USB芯片提供了通用驱动程序,可以满足大部分系统的需求,用户可在此基础上直接进行固件程序的开发[4-6]。

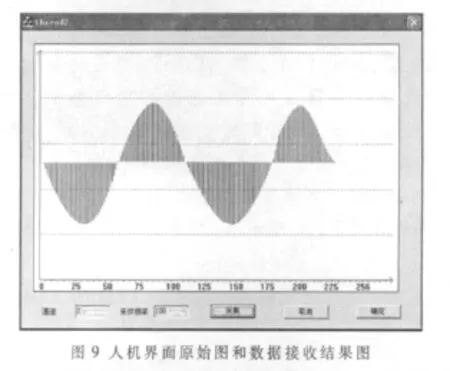

4 主机应用程序设计

应用程序主要负责读取系统硬件所输出的数据采集结果,并实时显示波形,使用微软的Visual C++6.0语言编写Win32应用程序,可根据具体应用进行扩展。按照系统指标要求,应用程序设计主要完成以下功能:设置采样频率、控制读取数据通道、读取数据、波形显示等。人机界面原始图和第二个通道接收到的数据显示波形如图 9。

该系统采用 USB2.0接口与计算机连接,利用FPGA完成系统控制。它既能与计算机连接进行实时数据采集,也能用NAND FLASH存储采集数据。该系统体积小、功耗低,特别适合环境比较复杂下的测试系统,使用灵活方便、适应性强。

实验表明,本设计可以很好地实现6通道同步采样,其采样频率范围 0.1 kHz~250 kHz,完成采样精度16 bit的数据采集。

[1]邱春玲,张广明,吴振翔.基于DSP和 FPGA的电梯智能数据采集系统的设计.计算机工程与设计,2009,30(7):1577-1579.

[2]范华,谭玉山.两通道高速数据采集系统[J].电子测量与仪器学报,1996(10):1-2.

[3]严雪萍.基于FPGA的高速数据采集系统[J].微计算机信息,2008(1-2):209-211.

[4]CY7C68013 EZ-USB@FX2TM USB microcontroller highspeed USB peripheral controller.Cypress Semiconductor Corporation,2002.

[5]张惠娟.Windows环境下的设备驱动程序设计.西安.西安电子科技大学出版社,2002:19-20,102-103,253-300.

[6]薛园园.USB应用开发技术大全[M].北京:人民邮电出版社,2007.