基于MCl45163P的智能锁相频率合成器设计

曾素琼

(嘉应学院 电子信息工程学院,广东 梅州 514015)

1 基于MCl45163P的锁相频率合成器系统设计

基于MCl45163P的锁相频率合成器系统框图如图1所示。环中的÷N分频器采用可编程的程序分频器,fr=fv时,环路锁定,频率合成器输出频率为 fo=Nfr=Nfs/R。式中 fr为参考频率,通常是用高稳定度的晶体振荡器产生,经过固定分频比的参考分频之后获得,此处 fr=fs/R;因 N、R均可调,输出频率源的频率点较丰富,较容易满足各种场合的要求。

MCl45163P是Motolora公司的CMOS大规模集成锁相频率合成器,其内部功能块包括图1中虚线部分,MCl45163P内部结构框如图2所示。主要集成了参考分频器、两个相位比较器和4位BCD/N分频器,配合环路滤波和压控振荡器可以得到一个完整、实用的锁相频率合成器。

图1 基于MCl45163P的锁相频率合成器系统框图

图2 MC145163P内部框图

输出频率间隔和13位/R计数器:引脚RA0和RAl用来决定MCl45163P内部参考分频器的分频比,RA0、RA1有四种组合决定参考分频器(R计数器)的分频比的情况:RA1、RA0=00 分频比 512;RA1、RA0=01 分频比1 024;RA1、RA0=10 分频比 2 048;RA1、RA0=11 分频 比4 096。选择合适的分频比,可以得到对晶振频率fs的分频,进而得到参考频率fr=fs/R。因为频率合成器的输出频率 fo=Nfr,因此,fr也是输出频率的间隔(步进频率)。

输出频率和4位BCD/N计数器:MCl45163P内部带有4位BCD/N计数器,通过设定4位BCD的数值,可以得到N计数器(分频)值。例如:4位 BCD数值设置为 1 000,则环路中 N计数器(分频)的 N值为 1000(引脚 24~9为0001 0000 0000 0000);4位 BCD数值设置为 0750,则环路中 N计数器(分频)的 N值为 0750(引脚 24~9为 0000 0111 0101 0000)。频率合成器的输出频率fo=Nfr。

2 MCl45163P的应用设计

2.1 频率范围和频率步进设计

只从N分频的设置范围3~9 999来看,如果频率步进 fr设定为 1 kHz,那么 f0输出频率为 3 kHz~9 999 kHz,但要受到VCO输出频率覆盖范围的限制。实际选用的VCO器件74LS628,环路处于锁定状态的测量频率范围在0.7 MHz~9.999 MHz。另外,考虑到最后输出波形达到占空比为50%的方波,因此可以在VCO输出信号后加一个1/2分频器进行整形、分频,这样输出波形质量较好。于是这里将频率步进fr先设定为2 kHz,fo=Nfr=1.4 MHz~19.998 MHz,即 fo的频率步进是 2 kHz;经过 1/2分频器件得到的 fo’=fo/2=0.7 MHz~9.999 MHz, 即最后输出信号fo’的频率步进为 1 kHz,输出波形和步进同时达到要求,实际相当于双环锁相频率合成器。

2.2 BCD编码接口设计

用10个按键S0~S9产生十进制0~9的BCD编码,4个按键S10-S13用来切换不同位数,并用数码管实时显示当前BCD编码所对应的十进制数。电路框图如图3所示,其中以单片机 AT89C2051为核心,编写4×4矩阵键盘的扫描控制处理程序,可以实现上述按键功能。采用该电路得到BCD编码,优点为可靠、方便,每次只需按下对应的位控制按键(S10~S13)和对应的BCD编码按键(S0~S9)。 由上述可知,输出信号fo的频率步进为1 kHz,所以数码管显示BCD编码对应的十进制数就是当前PLL频率合成器的输出频率。

2.3 VCO 选择

TTL系列中的 74LS624~74LS629是6种比较常用的VCO集成电路。该系统选用压控振荡器74LS628,器件内含 1个 VCO、有双向输出(除 Y输出引脚,有带 Z输出引脚)、使能端、频段转换、可外接Rext作温度补偿。

使用74LS628压控振荡器时应注意如下特性:

(1)2脚频段转换控制电位VRNG、13脚电位VFC不变时,3、4脚外接电容器Cext越大,输出信号频率越低,有利于达到频率范围的下限fmin,但不利于频率范围的上限fmax。反之,结论相反。因此必须选择合适的Cext,且需与VRNG配合好,才可得到所要的输出频率。

(2)2脚频段转换控制电位VRNG、3、4脚外接电容Cext都不变时,13脚电位VFC越高,输出信号频率越高。13脚电位VFC来自于MCl45163P与LF的控制信号动态控制VCO而达到锁定状态的输出 PDout;3、4脚外接电容器Cext应取合适的电容值:这样利用2脚频段转换控制电位VRNG的高低,就可以比较容易地实现输出频率fo的频率覆盖范围。

3 整体电路设计

整体电路设计如图4所示。

图4中,接入 MCl45163P的晶振为 2.048 MHz,若RAl、RA0=01即分频比为 1 024,则可设定为 2 kHz。 经 4位BCD编码可方便地设定N值,并可以由数码管显示当前BCD编码的十进制数,也即为当前PLL频率合成器的输出频率。VCO的Y输出端通过电容交流耦合到MCl45163P的1脚,经过其内部N分频后与fr比较,并由4脚 PDout输出,再经 3.3 kΩ 电阻和 4.7 μF电容组成的积分型低通滤波器得到控制电压Vc最后接在VC0的13脚。VCO的8脚输出的信号送至l/2分频器分频并整形,输出信号频率 fo’。

对于VCO频段控制引脚RNG(2脚)这样处理:通过集成数值比较器对BCD/N分频的最高位D3进行分档,例如可以通过DIP开关设定数值比较器基准BCD(B3~B0)为 0100或 0011,当 D3小于或超过基准后分别得到高或低电位VRNG信号。VRNG接入VCO的2脚,实现整个频率范围的覆盖。否则固定VRNG不变的前提下,VCO无法实现频率范围的覆盖。

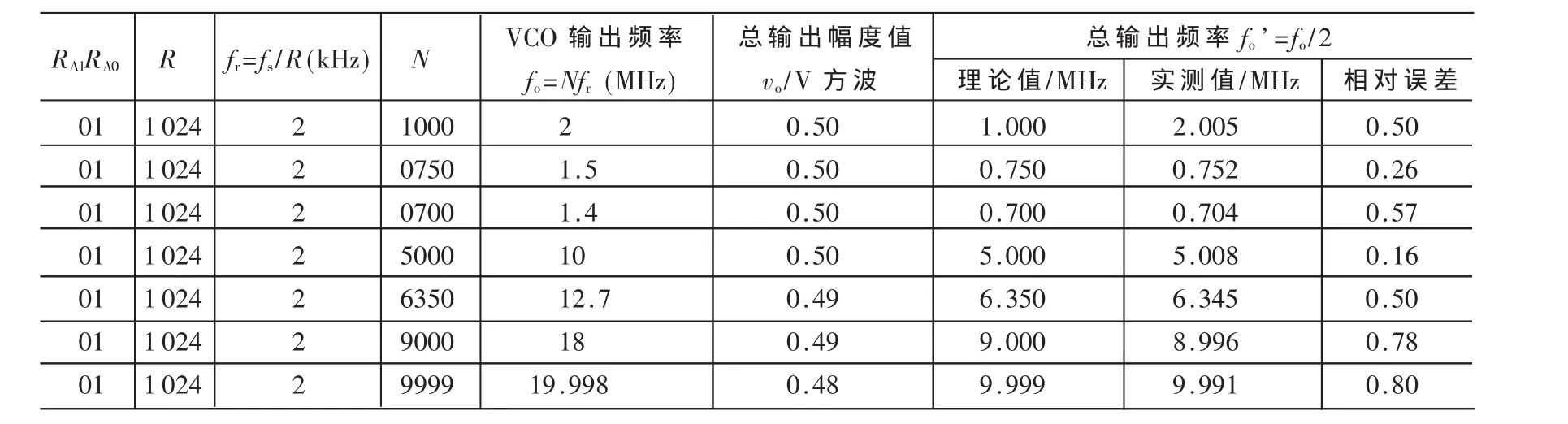

表1 锁相环输出频率及各参数 晶振频率fs=2.048 MHz

4 实验及结果分析

系统主要参数选择及实验结果如表1。

实验结果分析:4位BCD设置后,数码管显示的十进制数值和用频率计测量的信号频率相一致,验证了电路处于锁定状态,同时满足前面提到的数码管显示BCD编码对应的十进制数就是当前PLL频率合成器的输出频率。系统达到了锁相频率合成,输出频率源在R为1 024时,输出频率范围:0.7 MHz~10 MHz,输出频率步进 1 kHz;锁相环中的频率步进2 kHz,信号源波形质量较好,频率实测值与理论计算值误差较小,相对误差在0.8%以内。改变R时,输出频率范围可方便改变;改变N,得到不同输出频率点。

本文设计的基于MCl45163P智能锁相频率合成器系统,加入了单片机控制环节,容易实现频率输出的自动控制,增加了频率步进搜索、预置频率值、显示频率等功能,能得到输出频率覆盖范围较大、输出频率步进较小1 kHz(保证输出频率分辩率高)、锁相环频率步进较大2 kHz(保证频率转换时间较小)、波形质量较好(杂波较少)高频频率源。本设计具有一定的创新性,利于对锁相频率合成芯片的应用研究和锁相频率合成技术的研究。

[1]曾素琼.基于低压电力线载波通信的电机控制系统设计[J].微型机与应用,2009,28(22):26-28.

[2]曾兴雯,刘及安,陈健.高频电路原理与分析[M].西安:西安电子科技大学出版社,2005.

[3]张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,2003.

[4]庄卉,黄苏华,袁国春.锁相与频率合成技术[M].北京:气象出版社,1996.