主子板结构的ΓОСТ18977多用途接口板设计*

,3

(1.空军工程大学 工程学院,西安 710038; 2.空军通信训练基地,河北 保定 071051; 3.解放军驻成都飞机工业公司军事代表室,成都 610092)

1 引 言

俄罗斯标准ΓОСТ18977-79[1](以下简称ΓОСТ18977)和PTM1495-75[1](以下简称PTM1495)采用32位双极性归零串行数据(简称为32位码)传送方式来进行数字信息的传送和交换。ΓОСТ18977规定的是飞机和直升机的成套机载设备功能互联的类型、电信号的形式和电平,其中一部分规定了与美国标准ARINC429[1]相对应的串行码信号的类型及其电气标准,而与之配套的PTM1495技术资料中则规定了按照ΓОСТ18977采用双极性码进行信息交换的具体方法[1]。该标准在俄制军用飞机的机载设备上得到了广泛的应用。目前,我国对符合俄罗斯标准ΓОСТ18977的接口板不多,并且接口种类少,不能同时满足多种主机接口的要求,影响了部队战斗力的提高,因此对符合ΓОСТ18977标准的多用途接口板的研制,具有重要的军事意义和应用前景。根据以上需求,本文设计开发了一种能够兼容USB、CPCI和PXI 3种接口的通用多用途接口板。

2 ΓОСТ18977总线简介

在电气标准方面,依照ΓОСТ18977的规定采用与ARINC429标准相同的双极性归零制的三态码调制方式,而在对信号电平的定义上,ΓОСТ18977的定义见表1(表中所列均为A线到B线电位差)所示。

表1 ΓОСТ 18977信号的电平标准

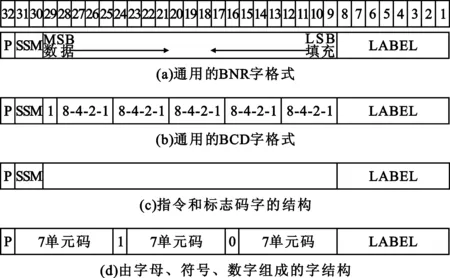

根据ΓОСТ18977和PTM1495的规定,采用二进制码作为所有系统间、全套设备间通信的统一语言。而它同时又规定了通信中可以采用二进制码、二-十进制码(BCD)、指令和标志码,以及由字母、符号、数字组成的字符码等4种数据的格式。这4种数据的通信都要按照ΓОСТ18977规定的32位串行数据的方式来发送和接收,具体在32位的字中格式定义如图1所示。

图1 ΓОСТ18977传输字格式

3 系统硬件设计

3.1 硬件整体设计

目前国内外已有产品的接口电路均仅支持一种接口用途。这样做的缺点是当需要更换为另一种主机总线接口时,不但要更改FPGA内的程序,还需重新设计接口电路,导致开发时间延长、经费增加。此外,国内的工控机普遍采用的是CPCI或PXI插槽,普通的台式机电脑则采用PCI和USB接口,而在没有PCI和PXI等插槽的笔记本电脑上均具有USB接口。因此,本系统采用主子板结合的方式同时实现USB、CPCI和PXI 3种接口用途的接口电路,可使该接口卡满足当前各种主机的接口要求。

鉴于上述原因,本系统采用FPGA、USB、CPCI及PXI技术,依据ΓОСТ18977航空总线规范,设计并开发一种兼容3种接口的多通道总线接口板,可以满足当前各种主机的接口要求,节省大量经费。并设计了采用双口RAM IDT70V658S[2]作为FPGA和接口控制器件之间的共享存储器,通过它来协调FPGA和各个接口控制器件之间传输的信息,从而实现系统多接口用途的设计。

本系统的硬件设计在结构上采用主子板的方式,主板主要由FPGA、双口RAM和电平转换3部分组成,子板主要由接口控制芯片和总线接口组成,具体分为USB接口子板、CPCI接口子板以及PXI接口子板3个子板。主板和子板间通过连接电缆相连,用户需要什么接口便可选择相应的接口子板与主板相连。系统总体结构如图2所示。

图2 系统结构图

3.2 主板设计

主板主要由FPGA、DPRAM和电平转换3部分组成,其功能主要是实现ΓОСТ18977航空总线协议。其功能分为两部分:一是接收经过转换成数字信号的符合ΓОСТ18977航空总线的数据并将其送入双口RAM;二是将双口RAM中暂存的数字信号按照ΓОСТ18977航空总线协议的数据格式输出。

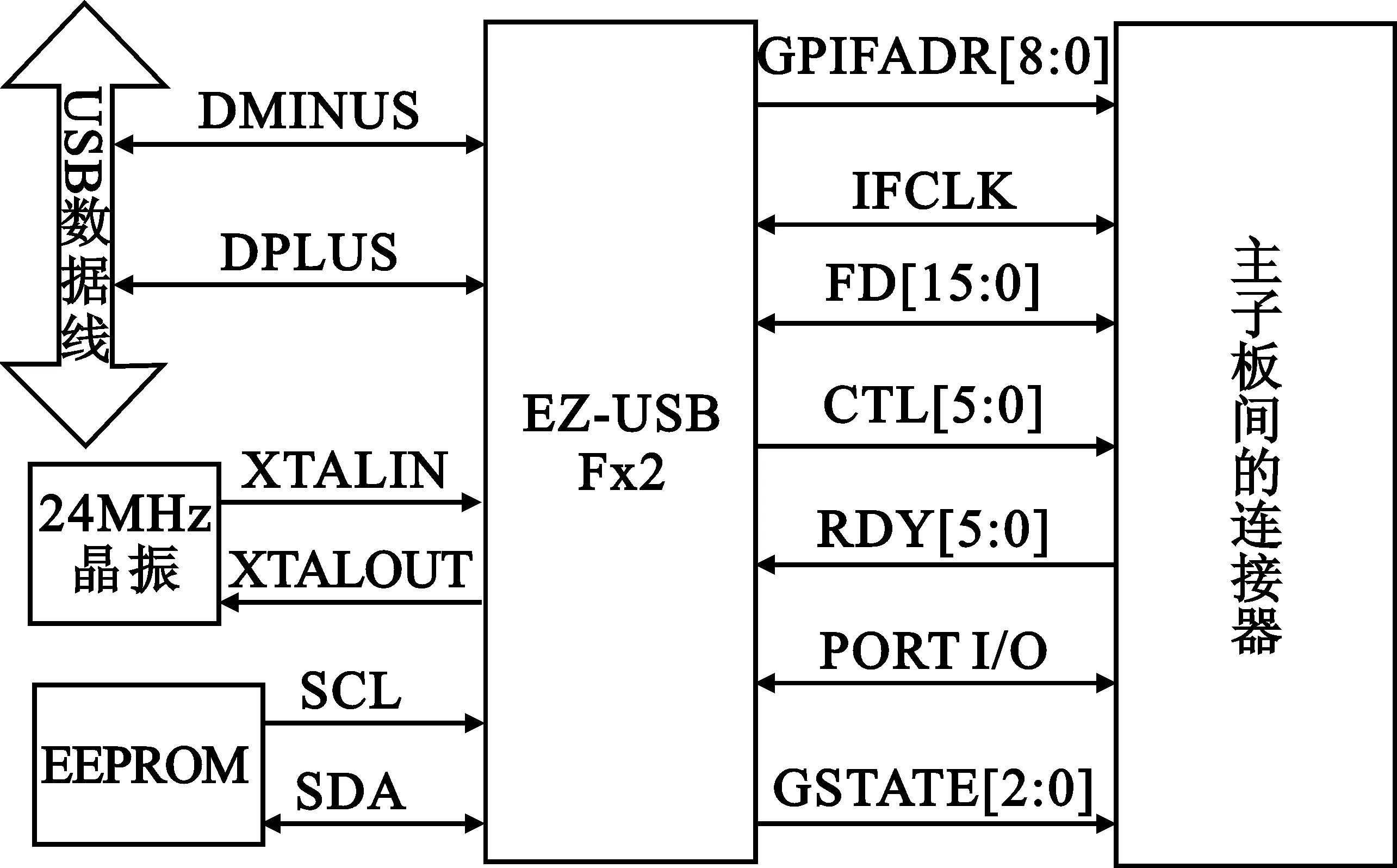

3.3 USB子板总体设计

图3 USB接口子板结构图

3.4 CPCI子板总体设计

CPCI接口子板主要由PCI控制器件PCI9054[3]和热插拔控制器件LTC1644[4]组成。PCI9054主要用来处理CPCI接口的PCI特性,它将复杂的PCI总线的数据传输逻辑转化为简单的本地控制逻辑;LTC1644则主要用来处理CPCI接口的热插拔特性。

CPCI接口子板的功能主要分为两部分:一是将主机的CPCI信号转换成并行信号传给双口RAM;二是将双口RAM中暂存的并行信号转换成串行信号通过CPCI接口传给主机。CPCI接口子板结构如图4所示。

图4 CPCI接口子板结构图

3.5 PXI子板总体设计

PXI接口子板主要由PCI控制器件PCI9054[3]、热插拔控制器件LTC1644[4]和FPGA[5]组成。其功能主要分为两部分:一是将主机的PXI信号转换成并行信号传给双口RAM;二是将双口RAM中暂存的并行信号转换成串行信号通过PXI接口传给主机。PXI接口子板结构如图5所示[6-7]。

4 多接口用途的设计与实现

本接口卡支持3种接口用途,各个接口传输的数据字格式、控制信号等均有差异,所以采用了双口RAM IDT70V658S[2]作为FPGA和接口控制器件之间的共享存储器,通过它来协调FPGA和各个接口控制器件之间传输的信息,从而实现系统多接口用途的设计。另外,各个接口总线和ΓОСТ18977航空总线标准传输速率相差很大,采用双口RAM可以很好地解决两者之间读写速度问题。

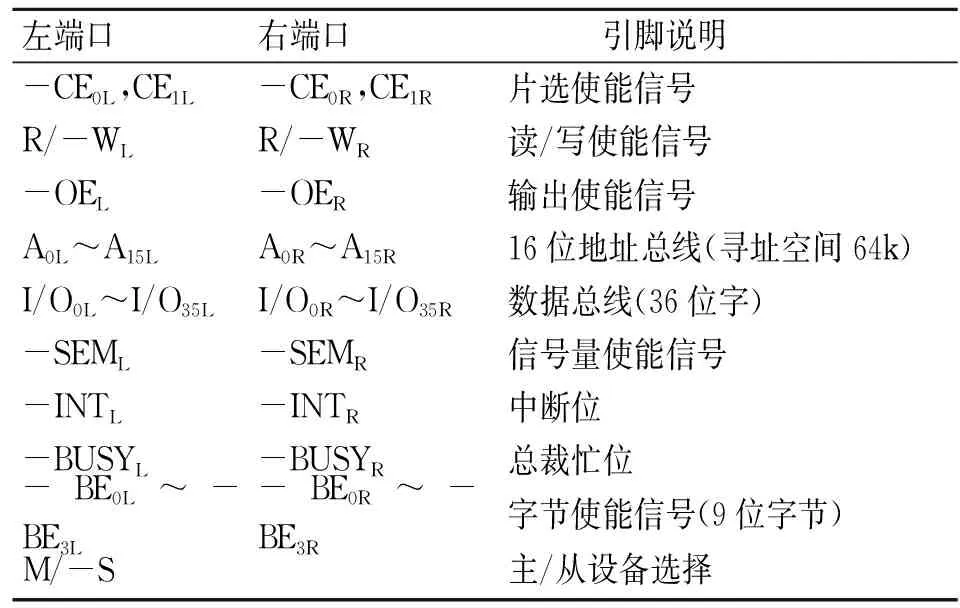

4.1 双口RAM主要引脚设计

双口RAM的存储器端口一边由各子板上的控制器件通过连接电缆来使用,另一边由主板上实现ΓОСТ18977航空总线协议的FPGA器件来使用。存储器的主要用途是保存ΓОСТ18977数据字,由于本系统可用于多种接口用途,存储器访问单元可根据需要选择8位、16位或32位字,具体是通过控制信号-BE0L~-BE3L进行选择。IDT70V658S共有36根数据总线,而ΓОСТ18977数据字为32位,所以设计时将IDT70V658S左端口的I/O8L、I/O17L、I/O25L、I/O35L数据线不连,呈高阻态。32位数据字从高到低依次为I/O34L~I/O26L、I/O24L~I/O18L、I/O16L~I/O9L、I/O7L~I/O0L。右端口的数据线连接与左端口相同。IDT70V658S主要引脚说明如表2所示。

表2 IDT70V658S主要引脚说明

使用双口RAM时,若两端同时对同一地址单元执行写操作或者一读一写操作,就会发生冲突,造成写错误或者读错误,即争用问题。该设计中选择使用双口RAM的硬件判优方式来解决这个问题。这样,当存储器两端同时对同一地址单元访问时,只有一方可以进行有效访问,而另一端的访问为不确定。所以存储器使用-BUSY信号表示双方访问的有效性(-BUSY=0有效,-BUSY=1无效),即-BUSY有效的一方表示访问不确定,不确定方访问操作需要重复。在连线存储器时,把存储器左右端口的-BUSY都引入FPGA中。可以使用FPGA硬件逻辑对-BUSY进行判断,使访问无效一方重新访问存储器[2]。

4.2 双口RAM存储单元的划分及数据缓冲区的维护

根据研制的需要,将双口RAM分为发送、接收两部分。结合对双口RAM可以同时读写的特点,又将发送、接收RAM地址区各划分为8部分,分别对应8个发送、接收通道。双口RAM的分配见文献[8-9]。

每个发送缓冲区的前5个单元用来存储发送控制字、SPOS指针、RPOS指针,每个接收的前7个单元用来存储发送控制字、LABEL标志、SPOS指针、RPOS指针。存储发送命令或接收命令的单元均只用最后8位,这是由本设计中双口RAM的最小访问单元为8位所决定的。

将翻转课堂应用到“射频识别原理与应用”课程教学中,可以解决当前该课程教学中存在的问题,引导学生自主学习,促进师生之间的交流,提高学生的深度学习能力。目前,基于翻转课堂的“射频识别原理与应用”课程教学设计已经完成,还需建立一个“射频识别原理与应用”课程的在线学习平台或APP,将教学资源分类细化列出,学生可以通过这个平台进行学习交流,老师在教学过程中可以不断地去补充和完善教学资源和设计,并通过这个平台针对学生的学习记录和学习互动情况进行评价考核。

发送控制字位宽为8位;接收控制字位宽为16位;LABEL为8位标志数据;SPOS和RPOS为每个缓存区的两个指针,每个指针大小为16位,用来控制读写,指针SPOS指向缓冲区中当前第一个空闲存储单元,指针RPOS指向缓冲区中当前第一个保存有效数据的存储单元。

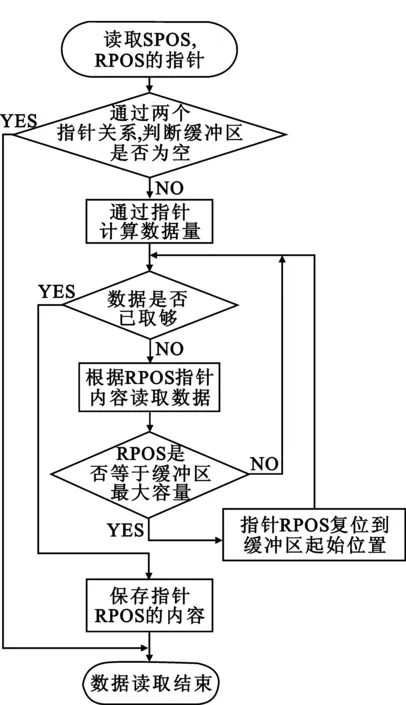

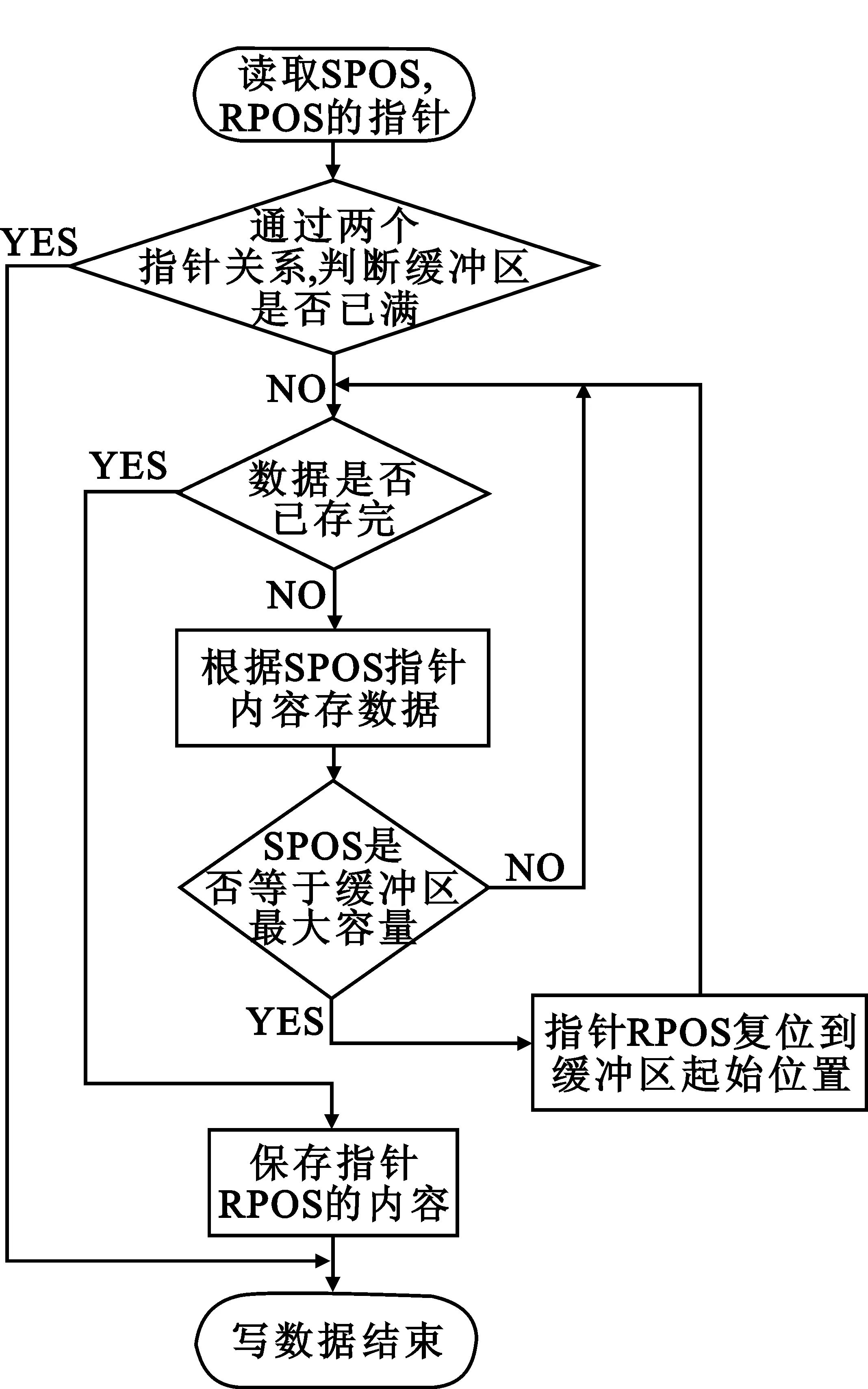

双口RAM缓冲区的读写数据流程如图6所示。

(a)读数据流程

(b)写数据流程

数据的保存采用循环缓冲区结构。双口RAM的两端通过读取SPOS和RPOS两个指针变量来判断当前缓冲区的状态是空还是满。本系统规定缓冲区满时存储数据的容量为Δ-1,其中Δ为缓冲区最大容量。

在对缓冲区进行读写操作后,应用程序要判断两个指针内容。当两个指针所指地址到达缓冲区终端时,应用程序把这两个指针复位到缓冲区的起始地址,这样即实现了循环缓冲区的存取。循环缓冲区结构见文献[10]。

当读数据一方进入缓冲区后,先读取SPOS和RPOS指针变量,然后判断当前缓冲区是否为空。如果缓冲区非空,则根据RPOS指针把数据取出。每取出一个数据后,应用程序要判断RPOS指针是否已到达缓冲区终端,如果RPOS到达缓冲区终端,则复位该指针指向该缓冲区的起始地址。最后读数据一方要把RPOS指针值更新到固定内存单元中。

当写数据一方进入缓冲区后,先读取SPOS和RPOS指针变量,然后判断当前缓冲区是否已满。如果缓冲区仍有空闲单元,则根据SPOS指针把数据存入存储器中。每保存一个数据后,应用程序要判断SPOS指针是否己到达缓冲区终端,如果SPOS指针到达缓冲区终端,则复位该指针指向该缓冲区的起始地址。最后写数据一方要把SPOS指针值更新到固定的内存单元中。

5 结 论

本接口板具有USB、CPCI和PXI多接口的设计,使得该接口板具有很好的通用性和兼容性。经测试表明,采用双口RAM作为FPGA和接口控制器件之间的共享存储器,可以很好地协调FPGA和各个接口控制器件之间传输的信息,从而实现系统多接口用途的设计。另外,各个接口总线和ΓОСТ18977航空总线标准传输速率相差很大,采用双口RAM也可以很好地解决两者之间读写速度的问题。

参考文献:

[1] 王勇,于宏坤.机载计算机系统[M].北京:国防工业出版社,2008.

WANG Yong,YU Hong-kun.Airborne Computer System[M].Beijing:National Defense Industry Press,2008.(in Chinese)

[2] Integrated Device Technology,Inc. High-speed 3.3V 128/64/32K 36 Asynchronous Dual-Port Static RAM[M].CA,USA:Integrated Device Technology,Inc.,2005.

[3] PLX Technology,Inc.PCI 9054 Data Book V2.1[M].CA,USA:PLX Technology,Inc.,2000.

[4] Linear Technology Corporation.LTC1644 Data Sheet[M].CA,USA:Linear Technology Corporation,2001.

[5] Altera Corporation.Cyclone-device-handbook[M].CA,USA:Altera Corporation,2008.

[6] 何光亚.基于PXI总线的QPSK解调模块设计[D].成都:电子科技大学,2007.

HE Guang-ya.The design of a PXI bus-based QPSK demodulation module[D].Chengdu:University of Electronic Science and Technology of China,2007.(in Chinese)

[7] 聂玉庆.基于PXI总线的QPSK解调器设计实现[D].成都:电子科技大学,2007.

NIE Yu-qing. The design and realization of QPSK modulator based on PXI bus[D]. Chengdu:University of Electronic Science and Technology of China,2007.(in Chinese)

[8] 蒋谢芳.基于嵌入式微处理机和Compact PCI的ARINC429总线接口板的设计[D].西安:西北工业大学,2006.

JIANG Xie-fang. The design of ARINC 429 bus interface card based on the embedded microprocessor and Compact PCI[D]. Xi′an: Northwestern Polytechnical University, 2006. (in Chinese)

[9] 宾辰忠.基于MCF5206的ARINC429通信板卡的设计与实现[D].西安:西北工业大学,2005.

BIN Chen-zhong. The design and realization of ARINC 429 communication card based on MCF5206[D]. Xi′an: Northwestern Polytechnical University, 2005. (in Chinese)

[10] 严蔚敏,吴伟民.数据结构[M].北京:清华大学出版社,2004.

YAN Wei-min, WU Wei-min. Data Structure[M].Beijing: Tsinghua University Press, 2004. (in Chinese)