基于FPGA的AIS中频收发信机设计及实现*

(中国西南电子技术研究所,成都 610036)

1 引 言

船舶自动识别系统(AIS)是由国际海事组织(IMO)、国际助航设备和航标协会(IALA)以及国际电信联盟(ITU-R)共同提出的技术标准,可用于船舶避碰、水上智能交通管理及海域监视等领域。AIS设备主要有Class A、Class B船载应答机和AIS基站、航标灯等。目前,AIS设备在欧美国家已广泛使用,我国及东南亚地区正处于推广安装阶段。

AIS收发信机是AIS硬件设备的主要组成部分,由工作于海事VHF频段的一路TDMA发射机、两路TDMA接收机组成,它的实现是AIS物理层的关键技术之一。目前,市场上销售的AIS设备中,该收发信机终端部分的功能由专用芯片(如英国CML公司的CMX910和CMX589等)在零中频实现,它与射频部分之间为基带接口。这样的设备结构形式不利于设备的功能扩展及改进,不利于终端模块的单独测试。另外,由于海事AIS属于专业市场,市场容量相对有限,对AIS专用芯片的市场需求量不大,因此CML公司已逐渐减少CMX910等芯片的生产,这使得有必要研制该类芯片的替代品。随着软件无线电理论的发展成熟和高性能A/D、D/A器件及FPGA价格的大幅降低,该收发信机的中频数字化低成本实现成为可能。

根据AIS的物理层协议,本文首先分析了AIS中频收发信机的信号处理原理,然后论述了基于FPGA的AIS中频收发信机的硬件组成、软件流程和具体实施方案,以实现一路TDMA突发中频信号的发射和两路TDMA突发中频信号的并行接收。

2 相关理论分析

2.1 AIS物理层结构

AIS是以自组织时分多址(SOTDMA)协议为核心技术的TDMA通信系统,工作于半双工方式。AIS使用的物理信道为海事VHF87(161.975 MHz)、88频道(162.025 MHz),该信道在时间上被划分成固定长度的时隙(SLOT),一分钟为一帧(FRAME),一帧包含2 250个时隙,每个时隙长26.67 ms,时隙的划分是以GPS的秒脉冲为基准的。本地组网的各AIS设备在SOTDMA协议所预约的时隙内,交替使用海事VHF87、88频道发射自己的信息包(Packet),而在其余时隙则在这两个频道上同时静默接收其它船舶发送的信息包[1]。

AIS中频收发信机使用BbTS=0.3或0.5的GMSK调制方式,数据编码方式为不归零倒置(NRZI)码,码速率为9.6 kbit/s,而且工作于突发模式;AIS有效数据按HDLC协议组包,一个发射时隙内的AIS信息包最多含248 bit,其组成如图1所示。

训练序列24 bit起始标志8 bitAIS有效数据168 bit帧校验序列16 bit终止标志8 bit缓冲24 bit

训练序列为24 bit的01交替序列;起始、结束标志为8 bit的01111110;帧校验序列(FCS)使用CRC-CCITT-16格式,其生成多项式为x16+x12+x5+1=0x8408。

2.2 GMSK信号分析

2.2.1GMSK信号的数学描述

假设原始的输入基带数据流{dk}为双极性(+1或-1)的二进制NRZ信号,传输速率为fs=1/Ts,Ts为符号周期。经差分编码并取反后,得到待发送的基带数据流{ak}。

GMSK调制所用高斯低通滤波器的传输函数为

H(f)=exp(-α2f2)

(1)

式中,α是与滤波器3 dB带宽Bb有关的一个系数,α=(ln2/2)1/2/Bb。H(f)对应的冲激响应为

(2)

a(t)经过预调制高斯滤波器赋形后,得到:

(3)

式中,g(t)为高斯低通滤波器的矩形脉冲响应。当BbTs=0.3、0.5时,g(t)波形能量主要集中在±2.5Ts的范围内[2],故可将g(t)截断为5Ts宽度。

GMSK信号是用频率来传递信息的2FSK信号的特例[3],可表示为

S(t)=cos[ωCt+φ(t)]

(4)

式中,kTS≤t<(k+1)TS;ωC=2πfC,fC是载波频率;φ(t)为瞬时相位,

(5)

由式(5)可知,高斯滤波赋形后的相位积分使得GMSK信号具有连续平滑的相位轨迹,从而改善了其频谱特性,降低了带外辐射。但由于高斯低通滤波器的冲激响应h(t)在时域上是无限扩展的,双极性码元序列{ak}通过高斯低通滤波器后产生拖尾现象,相邻脉冲之间有重迭,导致g(t)在时域上也是无限扩展的,因此GMSK信号中存在由于高斯低通滤波引入的码间串扰[4]。

为了实现中频数字化的调制、差分解调(DPD),需要把文中所述的各公式转化为离散形式。在此过程中,除按采样定理完成各信号的离散化之外,还要把公式中的积分转化为合适的数值积分。

2.2.2GMSK调制及上变频

按式(5)计算得到φ(t)后,令SI(t)=cosφ(t),SQ(t)=sinφ(t),再按式(6)计算,可得到发GMSK中频信号为

S(t)=SI(t)cos(ωCt)-SQ(t)sin(ωCt)

(6)

2.2.3下变频

经过存在视距传播途径的VHF无线信道传输后,接收机前端输出的GMSK中频信号可表示为

R(t)=cos[(ωc+Δω)×t+φ′(t)]+n(t)=

(7)

式中,Δω为由于多普勒频移、收发端载频的固有频差和相位噪声等原因导致的收发端载频频差;φ′(t)为收GMSK中频信号的瞬时相位;n(t)为带限后的高斯白噪声。

多普勒频移是收发端载频频差Δω的主要组成部分。由于海事船舶、基站之间的相对移动而产生的最大多普勒频移Δf可表示为

(8)

式中,v为相对移动速度,C为真空中的光速,f为工作载频。在海事应用中,当v=120 km/h、f=162 MHz时,Δf<200 Hz。

2.2.42bit差分解调

2 bit DPD的性能比1 bit的好[5]。令相隔两个符号周期的收GMSK中频信号瞬时相位变化量为Δφ′(t),且判决分量

(9)

Δ经过低通滤波后可得到d′(t),而且:

d′(t)=cos[Δφ′(t)]=cos[φ′(t)-φ′(t-2Ts)]

(10)

当位同步钟恢复后,在t=kTS时刻,

(11)

式中,πG/2为码间串扰[2]。当BbTS=0.3、0.5时,πG/2≤π/8,式(11)可简化为

(12)

3 设计实现

3.1 硬件设计

整机经指标论证和低成本设计的考虑,确定发中频信号的载频为48 MHz、收中频信号的载频为38.4 MHz。根据带通采样定理,可确定收中频信号的采样率;为保证GMSK基带赋形时的波形准确度和位同步钟的提取精度,可将基带信号的采样率定为符号速率的20~32倍。上述采样率的选取,对数字信号处理器件的高速运算性能提出了一定的要求。

AIS中频发信机主要由FPGA和AD9767、U2793B组成,后两者组成正交调制电路。而AIS中频收信机主要由FPGA和AD9244组成,其中FPGA完成主要的信号处理功能。与DSP或ARM相比,FPGA更适合于并行的定点算法实现。本设计中的FPGA选用Xilinx公司专用于低成本信号处理的XC3S-3400A,可稳定工作在250 MHz时钟下,完全能够满足本设计的要求。

根据收中频信号的动态范围(-10±15 dBm) 和采样率,选择14位、最大工作速率为65 MSPS的AD9244为 A/D变换器。

为减小I、Q通道的幅度和相位不一致性,选用双通道的AD9767。AD9767为14位、最大工作速率为125 MSPS的TxDAC+类型的D/A变换器,它将数字形式的基带I、Q信号转变为模拟形式,送给U2793B进行正交调制,U2793B的本振工作范围为30~300 MHz。

3.2 AIS中频发信机

3.2.1实现方案

送入AIS中频发信机的基带数据,在SOTDMA协议预约的时隙内,形成突发GMSK中频信号。该发信机的实现结构如图2所示,其中虚线框内的部分在FPGA中实现。

图2 AIS中频发信机的实现结构

产生GMSK中频信号的关键点之一,在于高斯低通滤波器的实现。在本设计中,BbTS的取值为0.3或0.5,高斯低通滤波器使用FIR逼近的方式实现。

图2中的FM基带调制由DDS调制器实现,它将高斯赋形滤波器的输出作为自己的频率控制字进行相位累加,生成瞬时相位φ(t)。

3.2.2软件流程

突发GMSK信号的发射流程如图3所示。整个发射过程可以分成3个部分:开始时,待发送的基带数据经数据分段、差分编码和HDLC组包后,形成一个突发数据包,然后进入循环等待状态;当预约的发射时隙到来时,让该突发数据包通过高斯赋形滤波、DDS调制后形成瞬时相位φ(t);最后,根据φ(t)查sin表,得到GMSK基带信号的同相、正交分量,并经多级内插及滤波后,以数字的方式并行输出。上述的整个过程由FPGA程序来处理。

图3 突发GMSK信号的发射流程

3.3 AIS中频收信机

3.3.1实现方案

AIS中频收信机中有两路并行的接收通道。接收的GMSK中频信号经带通采样后,送往FPGA进行前导字检测、数字解调等处理,其中一路接收通道的实现结构如图4所示。

图4 AIS中频收信机的实现结构

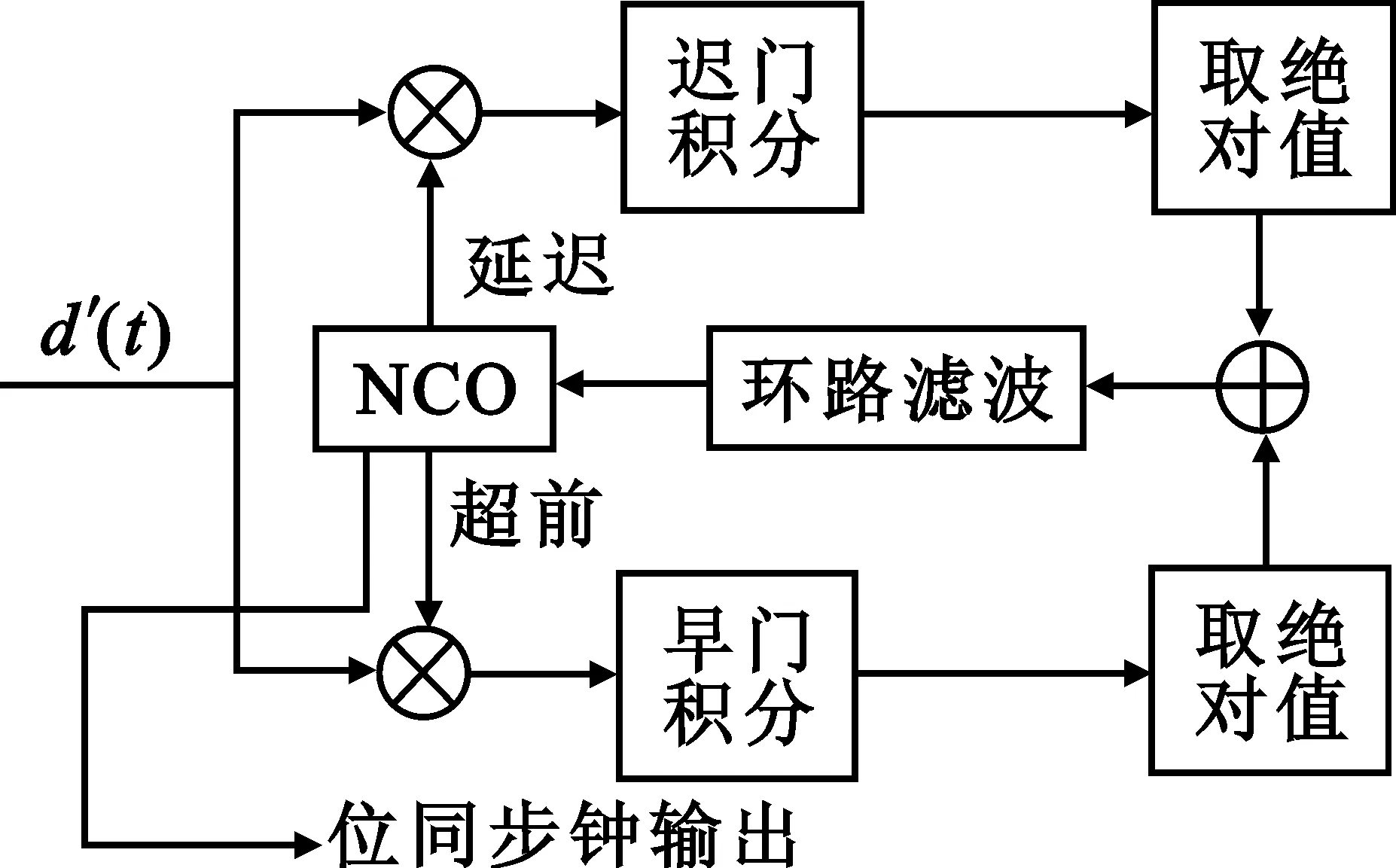

在按式(10)计算得到的d′(t)中,含有位同步钟的频率分量,可用经典的早-迟门积分环提取[7],其环路结构如图5所示。

图5 早-迟门位同步环

为保证所提取的位同步钟的精度,并考虑到环路的锁定时间应小于训练序列中8 bit的持续时间,d′(t)的采样率可取为符号速率的20倍左右。

在突发GMSK信号的接收过程中,需要确定AIS信息包的起始位置(即前导字的位置),以便从中提取有效的AIS数据。将差分解调后的信号d′(t)与本地的同步序列进行相关,根据相关峰的位置,可确定AIS信息包的起始位置。如果本地的同步序列仅由训练序列构成,则相关峰中存在凹点,影响相关峰的位置判决;而将训练序列加上起始标志作为本地的同步序列参与相关运算,可得到无凹点的相关峰。

3.3.2软件流程

突发GMSK信号的接收流程如图6所示。整个接收过程可以分成3部分:开始时,接收机处于信号侦收状态,通过相关计算检测是否有突发GMSK信号到达;当检测到突发GMSK信号并且相关峰超过门限值时,启动位同步提取、差分解调程序,同时记录此时的时隙标签号;然后对解调得到的数据进行CRC校验,如果结果正确则进行HDLC解包并加时隙标签后输出,反之则丢弃该数据包。上述的整个过程也由FPGA程序来处理。

图6 突发GMSK信号的接收流程

4 实验与分析

研制出的AIS中频收发信机如图7所示。用RS公司的FS-IQ7信号分析仪测试,该AIS中频发信机输出中频信号的眼图如图8所示,所得测试指标符合要求[1],其中EVM≤3.5%。如果将正交调制器集成在FPGA内,可改善至EVM≤2.5%,但“多级内插及滤波”环节将耗用较多的FPGA内部资源。因此从成本考虑,采用了外部的正交调制器。

用Agilent公司的E4433B信号发生器和误码率测试仪AV5237进行测试,AIS中频收信机在规定的信噪比、信号幅度及频偏(±1 kHz)的情况下,可达到小于等于10-4的误码率指标。

图7 AIS中频收发信机实物

图8 输出中频信号的眼图

5 结 论

利用本文所介绍的方法研制了AIS中频收发信机,与以往的AIS设备相比,实现了符合AIS物理层协议的突发GMSK信号的中频数字化调制解调。实验结果证明,该中频收发信机的各项技术指标符合AIS物理层的要求,已成功应用于话数同传的AIS话数端机中。另外,在增加频偏校正环节后,本文对设计大多普勒频移的相关中频数字化设备具有一定的指导和参考意义。

参考文献:

[1] IEC-61193-2, Maritime navigation and radiocommunication equipment and systems-Automatic identification systems(AIS)[S].

[2] 张邦宁.GMSK信号相干解调及载波同步方法[J] .微波与卫星通信,1998(2):34-39.

ZHANG Bang-ning. Coherent Demodulation and Carrier Synchronization Method of GMSK Signal [J].Microwave and Satellite Communication,1998,32(2):34-39.(in Chinese)

[3] 王士林,陆存乐,龚初光.现代数字调制技术[M].北京:人民邮电出版社,1987.

WANG Shi-lin,LU Cun-le,GONG Chu-guang. Modern Digital Modulation Technique[M].Beijing:The People′s Posts and Telecommunications Press,1987.(in Chinese)

[4] 叶丽艳,吴中一.GMSK基带信号的分析及改进[J].微波与卫星通信,1997(2):27-31.

YE Li-yan,WU Zhong-yi.Analysis and Amelioration of GMSK Baseband Signal[J].Microwave and Satellite Communication,1997,31(2):27-31.(in Chinese)

[5] Marvin K S, Charles C W. Differential detection of gaussian MSK in a mobile radio environment[J].IEEE Transactions on Vehicular Technology,1984,33(4):307-320.

[6] 杨小牛,楼才义.软件无线电原理与应用[M].北京: 电子工业出版社,2001.

YANG Xiao-niu,LOU Cai-yi.The Principles and Applications of Soft Defined Radio[M].Beijing: Publishing House of Electronics Industry,2001.(in Chinese)

[7] 陈玲,任重,夏俊.综合基带遥测单元信号同步的实现[J].电讯技术,2001,41(2):16-18.

CHEN Ling,REN Zhong,XIA Jun.Synthetical Baseband Remote Cell Signal Synchronous Realization [J]. Telecommunication Engineering,2001,41(2):16-18.(in Chinese)