一种高速跳频接收机的改进设计方案

罗红玲 ,尚海英 ,卜祥元 ,安建平

(1.福建省石狮电力有限责任公司,福建 石狮 362700;2.北京理工大学 信息科学技术学院,北京 100081)

飞行器制导接收机的任务是在飞行过程中不断接收导引指令,保证飞行器沿预定轨道飞行。由于对抗干扰、抗截获性能的严格要求,飞行器制导系统的通信体制目前都在向快速跳频(FH)的方向发展。同时由于制导接收机搭载在飞行器上,其体积和功耗受到了严格的限制。一般而言,根据跳频源的不同,传统的快速跳频接收机主要有两种实现方案:一种是基于多锁相环(PLL)频率合成跳频源的方案,其主要优点是可工作在高的本振频率,且功耗较低,缺点是受限于环路锁定时间而难以实现高速跳频;另一种是基于直接数字频率合成(DDS)跳频源的方案,其主要优点是频率转换时间短、容易实现高速跳频,缺点是DDS输出频率低,要工作在高的本振频率必须经过变频,这样就使其结构复杂,且功耗较高。另外,由于DDS输出杂散抑制差,接收机的性能也受到一定影响[1]。

本文提出了一种利用接收机前端双PLL和基带DDS共同实现高速跳频的改进设计方案,给出了一种基于高速跳频体制的飞行器制导接收机方案,实验结果表明,改进方案较好地解决了本振泄漏问题和I、Q两个通道的平衡问题,提高了系统性能。

1 系统特点和实现方案

飞行器制导系统的主要特点是必须具有优良的抗干扰、抗截获性能,同时制导接收机的体积和功耗严格受限。

采用直接序列(DS)扩频/快速跳频混合扩频体制是提高抗干扰、抗截获性能的有效途径。直接序列扩频信号具有较好的抗宽带干扰能力,而快速跳频信号具有较好的抗窄带干扰能力,DS/FH混合扩频体制在同时兼容DS系统和FH系统抗干扰、抗截获能力的同时还克服了单纯DS系统的远近效应问题。跳频速率对DS/FH混合扩频系统的抗干扰、抗截获能力具有决定性的影响。

制导通信系统采用了FH/DS/MSK混合扩频调制体制。其主要性能指标如下:

工作频段:1.7 GHz~1.9 GHz

工作体制:FH/DS/MSK

跳频范围:200 MHz

跳频点数:200个频点,间隔1 MHz

跳频速率:76 000跳/s

码片速率:5 Mb/s

为了满足体积和功耗的要求,制导接收机放弃了“DDS跳频+二次变频”的超外差方案,而采用“双 PLL跳频+基带数字跳频”的直接下变频方案,利用双PLL频率合成和基带数字部件共同实现76 000跳/s的跳频速率。整个接收机包括射频前端、基带数字信号处理和电源部分,其体积为 120 mm×60 mm×30 mm。

利用双PLL和基带数字部件共同实现高速跳频的方法是分组实现跳频,即将200 MHz频带内的跳频频点分成若干组,也即若干个子频带,每个子频带带宽40 MHz,包含40个跳频频点(频点间隔1 MHz)。子频带之间可以重叠或不重叠。首先由双PLL实现2 000跳/s的子频带跳变,再由DDS在0.5 ms时间间隔内实现子频带内40个频点间的38次跳变,实现76 000跳/s的跳频速率。

2 高速跳频制导接收机总体设计

2.1 接收机结构

接收机采用直接下变频拓扑结构,将接收到的射频调制信号直接进行一次性下变频解调,从而得到基带输入信号。由于省去了中频变换环节,能够大大减少外围元器件数量、印制电路板面积和功耗,但需要解决好本振泄漏问题和正交数据解调时I、Q两个通道的平衡问题。

图1是制导接收机组成框图。

跳频频率范围为1.7 GHz~1.9 GHz的射频调制信号从天线输入,其输入电平范围约为-97 dBm~-27 dBm。为了降低整机的噪声系数,首先经过低噪声放大器进行适当增益放大,再经过中心频率为1.8 GHz、带宽为200 MHz的带通滤波器抑制带外噪声后送给具有自动增益控制功能的射频放大器放大,然后进行直接下变频,其中AGC电压取自下变频信号的检波输出。下变频电路带有对本振进行±45°移相的功能部分,直接下变频后输出正交的两路基带信号,经过低通滤波和放大后送给A/D变换器,其幅度可通过AGC起控点的调节来控制,以满足A/D变换器的要求。基带数字信号处理部分由300万门的FPGA构成,完成跳频同步、DS解扩、MSK解调和信道解码等功能。

FPGA产生跳频同步控制信号和ADC采样时钟,与MCU通过高速SPI接口和外部中断接口进行控制信息的交换。MCU接收到起跳时间和预置频率的初值后,控制频率综合器产生所需的本振信号,送给下变频器。为了满足高速跳频的要求,采用双PLL频率综合器,以完成2 000跳/s的频率跳变。

2.2 接收机相关指标

(1)噪声系数 NF

噪声系数主要取决于射频前端第一级的增益或损耗。根据目前低噪声放大器的实际器件水平,考虑接头和馈线损耗,可取接收机噪声系数为NF≈1.5 dB。

(2)接 收 机 灵 敏 度 Pin,min

不考虑 DS扩频的因素,则码速率 Rb为 5 Mb/s(也即直扩后码片速率)。取成形滤波的滚降系数α=0.35,则实际中频带宽为:

虽然零中频带宽为40 MHz,但经过跳频同步和数字低通滤波后,实际带宽约为6.75 MHz。

对于MSK相干解调,误码率为10-4时,Eb/N0≈8.4 dB[2]。则所要求的接收机中频输出信噪比为

接收灵敏度

需要说明的是频率合成器相位噪声对接收机灵敏度的影响。相位噪声会限制接收机的信噪比,降低数字解调器的性能。当相位噪声恶化到一定程度时,即使不断增大信噪比,系统误码率也是不归零的,而是趋向于一个门限[3]。这时接收灵敏度已不再满足公式(3)。

(3)发射机输出功率

设系统备余量 E为 10 dB,收、发天线增益 Gt、Gr分别为0 dB和6 dB。

由于最大路径损耗:

故所需发射机输出功率为:

即10 W发射功率。

(4)动态范围

根据实际工程项目要求,信号视距传输距离d的范围为:100 m≤d≤80 km。

对应于最小接收距离dmin,其最小路径损耗为:

最强接收信号电平为:

最弱接收信号电平为:

动态范围为59 dB。实际设计时要留有抗衰落余量,根据所选器件的动态范围为69.5 dB,可取接收信号电平范围为-97.6 dBm~-28.1 dBm。接收机各部分的增益预算将按此电平范围来进行。

2.3 接收机内部增益预算

接收机内部各部分的增益预算如图2所示。

3 接收机前端的设计实现

3.1 低噪声放大器(LNA)

低噪声放大器按照噪声系数和增益兼顾的原则设计[4]。器件选用MGA-61563。其工作点选择为:Vd=3 V,Id=20 mA,输入、输出 50 Ω 匹配。

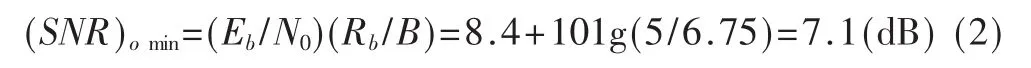

图3、图 4、图 5分别给出了 LNA的正/反向增益、噪声系数和输入/输出驻波比。

3.2 射频前端带通滤波器

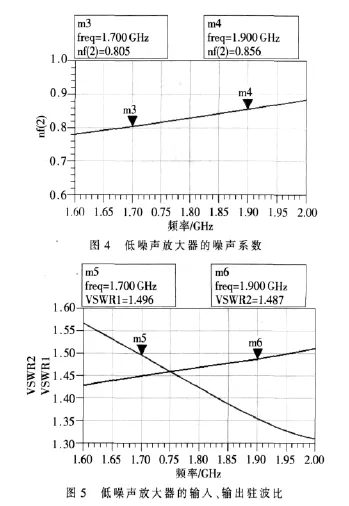

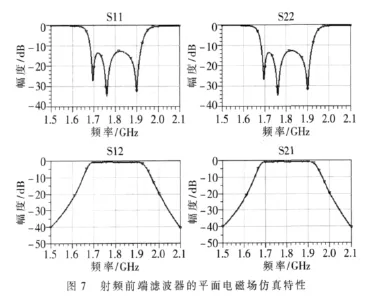

射频前端带通滤波器的指标如下:中心频率fo=1.8 GHz,带宽 BW-3dB=200 MHz,BW-40dB=600 MHz,插损约为1 dB,50 Ω匹配。采用发卡式(hairpin)平行耦合微带线设计,所占用的线路板面积为32 mm×22 mm。

图6、图7分别是hairpin滤波器的结构外形和平面电磁场仿真特性。

3.3 双PLL频率综合器

本振跳频源由双PLL频率综合器构成,采用温补晶振(TCXO)作为参考频率。由MCU控制射频开关以交替输出2个PLL综合的本振信号,跳频速率为2 000跳/s。采取如下的控制策略:

先对环1进行初始频率预置。在跳频切换时刻之前首先对环2进行下一时刻的频率预置,然后切换到环1的输出。如此循环往复,交替切换两个PLL的输出。

采用这种策略可以放宽对每个PLL锁定时间的要求,更好地保证了跳频源输出本振信号的杂散特性。图8是实测的PLL输出相位噪声和杂散特性。

频率综合器关键参数指标如下:

每个 PLL的环路带宽200 kHz,锁定时间小于 50 μs,

MCU频率预置时间小于 2 μs;

射频开关完成双环切换所需时间为几十纳秒[5]。

锁相环采用ADF4360-3,射频开关采用吸收式单刀双掷开关HMC349MS8G,隔离度约60 dB@1.8 GHz。

3.4 下变频器与自动增益控制

直接下变频器集成了可变增益放大器(VGA),其变换增益具有69.5 dB的动态范围,可与基带输出检波器一起实现自动增益控制功能。下变频器选用AD8347,其解调带宽90 MHz,I/Q幅度平衡度0.3 dB,正交相位误差典型值±1°[6]。

对高速跳频信号而言,AGC瞬态特性是一个非常关键的指标,必须减小电路时间常数,以保证能够及时跟踪输入信号幅度的变化。具体措施是减小VGA控制输入端的滤波电容值。

3.5 基带低通滤波和放大

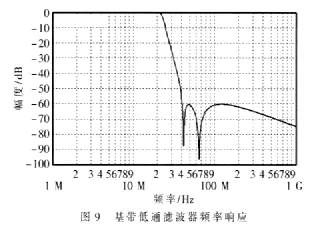

射频前端跳频同步后的I/Q基带信号带宽约为20 MHz,基带低通滤波器采用5阶LC椭圆函数滤波器的形式,L、C的值要精心选取,以满足 I、Q通道平衡和相位误差的要求。基带放大器采用AD8347内部集成的放大器,能够保证正交通道幅度的平衡。最终输出幅度可通过AGC起控点的调节来控制。基带低通滤波器的纹波为0.3 dB,放大器增益为30 dB。图9是基带低通滤波器的频率响应特性。

3.6 电路板的选材和布局

接收机射频前端部分单独采用一块电路板,面积为118 mm×58 mm。电路板采用4层设计,高频模拟部分单独占一面,MCU数字控制部分和电源部分占另一面。LNA部分和LO部分分别屏蔽处理。上、下两面电路板选用Rogers RO4350B板材,其介电常数在10 GHz以下时为3.48,损耗角正切为0.003 7[7]。中间使用FR4板材。

4 基带部分及其基本算法框架

基带数字信号处理部分主要包括FPGA及双路ADC。ADC采样时钟由FPGA提供,采样频率为80 MHz。基带数字信号处理算法均由FPGA完成。图10是基带数字信号处理的基本算法框架。

采用延迟锁定的方法实现跳频同步、DS扩频伪随机序列同步和MSK相干载波的同步。由于系统采用了多进制正交 DS扩频和(31,25)RS编码,对于 5 Mc/s的码片速率,达到的最高信息速率为625 Kb/s。

针对实际工程项目的需要,本文提出了利用双PLL和基带数字部件共同实现高速跳频的改进方案,确定了制导接收机相关指标参数,采用 “双PLL跳频+基带数字跳频”的直接下变频方案实现了76 000跳/s的高速跳频,同时兼顾了系统对体积和功耗的限制要求。设计的高速跳频制导接收机较好地解决了本振泄漏问题和I、Q两个通道的平衡问题,提高了系统性能。

[1]梅文华,王淑波,邱永红,等.跳频通信[M].北京:国防工业出版社,2005.

[2]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,1992.

[3]徐启刚,张辉.频率合成器相位噪声对跳频通信系统的影响[J].空间电子技术,2006(4):46-50.

[4](美)LUDWIG R,BRETCHKO P著.射频电路设计—理论与应用[M].王子宇,张肇仪,徐承和,等译.北京:电子工业出版社,2002.

[5]Hittite Microwave Corporation.HMC349MS8G/349MS8GE datasheet. v02.0607[EB/OL].2002.

[6]Analog Devices Inc.AD8347 datasheet[Z].2005.