氮化镓功率晶体管三电平驱动技术

任小永 David Reusch 季 澍 穆明凯 Fred C Lee

(1. 南京航空航天大学江苏省新能源发电与电能变换重点实验室 南京 210016 2. Virginia Polytechnic Institute and State University Blacksburg VA 24061)

1 引言

技术发展对功率变换装置的效率、体积、重量以及恶劣环境的适应能力的要求越来越高,Si MOSFET越来越难满足未来功率变换装置的要求,因此,氮化镓功率(GaN)晶体管应运而生[1-4]。

与Si和SiC相比,GaN的特征电阻要小得多(见图 1),其性能系数(Figure of Merit,FOM)FOM=RdsQg也远低于硅MOSFET,且其进一步减小的趋势十分明显,而硅已接近饱和。同时,GaN材料还具有良好的热性能[3,5,6]。GaN功率器件这些优点对功率变换装置性能的影响表现为效率的提升、体积的降低或是两者兼而得之。这对于应对目前的能源危机和原材料过度消耗问题,推进节能减排与可持续发展有着十分重要的战略意义和经济价值;同时,良好的化学稳定性以及耐恶劣环境能力使得GaN在未来航空、航天以及国防事业中的作用举足轻重。

图1 特征电阻对比Fig.1 Specific resistance comparison

由于GaN功率晶体管的开关特性、驱动技术及损耗机制相比Si MOSFET有显著差异,如何实现对GaN功率晶体管的驱动,对发挥其优势、提高系统整体性能十分关键。

目前,Si MOSFET的驱动方式可以归纳为PWM方式和谐振方式两大类[7]。其中,PWM驱动方式又可以分为集成式驱动和分立式驱动。集成式引起驱动结构简单、可靠而被广泛使用,尤其是对于互补开通的桥臂结构,集成驱动器既可以实现高可靠开通,又避免了桥臂直通[8]。然而,传统的PWM方式并没有考虑到控制死区时间对于开关管的控制,对于互补导通的桥臂结构,控制死区时间由开关管的反向导通机制实现电流续流。GaN功率晶体管由于没有体二极管,反向导通机制与Si MOSFET不同,其压降也远高于Si MOSFET体二极管的压降[2-4]。这对于高频工作的 GaN功率晶体管而言,若是沿用原有的 PWM驱动方式,死区时间的导通损耗将成为效率提高的致命障碍[4]。针对桥臂互补导通增强型GaN功率晶体管结构,美国国家半导体(现德州仪器)2011年年初刚刚推出一款集成的控制器 LM5113,该控制器实际上还是基于传统的PWM 方式,不同的是把死区时间设置的问题推给了逻辑控制电路,并没有从根本上找到死区时间反向导通问题的解决方案[9]。

针对 Si MOSFET的谐振式驱动是利用驱动回路的寄生电感或谐振电感与开关管结电容之间的谐振实现对开关管的驱动,通过回收驱动能量以降低驱动损耗[7,10]。而谐振式驱动电路本身并非无损的,其之所以能降低损耗实际上是节省了逻辑电路驱动损耗与功率电路驱动损耗之间的功耗差。这对于Qg比较大的Si MOSFET而言效果很明显,而GaN功率晶体管的Qg较小,谐振式驱动利用功耗差提高效率的优势显然不足[1-3,7,11]。另外,与 PWM 一样,在用于桥臂结构驱动时,谐振式驱动并没有考虑死区时间的控制。因此,有针对性的从GaN自身的特点出发,对能充分发挥其优势的驱动方案的研究势在必行。

本文将基于GaN晶体管的特性分析,并以GaN功率器件在同步整流 Buck变换器中的应用为例,提出一种三电平驱动方式,以充分发挥GaN功率晶体管器件的优越性。

2 GaN功率晶体管的特性

图2所示为IR公司GaN功率晶体管器件的结构图。由结构图可知,GaN功率晶体管器件栅极和源极是一个对称的结构,这与 MOSFET是不相同的。MOSFET的栅源极是不对称的,且由于结构材料特性,MOSFET中物理存在着一个寄生的二极管,俗称体二极管(body-diode)。显然,由于结构上的不一样,GaN功率晶体管中并不存在这样一个体二极管。

图2 GaN功率晶体管结构示意图Fig.2 Structure of GaN transistor

图3是增强型GaN功率晶体管的V-I特性曲线,图4为MOSFET的V-I特性曲线,图3和图4相比,在第一象限,两者的工作模式是类似的,但是在第三象限,两者工作模式则是完全不一样的。在给定的驱动电压下,MOSFET最大SD导通压降为二极管管压降VF,而 GaN功率晶体管则保持其在第一象限的恒阻特性。

图3 GaN功率晶体管V-I特性曲线(EPC1015)Fig.3 V-I characteristic curve of GaN transistor (EPC1015)

图4 MOSFET V-I特性曲线(IRF6618)Fig.4 V-I characteristic curve of Si-MOSFET(IRF6618)

在绝大多数的场合,主要关注功率晶体管在第一象限的特性,然而在一些需要反向导通机制工作的场合,如同步整流管(Synchronous Rectifiers,SRs)以及零电压开关变换器,则需要关注第三象限的特性。以同步整流管为例,其很重要的一个特性就是在驱动信号建立之前器件可以反向导通。对MOSFET而言,即体二极管在沟道开通之前导通。而GaN功率晶体管中并没有体二极管,在驱动信号没有建立之前,其反向工作机制能否建立是GaN功率晶体管能否在此类场合中应用的关键。

图5是GaN功率晶体管的等效物理模型,除了没有体二极管外与MOSFET类似。在作为同步整流管使用、且驱动信号还没有建立时,此时VGS为零,即可认为 G、S此时是短接的,电容CGD与CDS并联,当电流从S端流进,电流给电容CGD与CDS进行反向充电。由于GaN功率晶体管是一个DS对称的结构,当电容电压VGD充至门槛电压Vth时,沟道开始导通,而此时的导通压降VSD=VGD=Vth。即GaN功率晶体管反向导通机制是由于VGD到达开通的门槛电压,而不是体二极管,这一点与MOSFET不同,正是这种差异使得 GaN功率晶体管在驱动电压没有建立之前的反向导通压降远比 MOSFET的体二极管大。

图5 GaN功率晶体管等效物理模型Fig.5 Equivalent model of GaN transistor

当然,由于没有了体二极管,因此MOSFET作为同步整流管使用时的反向恢复问题在 GaN功率晶体管中不再是个问题。

3 传统驱动方式的问题

通常,为了保证电路可靠运行,避免直通问题,电路中互补工作的两只开关管在实际驱动工作时会预留一个死区时间,以确保电路安全可靠实行换流。以同步整流Buck变换器(见图6)为例,其主控管与同步整流管的驱动之间也同样存在这样的死区时间,在控制死区内,电流通过同步整流管的反向导通机制进行换流。当变换器工作频率不高时,控制死区可以完全忽略;当变换器频率不断升高的时候,这个问题则会变得比较突出。从功耗的角度来看,这一段时间中损耗可以表达为

图6 同步整流Buck变换器Fig.6 Synchronous rectified Buck converter

显然,对于一定的死区时间,频率升高意味着损耗增大。由于开关管在不同负载条件下实际导通、截止的时间是不一样的,因此在实际的电路设计中,驱动的死区时间是按照最恶劣的情况来考虑的。以目前常用的单输入 Buck同步整流的驱动器为例,其设置的死区时间一般为20ns左右,这对于开关频率为500kHz左右的POL应用场合是合理的,但对于频率到MHz甚至10MHz而言,频率越高其对占空比的影响越恶劣[7,10]。而GaN功率晶体管的优势在于兆赫兹的高频应用场合。换而言之,在GaN功率晶体管电路中沿用目前的 Si MOSFET集成驱动方式显然不可取。

在死区时间更小的新一代驱动器出来之前,简单可行的方案无疑是采用双输入的驱动器,通过控制两个输入信号的逻辑时序达到最小化死区时间的目的,以降低GaN功率晶体管在死区时间的损耗。这种做法可以有效的减小死区时间,但由于开关管导通、截止的时间受负载电流的影响,要时刻都能满足死区时间最小就必须实现对输入信号的逻辑时序进行实时调整,这对于POL这样一个小系统显然不太现实。下面将基于GaN功率晶体管的方向导通机制提出一种合适的驱动方式。

4 GaN功率晶体管的三电平驱动方式

图 7中,由KVL定律可知,GaN功率晶体管工作时三个结电容电压满足下列关系:

图7 GaN功率晶体管结电容电压的关系图Fig.7 Junction capacitor voltage of GaN transistor

显然,由这个表达式可以推得在驱动尚未建立,GaN处于反向导通时,由于VGS=0,反向导通压降就是加在栅漏极的驱动门槛电压Vth,即VGD=VSD=Vth。该反向导通机理也侧面验证了上面提及的GaN的对称结构,即无论GD或是 GS有驱动电压都可以实现开关管的驱动。按照这个逻辑,为了减小反向导通的压降VSD理论上存在下列三种可能:①VGS保持为零不变,降低VGD;②VGD仍为Vth,增加VGS;③增加VGS的同时降低VGD。

第①、第③两种可能性依赖于器件的改进,这主要是因为GaN功率晶体管反向导通时VGD实际就是器件的门槛电压。因此,真正可行的是第②种,也就是说,在驱动死区时间可以适当提高栅源极电压VGS(VGS<Vth),达到降低反向导通电压VSD的目的。值得注意的是,这里之所以要保证VGS<Vth,就是为了避免器件直通导致源短路。

基于上述分析,为了解决死区时间GaN功率晶体管导通损耗问题,可以在死区时间给 GS一个偏置电平Vgs_d=Vx(Vx<Vth,见图 8),这样相对于传统驱动方式的高、低电平而言,在原先两电平的基础上多了一个中间电平Vx。此时SD反向导通的压降有原先的Vth降低到Vth-Vx,理论上,当Vx接近Vth时开关管反向导通的压降为零,这将大幅度降低反向导通引起的损耗。

图8 Buck-POL中GaN功率晶体管三电平驱动策略Fig.8 3-level driving method for GaN in Buck POL

而由GaN功率晶体管的V-I特性可知,在驱动电压低于门槛电压时,开关管处于线性工作区域,此时开关管的阻抗相对较大,不会造成桥臂直通的问题,同时和上管交迭的导通时间很短,漏电流造成损耗相对于反向导通的损耗改善可以忽略不计。

5 实验结果

为了验证本文提出的三电平驱动方案,实验室完成了一台同步整流 Buck变换器原理样机,样机的参数为:Vin=12V,Vo=1.2V,Io=20A,V1、V2均为 EPC1015,Lf=150nH,fs=1MHz,td=15ns。

图9给出的是三电平驱动的电路图,图10给出的是相应的信号逻辑图。当 CON为低信号时,电路工作于两电平驱动状态。原理样机如图11所示,需要说明的是,为了降低实验的难度,V1与 V2采用了相同的器件。

图9 三电平驱动电路Fig.9 3-level driving circuit diagram

图10 三电平驱动电路信号逻辑顺序Fig.10 Logic signal consequence for 3-Level driving circuit

图11 原理样机照片Fig.11 Prototype picture

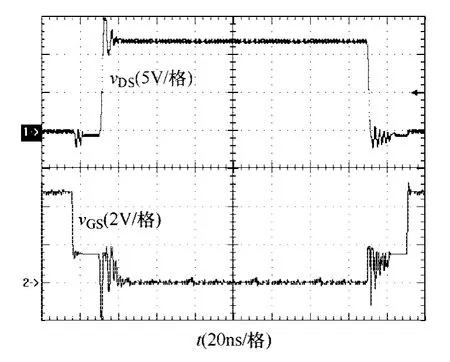

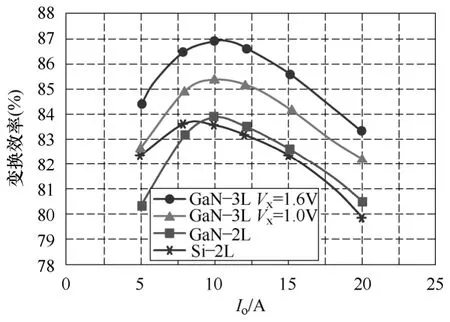

图12和图13给出的是两电平和三电平驱动是的栅源极电压和漏源极电压形,由于GaN功率晶体管体积太小,这里没有测试漏极电流。从实验波形可以看出三电平驱动方式有效降低了 GaN功率晶体管反向导通压降。图 14给出的是样机在不同Vx下的效率对比。显然,在Vx<Vth的前提下,增大Vx意味着变换器效率的提高。

图12 GaN两电平驱动及DS电压Fig.12 2-level GS and DS voltage of GaN transistor

图13 GaN三电平驱动及DS电压波形Fig.13 3-level GS and DS voltage of GaN transistor

与此同时,为了比较GaN与Si MOSFET的性能,这里同样给出了一组优化设计的 Si MOSFET样机的实验结果,V1和 V2分别采用 TI公司的CSD16410和CSD16325,其余参数保持一致。在工作频率为1MHz时,GaN两电平驱动的满载效率要高于 MOSFET;但是由于其反向导通压降远大于MOSFET的体二极管压降,因此其轻载工作时的效率要远低于MOSFET。

图14 效率曲线对比Fig.14 Measured efficiency

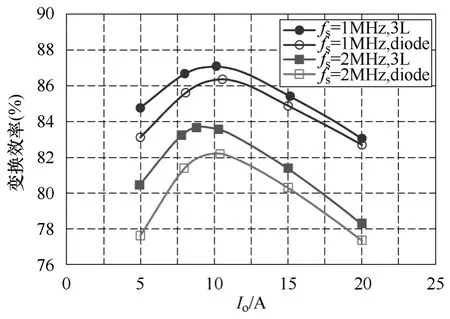

另外,为了证明驱动方法改进的必要性,将本文所提出的控制策略与 V2并联肖特基二极管的情形进行了对比。其中,Vx=1.5V,当开关频率上升到2MHz时,滤波电感减小到80nH,其余参数保持不变。图 15给出了效率曲线对比,在满载条件下,fs=1MHz时,三电平驱动方案比并联二极管方案的效率高0.3%;当频率上升到2MHz时,三电平方案的优势接近 1%。也就是说,随着频率上升,所提的三电平方案优势增大,这对于适用于高频开关的GaN功率晶体管而言是十分必要的。

图15 效率曲线对比Fig.15 Measured efficiency

6 结论

本文针对GaN功率晶体管在高频POL应用场合,基于对GaN电气特性的分析提出一种三电平的驱动方案以减小 GaN功率晶体管反向导通时的压降,从而达到改善变换器效率的目的。

实验结果表明,本文所提出的GaN功率晶体管三电平驱动方案对高频应用是有效且必要的,也将为 GaN功率晶体管的的广泛应用起到巨大的促进作用。

[1] Lidow A. Is it the end of the road for silicon in power conversion[R]. Application Note, Efficient Power Conversion Corporation, 2010.

[2] GaNPowIR—an introduction[R]. Presentation in IEEE Applied Power Electronics Conference 2010,International Rectifier, 2010.

[3] GaNPowIR update[R]. Presentation in IEEE Applied Power Electronics Conference 2011, IR Co., 2011.

[4] Colino S L, Beach R A. Fundamentals of galliun nitride power transistors[R]. Application Note,Efficient Power Conversion Corporation, 2010.

[5] Bhatnagar M, Baliga B J. Comparison of 6H-SiC,3C-SiC, and Si for power devices[J]. IEEE Transactions on Electron Devices, 1993, 40(1):645-655.

[6] Ikeda N, Kay a S, Li J, et al. High power AlGaN/GaN HFET with a high breakdown voltage of over 1. 8kV on 4 inch Si substrates and the suppression of current collapse[C]. Proceedings of IEEE International Symposium on Power Semiconductor Devices and IC′s 2008: 287-290.

[7] Zhang Z, Fu J, Liu Y, et al. A new discontinuous current source driver for high frequency power MOSFETs[C]. Proceedings of IEEE Energy Conversion Congress and Exposition, 2009: 1655-1662.

[8] ISL89163器件手册[Z]. Intersil, 2010.

[9] LM5113器件手册[Z]. Texas Intersil, 2012.

[10] Wang B, Tipirneni N, Riva M, et al. An Efficient High-Frequency Drive Circuit for GaN Power HFETs[J]. IEEE Transactions on Industry Applications, 2009 45(2): 843-853.

[11] 刘教民, 李建文, 崔玉龙, 等, 高频谐振逆变器的功率 MOS管驱动电路[J]. 电工技术学报, 2011,26(5): 113-118.Liu Jiaomin, Li Jianwen, Cui Yulong, et al. Power MOSFET gate driver of the high frequency resonant inverter[J]. Transactions of China Electrotechnical Society, 2011, 26(5): 113-118.

[12] EPC1015器件手册[Z]. Efficient Power Conversion Corporation, 2010.

[13] IRF6618器件手册[Z]. International Rectifier, 2008.