内串联型二极管封装产品研发

方逸裕,鄢胜虎

(汕头华汕电子器件有限公司,广东 汕头 515041)

1 引言

当前电子应用技术的发展趋势是电子电路的集成度越来越高,集成电路板上的空间越来越有限。同时,在半导体行业中,随着各种新型材料、技术的不断发展,二极管所需承受的反向工作电压也越来越高。但是由于半导体材料本身物理性能的局限性,其内部PN结所能承受的电压只能有限提高。随着国内外半导体市场的发展,电子电路应用设计过程中,电路中单个二极管需承受的电压值超过其最高反向工作电压的情况越来越多。通常情况下是采用两只或以上二极管串联分压的模式来解决该问题。运用这种解决方法,每增加一只器件,电路板上就需要增加相应的设计空间。如果能将两个或两只以上同等级或不同等级的二极管通过内串联的封装形式集成到一个产品里,则可以有效地解决电路设计空间的问题。

本文介绍一种新的封装半导体器件的研发,产品最终外形符合JEDEC的TO-220F-2L产品标准,如图1所示。图2为传统内部结构。本产品内部载芯板是分开的,可以装载两颗芯片,芯片间的连接以串联模式进行封装,如图3所示。封装后内部管芯之间具有3 500 V以上的绝缘耐压性能,芯片与外部的绝缘耐压性能也在3 500 V以上。以下介绍该封装产品开发过程中的重要技术难点和解决方法。

图1 TO-220F-2L标准产品

图2 传统二极管内部结构

图3 内串联二极管内部结构

2 研究内容

2.1 框架设计及风险评估

由于新产品功能对框架整体结构上有特殊要求要求,内串联型二极管封装产品外观符合JEDEC的TO-220F-2L产品标准,为保证产品外形尺寸满足客户要求,我们按保留要求外观尺寸的原则设计内串联二极管框架。

图4、5所示为内串联型二极管封装产品框架局部图。

图4 内串联型框架正面局部图

为满足客户 3.0 mm×3.0 mm的最大芯片尺寸要求,通过计算,内串联型二极管封装产品的载芯区整体宽度需要达到9.1 mm,如图7所示;而TO-220-3L产品为9.0 mm,如图6所示。该尺寸主要考虑要沿用原塑封模具的限制。同时该关键尺寸的增加会相应影响背面顶针孔附近和塑封体侧面的树脂体的充分填充,从而提高绝缘风险。通过反复计算和实验,最终认定对该关键尺寸微小调整(加大0.1)是可以接受的,产品失效风险仍然在可控范围。如图8所示,塑封后塑封体边缘尺寸可以达到要求。

图5 内串联型框架背面局部图

图6 TO-220-3L产品尺寸示意图

图7 内串联型二极管产品尺寸示意图

图8 内串联型二极管产品边缘尺寸示意图

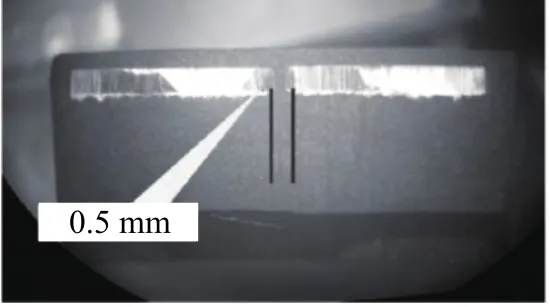

产品整体尺寸对两个载芯板之间的绝缘性能有相对影响,同时考虑到塑封过程环氧树脂粉的流动性和芯片尺寸对载芯板尺寸的要求。通过反复计算和讨论,最终载芯板间距的设计尺寸确定为0.5 mm。如图9所示。结构表面该设计尺寸可以满足产品的生产要求,图10所示为塑封后两载芯板之间树脂的填充情况。

图9 内串联型二极管框架载芯板间距示意图

图10 内串联型二极管两载芯板之间树脂填充情况示意图

考虑到产品的最大电流要求问题,设计方案要求引线框架能满足0.508 mm铝线的焊接。为满足该要求,新设计框架的管脚尺寸与TO-220-3L产生较大差异。 图11为TO-220-3L框架管脚外形和尺寸图,图12为内串联型二极管封装产品框架管脚外形和尺寸图。

图11 TO-220F框架

图12 内串联二极管框架

图13为所设计引线框架的外观总览图。

2.2 DIE BOND设备问题点及相关解决方案

2.2.1 存在问题

本产品上芯设备选用ESEC2007。因框架的结构问题,机台原装配套的上料真空管无法适用该框架,如图14所示。

图13 引线框架外观总览图

图14 原装上料机构

上料过程是利用真空吸附力完成框架的搬运。而正向串联的二极管结构框架的载芯板为拆分式的,如使用该真空吸杆及配套吸嘴,则会出现漏真空而导致框架搬运不良。

2.2.2 解决措施

重新设计一个上料真空管,并根据正向串联的二极管结构框架的关键尺寸选用合适的橡胶吸嘴,使得吸嘴能够完全吸附框架载芯板背面,完成框架搬运功能。备件如图15所示。

图15 改进后的上料机构

2.2.3 上芯过程产品质量标准及控制方案的制定

(1)焊料控制

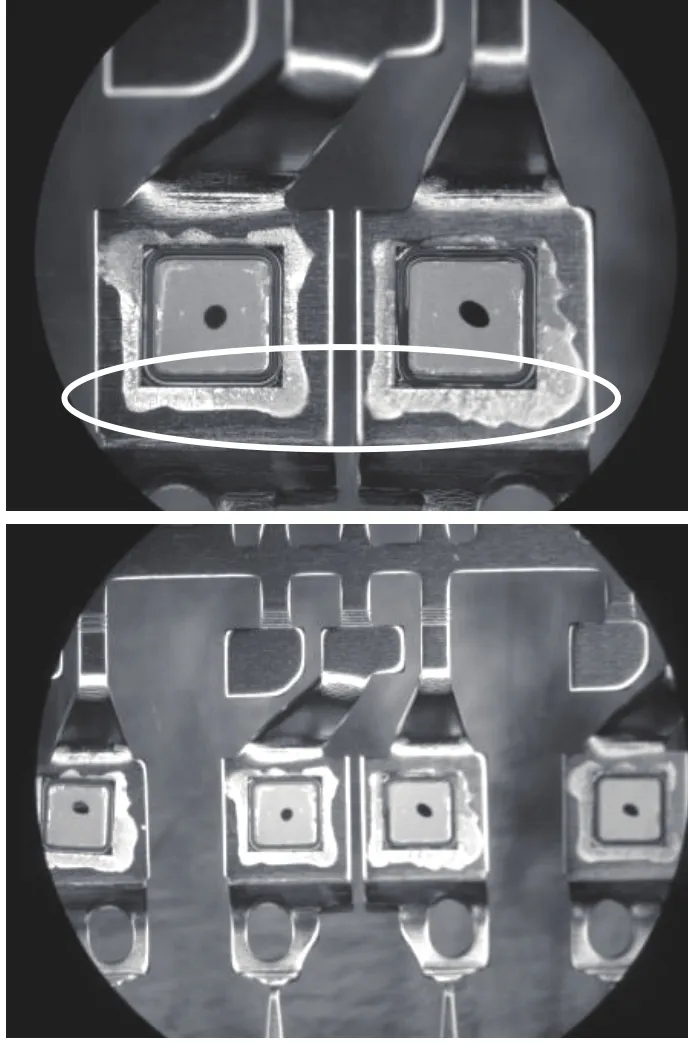

样品试验阶段,曾出现框架溢锡不良的问题,如图16所示。

图16 溢锡不受控情况

如图16所示,在单只产品两个载芯板之间,存在锡球,导致载芯板之间的距离变小,存在影响塑封过程环氧树脂粉流动性及塑封后绝缘不良的风险。

该问题可以通过合理规定上芯位置、并采用规定尺寸(2.5 mm×2.5 mm)的压模头解决。改善后图片如图17所示。同时将该内容列入质量标准,作为内串联型二极管封装产品的特殊质量标准。

图17 溢锡受控情况

(2)芯片的位置要求

为满足焊线工序压紧框架要求,确保压爪不会压伤芯片,如图18所示为由于芯片位置靠上导致焊线过程压爪压到芯片的情况。通过计算焊线压爪尺寸同时考虑公差,载芯板下端须留有宽度约为1 mm的压爪空间,如图19所示。

图18 压爪压到芯片

解决以上主要问题后,内串联型二极管封装产品的开发能顺利进行。样品试生产、验证,产品各项性能指标达到设计要求并通过客户认定及相关实验,转入正常批量生产。

图19 上芯效果图

3 结束语

内串联型二极管封装产品研发项目已成功完成。该项目突破了传统二极管的封装形式,在国内首创内串联式封装。同时该项目对引线框架进行自主创新,并申请了相关专利《一种正向串联的二极管框架结构》。该项目研发产品成本与国外知名半导体公司相比具有绝对优势,成本低23%,在国外市场上也具备一定的竞争力。

[1] STTH806DTI_07中文资料.