基于InP HBT的5 GS/s采样保持电路设计

罗宁,张有涛,李晓鹏,张敏

(南京电子器件研究所,南京211111)

基于InP HBT的5 GS/s采样保持电路设计

罗宁,张有涛,李晓鹏,张敏

(南京电子器件研究所,南京211111)

基于0.7 μm、ft=280 GHz的InP HBT工艺设计了一种双开关宽带超高速采样保持电路。芯片面积1.5 mm×1.8 mm,总功耗小于2.1 W。仿真结果表明,电路可以在5 GS/s采样速率下正常工作。当采样速率分别为5 GS/s和1 GS/s时,在输入信号功率为4 dBm的情况下,采样带宽分别为16 GHz和20 GHz;在输入信号功率为4 dBm且其频率小于5 GHz的情况下,电路的SFDR分别不低于43 dBc和50 dBc。

采样保持电路;超高速;宽带;磷化铟;异质结双极晶体管

1 引言

模数转换器(ADC)是模拟信号到数字信号的桥梁,被广泛应用于现代先进的电子系统。在无线通信技术飞速发展的今天,ADC不断向超高速方向发展,成为影响电子系统性能优劣的关键因素[1]。采样保持电路(THA)是ADC中最关键的部分,使模拟信号在转换为数字编码输出时保持不变,可以降低由于转换时钟沿偏离理想位置所引起的误差[2]。THA的速率和精度决定了整个ADC的速率和分辨率[3]。本文介绍了采样保持电路的整体结构、双开关THA的电路设计、输入输出缓冲电路的设计方法和时钟模式选择器CMS的工作原理。

2 电路设计

2.1 采样保持电路整体结构

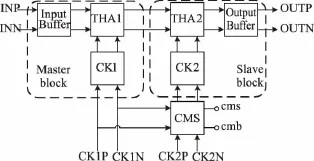

本文设计的采样保持电路框图如图1所示。电路包括输入缓冲器、输出缓冲器、2个采样保持电路核THA1和THA2、2个时钟缓冲器CK1和CK2和1个时钟模式选择器CMS。其中THA1和THA2是主从式结构,分别由CK1和CK2控制。而CK1和CK2的时钟输入信号由时钟模式选择器(CMS)控制。电路的全差分主从式结构方便性能指标的分别优化,主模块(Master block)主要负责优化线性度、带宽,减少抖动,从模块(Slave block)负责提高隔离度。

图1 采样保持电路框图

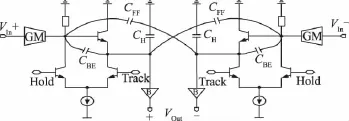

2.2 双开关THA电路

传统开关射极跟随器THA的简化电路如图2所示。图2在结构上最大的缺陷是保持模式下的馈通效应。馈通由采样开关管的固有寄生电容CBE引起,可以通过在采样开关的输出端和差分输入端之间加去耦电容CFF的办法来抑制馈通,但是这种抑制的效果取决于CBE和CFF的匹配程度[4]。另外,CBE的非线性会削弱匹配程度,带来非线性信号的馈通,这更加减弱了CFF抑制馈通的效果。传统开关射极跟随器THA也会因为开关操作导致的采样电容CH上采样电压值的变化而引入基座误差(Pedestal Error)。

图2 传统THA的简化电路图

与传统THA相比,本文设计的THA可以在保持模式下关断输入缓冲器与采样开关之间的通路,从而提高了隔离度,有效抑制馈通,并通过增加反馈缓冲器来消除基座误差。

THA1和THA2的实现电路如图3所示。在采样周期,控制端T为高电位,H为低电位,Q2、Q3打开,Q1、Q4关闭,RL、Q3、Q5支路和RD、Q2、Q6支路有电流。输入信号通路连接真负载RL,采样开关管Q7对输入信号进行采样。在保持周期,H为高电位,T为低点位,Q2、Q3关闭,Q1、Q4打开,RD、Q1、Q5支路和RL、Q4、Q6支路有电流。输入信号通路连接伪负载RD,输入信号与采样开关彻底断开,从根本上抑制了馈通。

图3中的反馈缓冲器B1可以有效地消除基座误差。没有B1的电路从采样态切换到保持态时,采样管Q7基极电压的共模电平从采样态的VCM1下降到保持态的VCM2。在保持态,为了提高隔离度,输入信号与真负载RL断开,RL上的差分电流衰减为零,开关管的输入差分电压衰减为零。最终,开关管的输入差分电压(Vb+和Vb-)在从采样态到保持态切换时经历不同的跳变。没有反馈缓冲器B1时从采样态切换到保持态的Vb+和Vb的变化曲线如图4(a)所示。不同的跳变ΔV1和ΔV2必将导致基座误差的产生。

图3 双开关THA简化电路图

当THA加上反馈缓冲器B1后,在保持周期,RL、Q3、Q5支路为RL提供的电流变为零,但是,由RL、Q4、Q6组成的反馈支路将为RL提供和采样周期电流一样的电流。因此,开关管的输入差分电压在切换时没有改变。有反馈的THA从采样态切换到保持态的Vb+和Vb-的变化曲线如图4(b)所示。在图4(b)中,Vb+和Vb-都经历了相同的跳变电压ΔV后到达低的共模电压VCM2。基座误差被明显抑制。

图4 双开关THA的开关管输入信号

图3中,采样电容CH及开关射级跟随电流ISEF是双开关型THA电路的重要设计参数,尽管本文采用的开关射极跟随器(SEF)结构有足够的开关速度和较高的线性度,但是SEF依然有结构上的局限性。由参考文献[5]可知,SEF的总谐波失真(THD)可以表示为:

fin为输入信号的频率,CH为保持电容,ISEF为SEF的偏置电流,A为输入信号的摆幅。本文设计指标是输入信号在奈奎斯特频率内,输入信号摆幅为1 VPP时,总谐波失真(THD)不大于-40 dB。指标确立后,由式(1)可知,THD为CH和ISEF的函数。增大CH会减小信号失真,但同时会减小带宽。

ISEF也可由公式(2)确定:

tHOLD是单个采样周期保持态的时长,tST是建立时间。

综合考虑带宽、线性度、功耗、噪声、下垂率等指标要求,最终本设计选择CH为300 fF,ISEF约为8.9 mA。

2.3 输入缓冲电路

输入缓冲电路的设计要求是大带宽、低噪声、高线性度。图5为本文的输入缓冲电路。输入端上拉50 Ω到地实现匹配,第一级起电平移位的作用,第二级主要负责提高线性度。非线性的产生是由于电路的增益随输入直流电平的变化而发生改变。即当晶体管基极直流电平发生变化,其VCE的值会随之改变,使晶体管的工作区域发生改变,导致了电路的非线性。本文提高线性度的方法如图5所示,Q1和Q2的基极电压均随输入信号变化而变化,三极管的VBE始终不变,因此Q1的VE即Q2的VC也随输入信号变化而变化,使得Q2的VCE保持不变,确保了Q2的增益不发生变化,有效提高了线性度。

图5 输入缓冲电路结构图

2.4 输出缓冲电路

输出缓冲电路的结构如图6所示。其主要作用是隔离并驱动后级电路。第二级与第三级与输入缓冲器的第二级类似,第二级通过电容负反馈拓展带宽,最后一级采用大尺寸晶体管提供大电流以驱动负载。输出端上拉50 Ω到地用以匹配负载。

图6 输出缓冲电路结构图

2.5 时钟模式选择电路(CMS)

由图1可知,时钟缓冲模块CK1和CK2均由时钟模式选择电路CMS控制。CMS有cms、cmb两个控制端,一共有4个控制态。CMS的真值表如表1所示。当cms接地、cmb悬空时,CK1和CK2控制THA1和THA2工作在全Track态,没有采样保持的作用;当cms接vee、cmb悬空时,CK1和CK2分别输入两种不同的时钟输入信号ck1和ck2;当cmb接地、cms为任意态时,CK1的时钟输入信号为ck1,CK2控制THA2工作于采样态,这种工作模式多用于测试;当cms和cmb均悬空时,CK1和CK2输入频率相同,相位相差180°的时钟输入信号,此工作模式为电路最常用的模式。在最后一种工作模式下,时钟周期被划分为两段,前半周期THA2采样THA1保持态的输出信号,后半周期THA2保持本级前半周期的信号。整个采样保持电路只输出保持模式的信号,方便了后级ADC电路的编译工作。

表1 时钟控制模块(CMS)真值表

3 仿真结果

电路采用0.7 μm InP HBT的工艺进行流片,芯片面积为1.5 mm×1.8 mm(包含压点),图7为芯片版图。芯片供电VEE为-5.2 V,总功耗小于2.1 W。图8为在5 GS/s采样速率下,输入摆幅为1 VPP、频率为1.3 GHz的正弦信号时的输出波形。图8从时域上表明电路实现了跟踪保持的功能。

图7 芯片版图

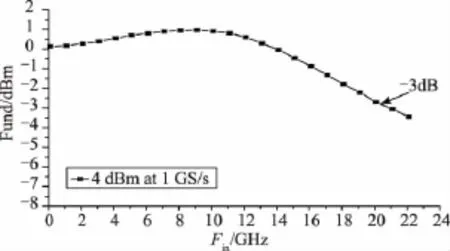

图9为5 GS/s采样速率下,输入不同输入功率时的采样带宽。由图9可得,在5 GS/s的采样速率下,电路的采样带宽为16 GHz。图10为1 GS/s采样速率下,输入差分功率为4 dBm时的采样带宽。由图10可知,在1 GS/s的采样速率下,电路的采样带宽为20 GHz。

图9 5 GS/s速率下不同输入功率时的采样带宽

图10 1 GS/s速率下输入差分功率4 dBm时的采样带宽

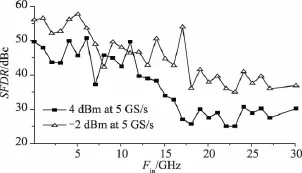

图11为5 GS/s采样速率下,不同输入功率下的无杂散动态范围(SFDR)曲线。由图11可知,输入1 VPP峰峰值信号(功率为4 dBm),当输入频率在5 GHz以内,SFDR不低于43 dBc,在整个带宽范围内,SFDR不低于30 dBc。输入0.5VPP峰峰值信号(功率为-2dBm),当输入频率在5 GHz以内时,SFDR不低于52 dBc,在整个带宽范围内,SFDR不低于42 dBc。

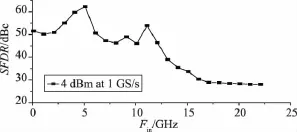

图12为1 GS/s采样速率下,输入差分功率为4 dBm的SFDR曲线。由图12可知,输入1 VPP峰峰值信号,当输入频率在5 GHz以内时,SFDR不低于50 dBc。

图11 5 GS/s下的无杂散动态范围(SFDR)曲线图

图12 1 GS/s下输入差分功率4 dBm的无杂散动态范围(SFDR)曲线图

4 结论

本文采用0.7 μm InP HBT工艺,设计了一种基于双开关结构的两级全差分采样保持电路,可有效抑制馈通,减小基座误差。仿真结果表明,电路可以在5 GS/s采样速率下正常工作。当采样速率分别为5 GS/s和1 GS/s时,在输入信号功率为4 dBm的情况下,采样带宽分别为16GHz和20GHz;在输入信号功率为4 dBm且其频率小于5 GHz的情况下,电路的SFDR分别不低于43 dBc和50 dBc。

[1]J Deza,A Ouslimani.70 GSa/s and 51 GHz bandwidth track-and-hold amplifier in InP DHBT process[J]. ELECTRONICS LETTERS,2013,49(6).

[2]潘星.一种基于SiGe BiCMOS的高速采样/保持电路的设计[D].重庆大学,2009.

[3]J Lee.A 6-b 12-GSample/s Track-and-Hold Amplifier in InP DHBTTechnology[J].ISSC,2003,38(9).

[4]H Dinc.A 1.2 GSample/s Double-Switching CMOS THA With-62 dB THD[J].IEEE JSSC,2009,44(3).

[5]J Dezaand,A Ouslimani.A 4 GSa/s,16-GHz Input bandwidth Master-Slave Track-and-Hold Amplifier in InP DHBT technology[C].The 20thTelecommunications forum TELFOR 2012,2012,Serbia.

Design of 5 GS/s Track-and-Hold Amplifier in InP HBT Technology

LUO Ning,ZHANG Youtao,LI Xiaopeng,ZHANG Min

(Nanjing Electronic Device Institute,Nanjing 211111,China)

The paper presents a double-switching,wide bandwidth,ultra-high speed track-and-hold circuit in 0.7 μm InP heterojunction bipolar transistor(HBT)technology.The area of the circuit is 1.5 mm×1.8 mm and the power consumption is no more than 2.1 W.Simulation results show that the proposed track-and-hold circuit is capable of operating under 5 GS/s.When the sampling rate is 5 GS/s and 1 GS/s with the input signal power being 4 dBm,the circuit sampling bandwidth is 16 GHz and 19 GHz,respectively.If the input signal power is 4 dBmandthe inputsignalfrequencyislessthan 5 GHz,the SFDRofthe circuitisno lessthan 43 dBc and 50 dBc.

Track-and-Hold Amplifier(THA);ultra-high speed;wide bandwidth;InP;HBT

TN402

A

1681-1070(2017)05-0020-04

罗宁(1992—),女,湖北襄阳人,2014年毕业于华中科技大学光学与电子信息学院,获学士学位,现为南京电子器件研究所在读硕士研究生,研究方向为高速数字电路和模数混合信号电路设计。

2017-2-7