非连续平面结构的电源完整性研究

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

非连续平面结构的电源完整性研究

尹学全,江肖力,韩 威,魏 浩

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

针对封装级多电源分配网络的噪声隔离难题,对封装级电源非连续平面结构的电源完整性进行了研究。建立了基于非正交三维空间变换的电源非连续平面结构等效电路模型,并运用保角变换等共形映射的方法进行了分离单元间互耦电容和电感的提取。基于本文建立的电路模型与提取的电路参数计算结果,设计了表贴式去耦电容的拓扑方案。最后,基于上述理论模型,采用LTCC技术和SiP封装技术,成功研制出了一款集成多电源的多功能模块。实测结果表明,研制出的模块的电源纹波小于10 mV,噪声隔离性能优异。

电源完整性;多电源分配网络;微元等效电路;保角变换;去耦网络;电源纹波抑制

目前,电源分配网络(Power Distribution Network, PDN)设计技术已成为混合信号系统设计的关键技术之一[1-4]。随着电子信息系统不断朝着小型化、高可靠性、高性能、低成本方向发展,对PDN的电源完整性提出了更高要求[5-6]。作为芯片级封装的核心部件,电源分配网络的输入阻抗特性及噪声的隔离度是衡量电源完整性的主要指标[7]。

对于微小型电子器件的PDN设计,增大其等效电路中的并联电容,能够降低宽频带范围内PDN阻抗,从而隔离噪声。并联电容的添加方式有电源平面结构分割、嵌入式电容集成[8]和表贴式去耦电容焊接[9]等。

建立PDN等效电路,是实现最优电容添加方案,进而实现PDN网络低阻抗的先决条件。

2011年,Jingook等[10]建立了一种多层PCB通孔结构中电源总线的等效电路模型,用于计算和分析板级PDN连续结构的阻抗等电路参数。

2014年,Zhao等[11]建立了一种基于mesh网格划分的单电源分布网络等效电路模型,用于提高大电流密度的TSV三维连接结构芯片可靠性。2017年,Nayak等[12]提出了一种基于非正交 2.5维空间变换和微单元分割的等效电路模型建立方法,用于分析封装级的电源完整性。

但是,上述方法均没有建立封装级电源非连续平面结构的等效电路模型,无法有效解决封装级多电源分配网络的噪声隔离难题。对于多电源非连续平面结构的等效电路模型以及建立模型应用于实际产品鲜有报道。为此,本文针对电源非连续平面结构建立了基于非正交三维空间变换的等效电路模型,通过保角变换等共形映射的方法进行了分离单元间互耦电容与互感的提取。基于本文提出的电路模型与电路参数计算结果,设计了表贴式去耦电容的拓扑方案。最后,采用LTCC技术和SiP封装技术,成功研制出了一款集成多电源的多功能模块,实测结果表明,基于本文提出的方法所研制的模块,其电源纹波小于10 mV,噪声隔离性能优异。

1 模型建立

本文设计的多电源的电源/地分割平面顶视图如图1所示。在图中,每个等分单元代表不同的电源顶层的分割平面。

图1 分割平面示意图Fig.1 The diagram of split plane

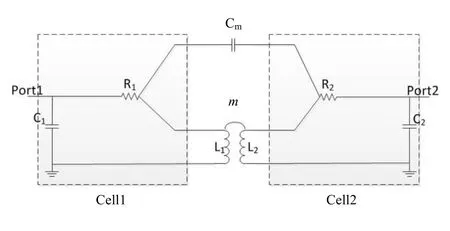

提取图 1中两个相邻平面间的电磁耦合如图 2所示,从图中可以看出,两个临近单元之间存在一个耦合电容Cm和互感系数为m的耦合电感。

依据电磁传输理论,结合单个平面的微元剖分等效电路,以及相邻平面的电磁耦合等效,建立电源非连续平面结构等效电路模型如图3所示。

图2 相邻两平面的电磁耦合图Fig.2 Electromagnetic coupling diagram of two adjacent planes

图3 电源非连续平面结构等效电路Fig.3 Equivalent circuit of power supply discontinuous planar structure

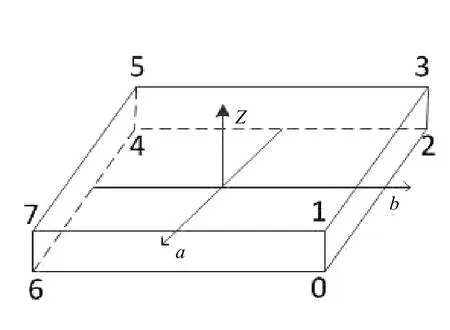

本文等效电路中的电阻R与电感L提取,采用非正交三维空间变换与有限元mesh网格剖分(如图4所示)的方法实现。首先,将单个平面mesh网格进行坐标变换[13],变换方法如公式(1)和(2)所示。

图4 网格剖分结构Fig.4 The structure of mesh generation

式中:a, b, c∈ [–1, 1];x, xk为坐标植及相应分值。

对于剖分单元的任意一点与原点形成的向量 r对于a方向的偏导有定义如下:

从而电流流向为a方向的电阻计算公式可表示:

电流流向为a方向的电感计算公式可表示:

式(5)、(6)计算了a方向的等效电路电阻电感参数值,可根据相同的原理方法计算出b、c方向的电阻电感值。

接地电容即为电源/地平面形成的电容,可表示为:

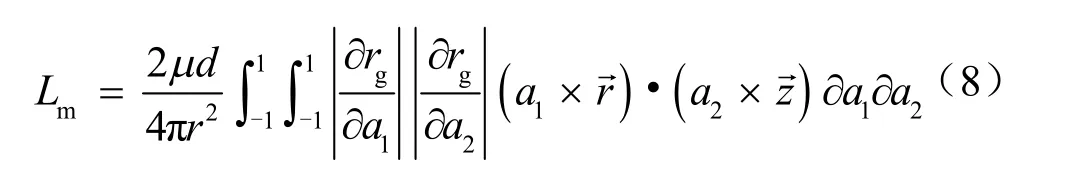

两分割平面的互感Lm可表示为:

两分割平面的耦合电容Cm可表示为:

基于以上等效电路模型以及模型参数的计算公式,考虑到两个分割平面之间的耦合参数影响,可以得到非连续电源/地平面结构电路的输入阻抗:

式中:ZL为相邻平面的等效阻抗值。

设计宽频带范围内低阻抗、高噪声隔离度的PDN网络,就是要使上述分析的输入阻抗满足低于特定的阻抗值,这个特定的阻抗值称为“目标阻抗”值, 即对于电源完整性分析,在特定输出纹波下,存在一个输入阻抗的最高值,只有当输入阻抗小于目标阻抗值时,电源输出纹波才能满足设计要求。

目标阻抗Z的计算公式:

式中:V为供电电压值;I为峰值电流值。

综上,芯片级封装的电子器件PDN可以通过优化电源平面分割结构,使阻抗值达到最小。但是,对于某些特定尺寸的电源平面,仅通过优化电源分割平面无法满足目标阻抗要求。因此,需要结合嵌入式电容或者表贴去耦电容进一步增大并联电容,以降低阻抗。考虑到工艺加工难度,本文采用表贴去耦电容的方法保证PDN电源完整性。

2 去耦电容拓扑方案

基于上述理论分析,首先选取最大最小电容,电容的谐振频率对应于需要抑制频段的最低最高频率,然后检测抑制频段内的高于目标阻抗值的频点,这些频点的阻抗局部最大值对应的频率就是上述理论分析的输入阻抗谐振模式的谐振频率。利用去耦电容‘V’形频率特性,即电容的容值以及其寄生电感值形成‘V’形的频响特性,在谐振频率处阻抗最小。添加谐振频率为阻抗局部最大值对应频率的电容,使得此频点的输入阻抗满足目标阻抗要求;连续利用此方法加入电容直到抑制频段内形成相对平坦的低阻抗带。即在抑制频带内输入阻抗符合目标阻抗要求。

3 仿真与分析

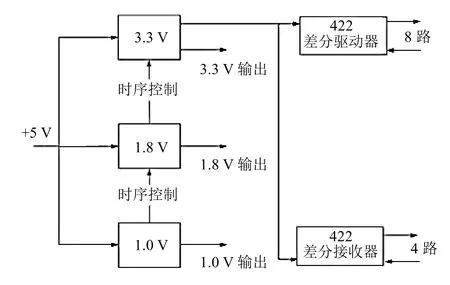

基于上述理论分析结论与方法,结合工程需要,采用LTCC技术和SiP封装技术,研制一款集成多电源的多功能模块,模块主要由稳压电路及422差分接收驱动电路组成。稳压电路的输入电压为5 V,输出电压有三种:开关稳压输出为1.0 V,线性稳压输出为1.8 V,3.3 V,并具有顺序上电功能;差分接收驱动电路提供4路差分接收以及8路差分驱动。具体电路原理图如图5所示。

图5 电路原理图Fig.5 The schematic diagram of the circuit

为了减小电路布局面积和提高微组装效率,采用LTCC一体化封装集成方案,节省外部封装所占用的体积。由于模块内部集成串口通信电路,且此部分电路封装体积小,容易引入串扰与电源噪声。为此针对模块非连续平面结构PDN中的3.3 V供电的422芯片进行电源完整性分析。422芯片峰值电流为260 mA。则得到目标阻抗为1.27 Ω。

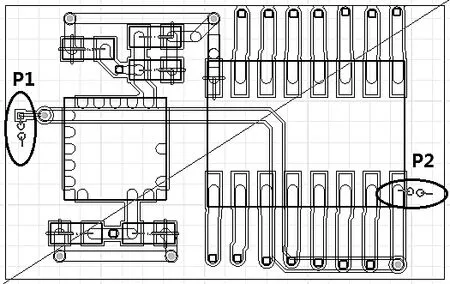

依据理论分析结论与实际产品方案布局,利用建立的电源非连续平面结构等效电路模型,分割电源平面使噪声抑制度达到最优,但仅通过此措施不能达到PDN目标阻抗要求,需根据上述介绍的去耦电容拓扑方法进行进一步优化。借助Designer分析软件可清楚地计算出PDN输入阻抗随频率变化的曲线,以及实时监测加入去耦电容的效果。将建立的模块PDN模型导入Designer软件中。并在电源链路两端加入端口P1、P2,其中P1为模块稳压电源输出口,P2为422芯片电源输入口,如图6所示。通过仿真可以提取出电源链路的二端口Z参数,如图7所示。

图6 电源链路端口示意图Fig.6 The diagram of power port

图7 阻抗曲线图Fig.7 The diagram of impedance curves

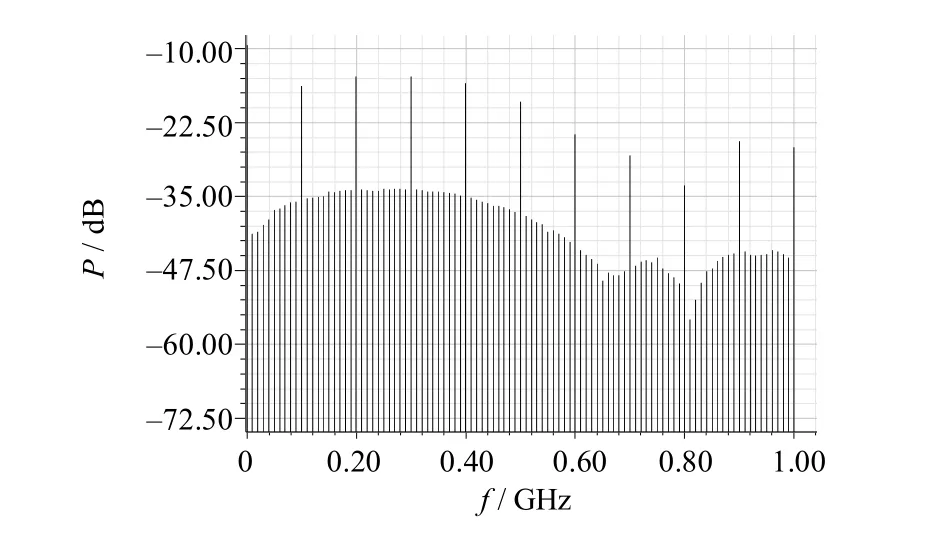

供电电源的纹波幅度大小可直观反映PDN电源完整性的优劣。为了监测现状态下的电源纹波幅度,将电源链路二端口的S参数模型及422芯片的IBIS模型导入Designer,在422芯片供电端口加入电压Vcc测试点,具体仿真示意图如图8所示。运行仿真得到422芯片电源的电压波形如图9所示,由图得到,电源电压纹波幅度峰峰值达4.5 V;电源功率频谱分布如图10所示。

图8 仿真原理图Fig.8 The schematic diagram of simulation

图9 电压波形图Fig.9 The voltage waveform

图10 功率频谱Fig.10 The diagram of power spectrum

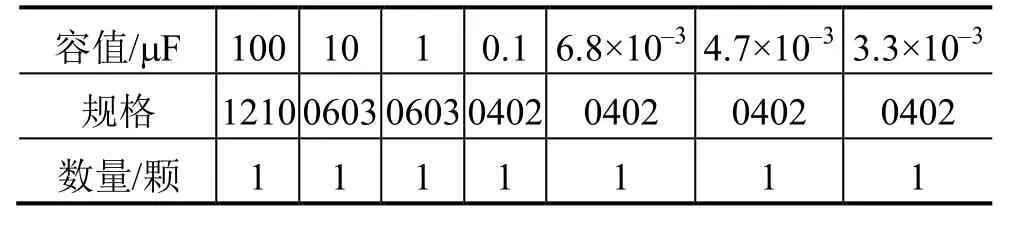

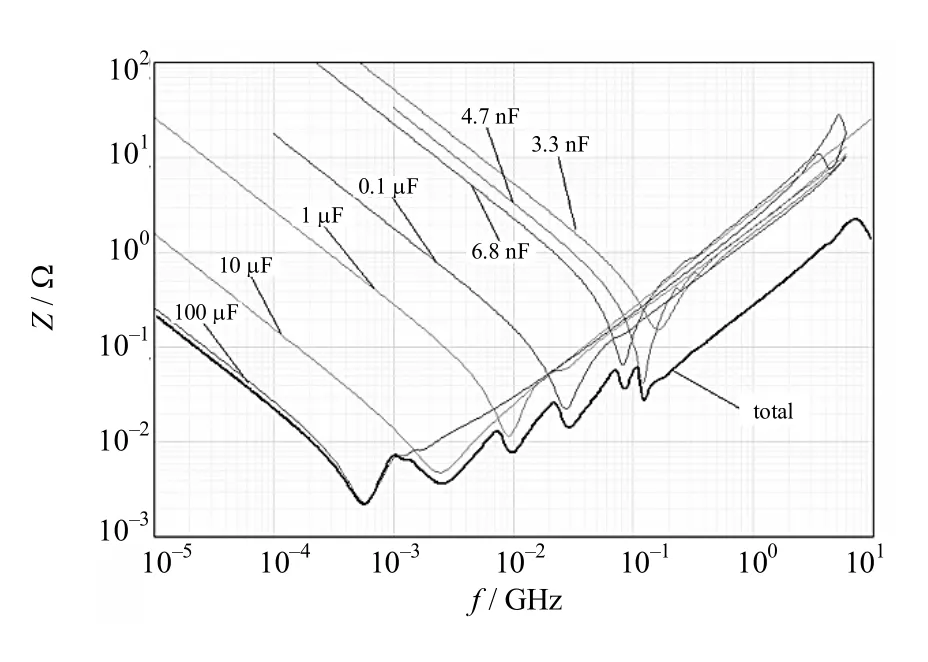

由图得到,频率低端存在较大的100 MHz及其倍频分量纹波,根据添加去耦电容理论分析方法,结合工程可利用的封装去耦电容。选取添加到供电网络的去耦电容如表1所示。添加电容的阻抗图如图11所示。

表1 选取电容列表Tab.1 List of selected capacitor

图11 电容阻抗曲线图Fig.11 The curves of capacitive impedance

将并联电容组加入到电源链路上。重新扫描并提取电源链路的S参数和Z参数,其中Z参数曲线如图12所示。

图12 阻抗曲线图Fig.12 The diagram of impedance curves

通过图中曲线可以看到:电源链路的阻抗在10 kHz~1 GHz范围内低于目标阻抗,满足阻抗要求。依据图 8再次进行仿真,得到的电源电压纹波为 7 mV,具体电压波形如图13所示。

图13 电压波形图Fig.13 The voltage waveform

通过以上的电源完整性仿真,利用介绍的去耦电容添加方法可以在有限的空间内实现控制电源纹波在10 mV以下,去耦效果较好。

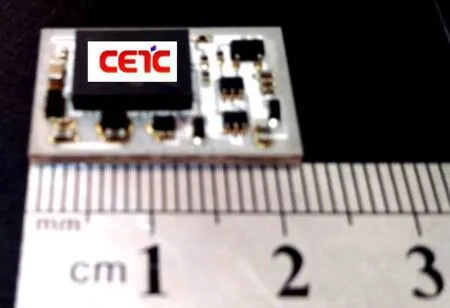

4 加工与测试

按以上方案设计的 SiP电源通信封装模块,尺寸为22 mm ×14 mm ×5 mm,与传统的采用混合电路技术制作的传统同类产品相比其体积缩小到约为原来的1/4,实物如图14所示。采用示波器、信号发生器等设备对 SiP模块进行高低温电性能测试,测试结果与电源完整性仿真相符。输出电压稳定,电压纹波在10 mV以下。测试电压波形图如图 15所示。

图14 产品实物图Fig.14 The photo of the product

图15 测试电压波形图Fig.15 Test voltage waveform

5 结论

本文建立了基于非正交三维空间变换的电源非连续平面结构等效电路模型,将分割平面间的电磁耦合效应寄生参数加入到等效电路模型中,进而推出电源平面的优化分割理论方法,且在此基础上介绍了一种进一步优化PDN的去耦电容添加方法。在理论推导、仿真分析以及实物测量方面验证了上述方法的正确性。该方法适用于多电源PDN设计。

[1] 郭广阔, 黄春跃, 吴松等. 基于HFSS的埋入式电容串扰分析 [J]. 电子元件与材料, 2014, 33(4): 60-63.

[2] SWAMINATHAN M, KIM J, NOVAK I, et al. Power distribution networks for system-on-package: status and challenges [J]. IEEE Trans Adv Packg, 2004, 27(2): 286-300.

[3] WANG C, MAO J, SELLI G, et al. An efficient approach for power delivery network design with closed-form expressions for parasitic interconnect inductances [J]. IEEE Trans Adv Packg, 2006, 29(2): 320-334.

[4] SWAMINATHAN M, ENGIN A E. Power integrity modeling and design for semiconductors and systems [M]. Englewood Cliffs, NJ, USA: Prentice-Hall, 2007.

[5] SWAMINATHAN M, CHUNG D Y, STEFANOG T, et al. Designing and modeling for power integrity [J]. IEEE Trans Electromagn Compatibility, 2010, 52(2): 288-310.

[6] ARAGA Y, MIURA R, NAGATA M, et al. A study on power integrity in a 3D chip stack using dynamic power supply current emulation and power noise monitoring [C]∥Electronics System-Integration Conference. NY, USA: IEEE, 2014.

[7] 李君, 寥成, 万里兮. 系统级封装的电源完整性分析和电磁干扰研究 [D]. 成都: 西南交通大学, 2010.

[8] WU T L, CHUANG H H, WANG T K. Overview of ower integrity solutions on package and PCB: decoupling and EBG isolation [J]. IEEE Trans Electromagn Compat, 2010, 52(2): 346-356.

[9] 周磊, 刘庆想, 张健穹, 等. 印制电路板去耦网络优化设计 [J]. 微波学报, 2014(6): 612-615.

[10] JINGOOK K, SHRINGARPURE K, JUN F, et al. Equivalent circuit model for power bus design in multi-layer PCBs with via arrays [J]. IEEE Microwave Wireless Compon Lett, 2011, 21(2): 62-64.

[11] ZHAO X, LIM S K. Analysis and modeling of DC current crowding for TSV-based 3-D connections and power integrity [J]. IEEE Trans Compon Packg Manuf Technol, 2014, 4(1): 123-133.

[12] NAYAK B P, GOPE D. Nonorthogonal 2.5-D PEEC for power integrity analysis of package-board geometries [J]. IEEE Trans Microwave Theory Tech, 2017, 65(4): 1203-1214.

[13] RUEHLI A E, ANTONINI G, ESCH J, et al. Nonorthogonal PEEC formulation for time- and frequency-domain EM and circuit modeling [J]. IEEE Trans Electromagn Compat, 2003, 45(2): 167-176.

[14] 彭大芹, 许海啸. 电源分配网络设计中一种新型的去耦电容选择方法 [J]. 广东通信技术, 2016(1): 76-79.

Power integrity study of discontinuous planar structure

YIN Xuequan, JIANG Xiaoli, HAN Wei, WEI Hao

(The 54th Research Institute of China Electronics Technology Group Corporation, Shijiazhuang 050081, China)

This paper thoroughly studied the power integrity of a discontinuous plane structure, which aimed at the problem of noise isolation for multi-power distribution network in package level. An equivalent circuit model, for discontinuous plane structure, based on nonorthogonal three dimensional space transform, was built. The mutual coupling capacitance and inductance among the elements were extracted by the conformal transform and conformal mapping. A topology scheme of decoupling capacitor was designed, based on the circuit model and the extracted parameters established in this paper. Finally, based on the above theoretical model, a multifunctional module was successfully developed using LTCC technology and system in package (SiP) technology. Measured results show that the power supply ripple of the module is less than 10 mV, and the noise isolation performance is excellent.

power integrity; multi power distribution networks; partial element equivalent circuit; conformal mapping; decouple net; power ripple suppression

10.14106/j.cnki.1001-2028.2018.01.014

TG434.1

A

1001-2028(2018)01-0071-06

国家自然科学基金资助项目(61404119)

2017-09-08

尹学全

尹学全(1990-),男,内蒙古宁城人,研究生,主要研究方向为信号与信息处理。

(编辑:陈渝生)