一款12 Bit 1 GS/s射频采样的流水线模数转换器设计

史帅帅,唐 鹤,武 锦,王 卓,张 波

(1.电子科技大学,成都 610054;2.中国科学院微电子研究所,北京 100029)

1 引言

高速高精度是数模转换器(A/D converters)未来发展不可逆转的趋势。在无线通信应用中,使用高速高精度ADC能够使通信基站拥有更加广泛的蜂窝网络覆盖范围,更强的用户量承载能力,也在一定程度上简化了无线通信系统的设计。一般来说,更高采样速率的ADC有更大带宽,可以简化前端的抗混叠滤波器,具有更高的灵活性。另外,射频采样可以降低系统的设计成本,同时提高系统整体性能和效率。

实现吉赫兹采样速率的ADC通常使用时间交织架构。然而这种架构存在通路之间的失调以及增益时序带宽不匹配的问题,这些问题也限制了数模转换器的性能和用途。虽然失调和增益的失配可以被有效校准,但是通道间时序和带宽的失配影响仍然是限制高频输入频率下ADC性能的主要因素[1]。

另外,流水线数模转换器结构已经被证明是高速高性能ADC很好的选择。但是,用流水线结构来实现12 Bit 1 GS/s的ADC仍然需要面对一些挑战。要在很短的时间内完成采样,需要更快的比较器,运放的建立时间也很紧张,出现了一系列实现高速高精度ADC将会遇到的问题。在先进的40 nm CMOS工艺下,器件的截止频率高达300 GHz,但是本征增益和输出电阻方面表现很差。在低电源电压下(1.2 V),使用传统的高增益高带宽的运算放大器来实现高速高精度的ADC是不可能的。

本文采用无采样保持放大电路(SHA-less),带正反馈电容的低增益高带宽高线性度的运放,并结合片外数字校准来实现一款12 Bit 1 GS/s的流水线ADC。

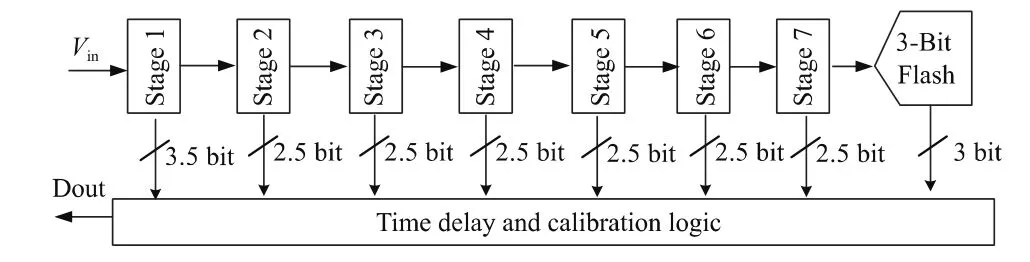

图1 流水线ADC的典型结构

2 传统流水线ADC的结构与工作原理

流水线ADC的典型结构大致如图1所示[2],一般包括以下几个部分:最前端的采样保持电路(Sample and Hold Amplifier,SHA)、中间部分的多级流水线级和最后一级的快闪式数模转换器(Flash ADC)。SHA把在时间上连续的模拟信号转化为在时间上离散的直流电平信号;中间部分的每一级流水线级都包括跟踪保持模块(Track and Hold,T/H)、子模数转换器模块(sub-ADC)、子数模转换乘法器(Multiplying Digital to Analog Converter,MDAC),其中包括子数模转换器(sub-DAC)和余量放大器(Residue amplifier,RA)。每一级流水线级的工作基本一致,以第一级为例:首先,输入信号被THA采样并保持;然后采样信号被Sub-ADC量化,并输出数字码;Sub-ADC输出的数字码即作为本级的数字输出Dout,同时也作为MDAC的输入,MDAC中的Sub-DAC根据数字码产生相对应的模拟输出;然后,采样信号与Sub-DAC的模拟输出做减法产生余量信号;最后,该余量信号被余量放大器(RA)放大并作为下一级的输入信号。后面的每一级都是在重复刚才所述的过程,在精确时序控制下,使每一级在采样量化和余量放大状态间来回切换,每一个时钟周期都有新的输出产生,只是从模拟信号的输入到产生与之相对应的数字输出之间存在延迟(latency)[3]。对于指定每一级量化位数越高,ADC总的级数越少,所需要的放大器个数越少,延迟也越低,但是最终会受到采样电路与放大电路的带宽还有电容失配等的影响,限制流水线ADC的速度和精度的极限[3]。

3 流水线ADC的设计

3.1 整体架构设计

由于满足更高的采样速率和采样精度要求的SHA会占据芯片更多的功耗和更大的面积。因此,一个简单有效的方法就是移除前端的SHA模块。如果没有SHA模块,输入与MDAC以及输入与Sub-ADC的采样电路网络需要匹配,否则MDAC和Sub-ADC对输入的采样可能并不是同一个值。假设MDAC与Sub-ADC采样时钟存在Δt的偏差,输入信号为正弦信号,频率为f,输入信号幅度为A,那么对应信号中MDAC和Sub-ADC所采样到的电压信号的最大差值为:

由于流水线ADC的结构优势,当此误差小于本级sub-ADC分辨率的0.5 LSB时,此误差可以被修正,对ADC整体性能没有影响。当输入信号的频率很高时,可能会导致流水线ADC产生错误的输出。但是这个失配所产生的误差可以等效到sub-ADC的失调中,因此采用具有冗余位(如3.5位/级)的结构可以在一定程度上容忍该误差。另外,还可以在两个采样通路的其中一路中的采样时钟里加入可调延迟模块[4]。

图2 本文所设计的流水线ADC架构图

本文中所设计的ADC架构如图2所示,第一级是3.5位每级,第二级到第七级是2.5位每级,最后一级是3位的Flash ADC。其中,第一级的有效量化位数是3,理想级间增益为4,输入范围是-0.6~0.6 V,因此第一级的输出范围就在±0.3 V以内,从第二级开始,后面每一级的量化范围是-0.3~0.3 V。

3.2 Sub-ADC的设计

Sub-ADC是流水线ADC的重要模块,通常由Flash ADC实现。

3.2.1 第一级Sub-ADC的设计

根据前面的分析,对于SHA-less结构的第一级设计而言,输入信号到MDAC以及Sub-ADC的路径匹配非常重要。所以本文中的Sub-ADC采用如图3所示的结构,使得MDAC和Sub-ADC在采样相时对输入信号而言采样路径几乎完全一样。

但这样的设计使得比较器必须有额外的时间对参考电压采样,因此我们使用占空比为25%~75%的时钟,分配前25%为输入信号采样,25%~50%为比较器对参考电压采样,而后50%为MDAC输出建立。实际大约230 ps的采样时间是相当短的,为了保证在低电源电压及高速应用下的线性度,所以此处采样相位Φ1所控制的开关是高线性度的自举采样开关。

如图3所示为本文设计的流水线ADC所采用的开关电容比较器结构。比较器由采样相时钟Φ1的提前相Φ1e触发。比较器的工作过程如下:(1)在保持相Φ2的下降沿,电容C的下极板断开连接,参考电压被采样保持在电容C上;(2)采样相Φ1时,电容C上极板连接输入信号;(3)比较器在Φ1e下降沿被触发并比较。因此,在两相时钟的不交叠时间里比较器需完成比较并产生输出,这对比较器的速度提出了要求。通过电荷守恒我们可以计算比较器开始工作时的两个输入端的电压差,在Φ2相时C上的电荷为:

在采样相Φ1时,C上的电荷为:

由于电路在Φ1和Φ2时电荷守恒:

本设计中利用电阻串分压产生所需的参考电压。

3.2.2 后级Sub-ADC的设计

对于流水线后级,由于采样信号都为前一级的输出电压,可以近似为直流电平信号,输入信号到MDAC以及Sub-ADC的路径匹配就不是那么重要了。然而,设计一款能够在100 ps左右输出结果的Sub-ADC面临很大的困难。与之前的SHA-less结构[5-6]相比,如果让比较器在MDAC余量放大阶段进行对参考电压的预充电,在采样相位连接到上一级流水线的近似于直流信号的输出,那么比较器可以在采样结束后马上就开始工作,相比于第一级结构中在所在的时钟周期内就少了一个电荷分配的时间,可以在很大程度上缓解比较器的压力。具体分析和第一级Sub-ADC类似,在此不再赘述。

图3 开关电容比较器

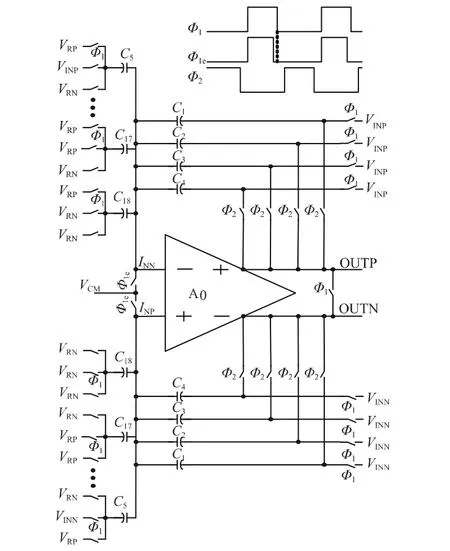

3.3 MDAC设计

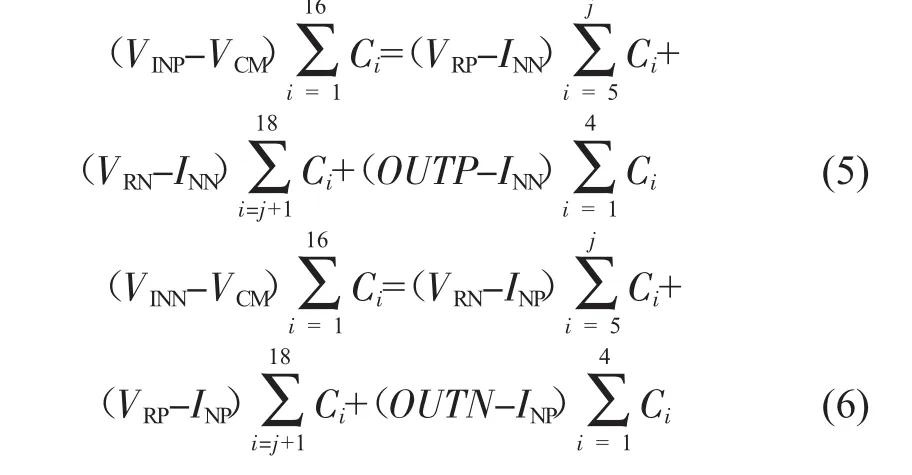

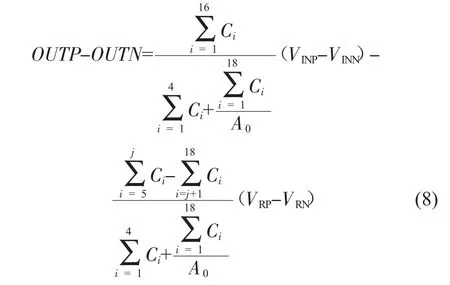

由前述可知,MDAC模块是流水线ADC中的关键模块,决定了ADC的速度和噪声性能,它包括Sub-DAC和余量放大器(RA)。MDAC主要有两种结构,电荷翻转型和电荷重分配型,本文设计采用如图4所示的电容翻转型结构[7],并使用了下级板采样技术。以单端(运放的负输入端)为例来分析工作原理如下:在采样相位Φ1时,电容C1~C16下极板接到输入VINP,C17、C18的下极板分别接到参考电压VRP和VRN上;在保持相位Φ2时,C1~C4的下极板与运放的输出端OUTP相连,余下14个电容C5~C18由Sub-ADC输出结果控制其接VRP或者VRN,实现信号的减法运算。当比较器比较结果为1时,其对应采样相位接到正输入信号VINP的电容上极板连接到VRP,采样相位接到负输入信号VINN端连接到VRN;反之,当比较器的比较结果为0时,其对应的采样相位接到正输入信号VINP的电容上极板连接到VRN,采样相位接到负输入信号VINN端连接到VRP。假设Sub-ADC输出的结果中有x个值为1,(14-x)个为0,则运放的正输入端有x个电容接到 VRN,(14-x)个电容接到 VRP;运放的负输入端则相反,有(14-x)个电容接到 VRN,x个电容接到 VRP;并且在不考虑寄生的情况下,在运放的输入端使用电荷守恒,可以得到式(5)、(6):

假设运放的增益为A0,则有:

联立(5)~(7)3式可以得到:

假设所有的电容完全匹配,而且运放增益无穷大,可以得到如图5所示的传输曲线图。

图4 本文所采用的3.5位/级MDAC结构图[7]

图5 本文设计的3.5位/级流水线级传输曲线图

从以上分析可以看出本文采用的3.5位/级的结构有几个显著的优点:(1)在采样相时,对运放的失调电压进行采样,具有消除运放失调的功能;(2)简化了从Sub-ADC到Sub-DAC的编码电路设计,提高了转换速度;(3)更大的反馈系数以及缩放的输出摆幅减小了对运放的要求,提高输出线性度的同时有利于降低功耗。

3.4 余量放大器的设计

本文设计ADC的工作速度高达1 GHz,仅对线性误差进行校正而忽略非线性误差可以在很大程度上简化数字校正算法的复杂度[8]。对于不同结构的运算放大器,其所能达到的增益、带宽、线性程度都是不同的,表1对常用的运放做了一个总结[9]。

表1 各种结构的运放性能比较

综上所述,对于具有数字校准的高达1 GHz采样速度的ADC来说,低增益大带宽的五管运放即可满足要求,还能大大降低电路复杂度及功耗面积。因此我们采用如图6所示的结构,图6中2个电阻是最简单的共模反馈结构,C1和C2是正反馈电容,能够增大运放闭环工作时的反馈系数,降低对运放带宽的要求。

图6 本文所采用的RA电路图

3.5 数字校准

流水线ADC误差的主要来源有热噪声、采样开关的非线性、比较器的失调电压、MDAC增益误差、Sub-DAC的非线性、余量放大器的非线性等。

采样电容取值越大,热噪声影响会越小,而且Sub-DAC的非线性也会很低,但是不利于采样速率的提高,因此可以通过对电容的合理取值来折中。Sub-DAC中由于电容失配引起的非线性也可以通过校准方法来解决,例如文献[8]中提及的前台校准。由采样开关引入的非线性失真本文采用自举采样开关来降低。

本文设计的流水线ADC采用了一种基于随机抖动的后台校正算法[10]来校准线性误差。在图7所示的Sub-DAC基础上在输入端注入随机抖动信号,图7给出单端示意图,即在Sub-DAC中多加一路注入电路,此电路只在PN码注入时有用,余量放大输出表达式右边将多一项:

注入 1(PR=1)传输曲线下移,注入-1(PR=-1)传输曲线上移。需要注意的是,为了防止输出溢出,当差分输入在区间(-VR,-13VR/16)内注入-1,当输入在区间(13VR/16,VR)内注入 1。

图7 带有抖动信号输入的MDAC单端电路示意图

4 仿真结果

本文基于40 nm CMOS混合信号工艺对芯片进行整体仿真,以验证电路的功能及性能。

图8 ADC在输入约455 MHz正弦信号时的动态性能

首先我们验证每一级的功能,在输入斜坡信号时,得到注入-1、0、1时的传输曲线图。确定每一级的功能都没有问题之后,接下来是对整体ADC性能的仿真,在采样频率为1 GHz时,当输入频率分别为455.078 125 MHz、1.486 328 125 GHz时,仿真结果分别如图8和图9所示。同时仿真结果表明,整体电路功耗约为220 mW。

图9 ADC在输入约1.5 GHz正弦信号时的动态性能

可以看到,在输入信号频率为455.078 125 MHz时,SNR是70.09dB,SFDR是82.07dB,ENOB是11.22Bit;当输入信号频率达到1.486 328 125 GHz时,SNR是62.75 dB,SFDR 是 77.98 dB,ENOB 是 10.08 Bit;在高频输入下,采样时钟的抖动和首级流水线级中MDAC和Sub-ADC采样网络的失配愈加严重,导致了SNR的快速下降。通过以上分析可知,本文设计的流水线ADC在1 GHz工作频率下能得到较好的动态性能。

5 结论

本文基于40 nm CMOS工艺设计了一款12 Bit 1 GS/s射频采样的流水线ADC,采用SHA-less、高带宽高线性度的运放、数字校准等技术,并对关键模块以及整体电路进行了仿真。最终仿真表明,本文设计的流水线ADC在1GHz工作频率下能得到较好的动态性能。

[1]William C Black,David A Hodges.Time interleaved converter arrays[J].IEEE Journal of Solid-State Circuits,1980,15(6):1022-1029.

[2]Ashutosh Verma.A 10-Bit 500-MHz 55-mW CMOS ADC[D].Los Angeles:University of California,2009:4.

[3]Zhao Hui.Pipelined ADC Design Methodology[D].Riverside:University of California,2012:28.

[4]Massimo Brandolini,et al.A 5 GS/s 150 mW 10 b SHA-Less Pipelined/SAR Hybrid ADC for Direct-Sampling Systemsin28nmCMOS[J].IEEEJournalofSolid-StateCircuits,2015,50(12):2922-2933.

[5]Young-Mok Jung,Jin Zhe,et al.A SHA-less 10-bit 80MS/s CMOS pipelined ADC[C].IEEE 11 the International Conference on Solid-State and Integrated Circuit Technology,2012:1-3.

[6]Siddharth Devarajan,et al.A 16 b 125 MS/s,385 mW,78.7 dB SNR CMOS pipeline ADC[J].IEEE Journal of Solid-State Circuits,2009,44(12):3305-3312.

[7]邓世杰.14 bit 250 MSPS流水线ADC关键电路设计研究[D].西安:西安电子科技大学,2014:25-29.

[8]Bibhu Datta Sahoo,Behzad Razavi.A 10-b 1-GHz 33-mW CMOS ADC[J].IEEE Journal of Solid-State Circuits,2013,48(6):1442-1452.

[9]Behzad Razavi.Design of analog CMOS integrated circuits[M].Boston:McGraw-Hill,2001:314.

[10]Yun-Shiang Shu,Bang-Sup Song.A 15-bit Linear 20-MS/s Pipelined ADC DigitallyCalibrated With Signal-Dependent Dithering[J].IEEE Journal Solid-State Circuits,2008,43(2):342-350.