安装空间受限的北斗接收机电磁干扰分析和解决方法

薛 雯,卢飞平

(上海电控研究所 上海 200092)

1 引言

北斗接收机的工作波段属于微波波段,传播模式为空间波,卫星到达地面的标准功率只有-133dBm,容易受到各类来自环境和设备内部的电磁干扰。随着电子导航设备小型化,接收机上的射频电磁敏感区与各类数字时钟数字电路这些容易产生电磁干扰的噪声源靠得越来越近,电磁兼容设计显得尤为重要,一个失误可能就会导致整个接收机无法正常工作。

2 问题的提出

一款新研安装空间受限的北斗接收机,其原理框图如图1所示,属于典型的模数混合电路,采用了传统的模拟地数字地分割的方法,通过0Ω电阻进行了单点接地。接收机与天线用长射频线缆对天测试时,定位正常。接收机安装在天线所在的腔体时,接收机与天线之间的空间距离非常近,接收机无法定位,怀疑出现电磁兼容问题。频谱分析仪接上天线测试接收机带内辐射,发现底噪被抬高。进一步测试发现接收机地、电源等处都串扰进了62MHz时钟的谐波,其21次谐波正好落在接收机工作频段内,这些谐波辐射到空间,被距离很近的天线接收,捕获灵敏度严重下降,接收机无法定位。

图1 北斗接收机原理框图

3 电磁干扰理论分析

3.1 噪声源分析

特定噪声源有4类:(1)单个网络的信号完整性;(2)两个或多个网络间的串扰;(3)电源和地分配中的轨道塌陷;(4)来自整个系统的电磁干扰和辐射[1]。

时钟信号单个网络的信号完整性问题以及和其他网络之间的串扰问题都可能将时钟变成噪声源。

3.2 时钟指标分析

时钟指标一般包括相位噪声、谐波抑制、杂散抑制等[2]。

时钟频率源锁相环内部的环路滤波后的输出信号总是或多或少的包含有鉴相频率泄漏分量,此泄漏分量加到压控振荡器上就会对其信号调制,形成杂散[3]。

时钟输出抖动也是影响时钟杂散的关键因素。相位噪声是信号在频域的度量。在时域,与之对应的是时钟抖动,为了不影响时钟频率源,参考时钟尽量无噪声,仅具有可能最低的时钟抖动。

环路带宽内的相位噪声,可用公式(1)表示。

F(all)=F(1)+10logf(ref)+20logN (1)

其中F(all)是总的带内噪声基底,F(1)是芯片鉴相器的归一化噪声,f(ref)是鉴相频率,所以F(1)+10logf(ref)就是鉴相器工作在鉴相频率下的噪声,N是分频比,鉴相频率越高分频比越小,所以,总的来说,鉴相频率越高,带内相位噪声越好,前提是参考时钟的相位噪声不会影响到噪声基底,也就是说提高时钟频率源的鉴相频率有利于降低相位噪声。

综上所述,可以从噪声源头上去抑制大部分杂散,也可以选择时钟输出抖动较小的晶振和提高鉴相频率减少时钟杂散。

3.3 时钟信号完整性分析

为了解决EMI问题,除了需要控制时钟杂散,还需考虑时钟信号完整性,62M输出引脚引出的线条与其他两个芯片相连,连接这3个引脚的每条走线就可以看成属于同一个网络。网络不仅包含信号路径,还包含信号电路的返回路径[1]。在高频数字系统中,高频信号以参考面作返回路径,即回流路径,如果参考面不连续,信号跨分割,就会带来诸多的问题,如EMI和串扰等问题。根据法拉第定律,该回路会产生变化磁场,变化磁场就会产生电场,所以高频信号EMI是与回路面积密切相关的,如果想减少EMI,就必须把回路面积减小。本项目问题设计中,采用了传统的模拟地数字地分割的方法,通过0Ω电阻进行了单点接地,导致62MHz时钟信号跨区,信号环路增大,增加了接收机EMI。

4 EMI实测情况分析

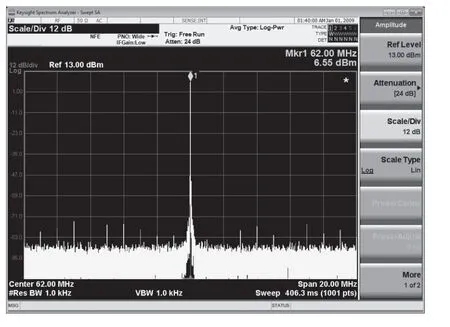

当出现EMI问题时,首先对射频电路进行了排查,断开AD芯片和基带芯片,测试了射频电路在北斗接收机频段内的带内噪声情况(测试频点为B3,中心频率为1268.52MHz,带宽为±10MHz),未扫描到任何噪声抬起的状态。其次对AD芯片和基带芯片进行了测试,发现只要板子的AD芯片和基带芯片工作,板子的底噪就被抬高,带内干扰谐波非常严重。进一步测试发现,只要62MHz时钟被接入到AD芯片和基带芯片中,就会出现大量的干扰谐波(如图2所示),并且62MHz时钟由于跨地传输的原因,通过接地串扰到整个板子,故将问题锁定在62MHz时钟上。

北斗接收机上62MHz时钟信号频谱和相位噪声测试结果如图3-4所示。从图3可以看出,62MHz时钟锁相环有2MHz的鉴相频率泄露非常严重,相对功率非常大。在接收机设计中,这些杂散信号与其他干扰信号相混频有可能产生有用信号频率,从而降低接收机的灵敏度。

图2 北斗B3频点带内干扰谐波

图3 北斗接收机62M时钟频谱

图4 62M时钟的相位噪声

5 解决EMI问题的措施

5.1 时钟电路优化

62MHz时钟是时钟频率源锁相环生成。为了解决62MHz时钟的杂散问题,采取了以下两个措施优化时钟电路。

5.1.1 降低相位噪声

10MHz参考时钟为时钟频率源锁相环参考输入频率,该参考时钟由外部晶振提供,优选了相位噪声较好,即输出时钟抖动较小的温补压控晶振。并将时钟频率源的鉴相频率从2MHz调整到10MHz。

EMI辐射、电源噪声、同步切换噪声等对时钟相位噪声的影响是有边界的,可以通过电路设计优化把噪声源消除或大幅降低。所以本文除了优化参考时钟的指标外,还采取了电路优化措施,将时钟的供电电路和其他模拟供电进行分开供电,并在电源管脚处依次放置0.1uF,0.01uF,100pF的电容,电源输入处增加了磁珠滤波,时钟锁相环的供电口同样增加了退耦电容,最大限度滤除电源线上的干扰。大电容的等效串联电阻往往较大,而且对高频噪声的滤波效果较差,高频噪声的抑制需要用小容值的电容。

5.1.2 抑制鉴相频率泄露

除了优化参考时钟和供电电路外,还外加了鉴相频率抑制滤波器。在不破坏锁相环路稳定性的前提下,二阶低通有源滤波器对鉴相泄漏及其谐波分量的抑制作用最好[3]。本文在VCO压控电压口处设计了二阶低通有源滤波器。

通过以上优化设计及增加二阶低通滤波器后,改善后的62M时钟的鉴相泄露抑制比增加显著,且相位噪声也有了改善,如图5-6所示。

图5 改善后的62M时钟鉴相泄露明显被抑制

图6 改善后的62M相位噪声

5.2 时钟信号完整性优化

由于时钟信号进行了跨区域走线,导致接地平面上被串扰进了62M时钟,这样整个板子都可以测到幅度不等的时钟信号。同时两层之间的接地噪声直接添加到时钟信号,并产生过度抖动。抖动可造成信噪比降低,还会产生干扰谐波。

为了优化时钟串扰问题,本文对PCB板进行了信号完整性分析,摒弃了传统单点接地的思想,改用统一地,避免由于地平面分割造成的参考平面割裂,如果时钟导线下方的接地层上有割裂,接地层返回电流必须环绕裂缝流动。这会导致电路电感增加,而且电路也更容易受到外部场的影响。模拟电路和数字电路划区布局,但使用“统一地”,形成完整的接地平面,仅在射频部分人工割开一部分铜皮,保护敏感的射频部分不受其他数字电路产生的噪声干扰。当然,没有任何一种接地方法能始终保证最佳性能。本文根据所考虑的特定混合信号器件特性提出了接地思路,仅供参考。

6 结语

由于手持设备等小型化需求,天线往往和接收机无法进行空间隔离,如何让接收机辐射的噪声不要影响到带内的信号,确保接收机能正常捕获从卫星上发出的极其微弱的导航信号,这就需要我们花大量的精力去解决电磁干扰问题。本文从出现EMI问题故障的接收机着手,对噪声源进行了定性分析,将噪声源定位于时钟信号,并从理论上对时钟杂散及时钟信号完整性进行了分析,提出了优化时钟电路的方案,并提出了基于信号完整性分析的“统一地”接地方案,有效地解决了因EMI导致的接收机灵敏度下降的问题。